文章目录

前言

Lattice FPGA在市场上的份额相对较小,相关的开发经验分享也并不多。多数资料停留在基础操作的介绍,缺乏深入的实战总结。而在实际项目中,我逐渐体会到 Lattice 在 SerDes + 低功耗 + 高性价比 方面的独特优势。基于这些经验,我希望把自己的Serdes实战过程记录下来,侧重通过类比的方式达到让读者理解的目的。与大家共同交流学习,一起成长进步。

1. 什么是Serdes?

SerDes 是 Serializer/Deserializer 的缩写,一般译为串并转换器。它是一种高速接口电路,主要功能是串并转换。(概念)在FPGA里面 ,SerDes 通常是 硬核(硬件资源),比如 Xilinx 的 GTP/GTY,Intel 的 H-Tile,Lattice 的PCS块。这个硬核包括一些通用的部分,比如PLL(锁相环)用来产生高速串行时钟、还有CDR(Clock Data Recovery)从接收到的数据流里恢复时钟、还有8b/10b 编码单元,保证直流平衡和时钟提取。通用的部分基本一致,但有些细节不同厂商.还是有些差异。与xilinx serdes相比,IP的形式,底层的结构,用户的信号,约定俗称的叫法上都有些区别。

从更为宽泛的角度, SerDes 是把宽并行数据转成高速串行数据并可靠传输的核心技术,广泛应用于各种高速接口和通信系统。数据传输技术在并行传输上遇到引脚资源占用较多,数据到达时间难以对齐,并行线容易收到干扰等困难,最快的并行传输,源同步模型可能就是LVDS传输,也只有不到1Gbps的传输速率。随着技术发展,渐渐从源同步发展到了自同步模型,高速串行技术迎来崛起。所谓自同步就是不再有单独的时钟线,而是在数据中添加时钟信息,接收端采用CDR技术恢复,也就是Serdes技术。

从更贴切的工作场景看,项目方案讨论时,提到的"走Serdes"即通过FPGA的Serdes硬核传输数据。在xilinx中,GT称之为串行收发器,通常等同于Serdes。而在Lattice中,更愿意把PCS与Serdes等同。

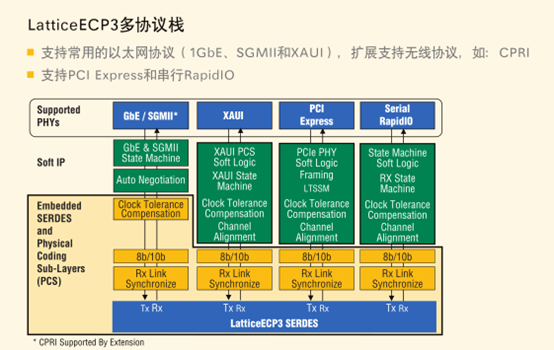

2. ECP3的Serdes协议栈

如图所示,LatticeECP3™ FPGA系列结合了高性能FPGA结构、高性能I/O和多达16个通道带有相应的物理编码子层(Physical Coding Sublayer,PCS)逻辑的嵌入式SERDES,PCS 逻辑可配置用于支持很多业界标准的、高速串行数据传输协议。此外,PCS 还提供旁路模式 (bypass mode),允许使用 8 位或 10 位接口将 SERDES 直接连接到 FPGA 逻辑。

3.专题内容综述

一是一些概念的梳理明确,例如上面从三个角度介绍了准确的Serdes、高速串行技术Serdes以及口语化场景中的Serdes,后面会介绍一些概念之间的关联,例如Serdes与光口,Serdes与8b/10b等,这部分内容自然的穿插在各个章节。二是,外围的光纤和光模块的知识;Serdes是FPGA硬核,与外部器件和其他设备的连接需要一定的物理介质,光纤、背板、连接器、金手指等都是常见的方式,本次项目开发基于光纤,所以着重介绍。内容包括光模块的名称的含义,波长要匹配光模块光纤,光纤是什么接口,是否多模,光纤的颜色都有讲究,还有原理图的设计是有规范的。三是,Serdes底层的原理结构,例如8b/10b编码技术, serdes底层组成各部分的作用,还有Serdes的时钟、复位等。四是,实战的应用层面,例如复位代码结构,如何利用自回环,如何利用寄存器的信息帮助调试等。

4.参考资料的整理

第一部分(本文所附资源中)是可以从官网下载到的文件做了梳理,①ECP3相关的手册,数据手册,sysIO,sysCONFIG等,②PCS相关的资料包括中英文手册各一份,一份SFP的Specification③一个Reset Sequence的代码。第二部分提供付费源码供参考,包括两份官方Demo,其余都是自己写的包括nearloop近端环回例程,FarLoop远端环回例程,SelfLoop两个板子一收一发的例程,添加寄存器的例程等。

5.传送门

|-----|

| END |

📡文章原创,首发于CSDN论坛。

📡欢迎点赞♥♥收藏⭐⭐打赏💵💵!

📡欢迎评论区或私信指出错误💉,提出宝贵意见或疑问😱。