引言

CPU南北桥的发展史

CPU南北桥架构是计算机发展历史中的重要里程碑,它解决了早期计算机总线架构的性能瓶颈问题,为现代高性能计算奠定了基础。本文将详细介绍CPU南北桥的发展历程,以及其如何演变为现代高度集成的芯片组架构。

我是 SharkChili,Java 开发者,Java Guide 开源项目维护者。欢迎关注我的公众号:写代码的SharkChili,也欢迎您了解我的开源项目 mini-redis:github.com/shark-ctrl/...

总线

在计算机发展初期,硬件设备相对较少,CPU主要与内存进行交互。为了减轻CPU的负担,将虚拟地址转换为实际物理地址并进行读写操作都由内存控制器完成。

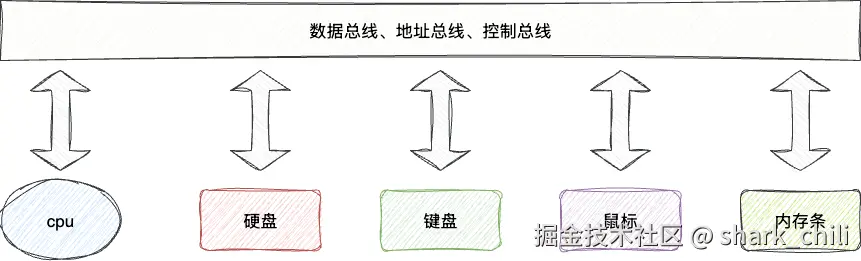

在冯·诺依曼体系的计算机设计理念下,计算机引入了键盘、鼠标、显示器、硬盘等设备协同工作。为了避免多设备协同线路设计的复杂性,所有设备都连接在一条总线上:

为保证多设备总线资源竞争的并发安全,设计者引入了总线仲裁机制,由总线控制器统一管理总线资源的申请。有了总线仲裁机制后,所有设备在进行通信时都需要先申请总线资源,获得许可后才能进行通信操作。

南北桥架构的诞生

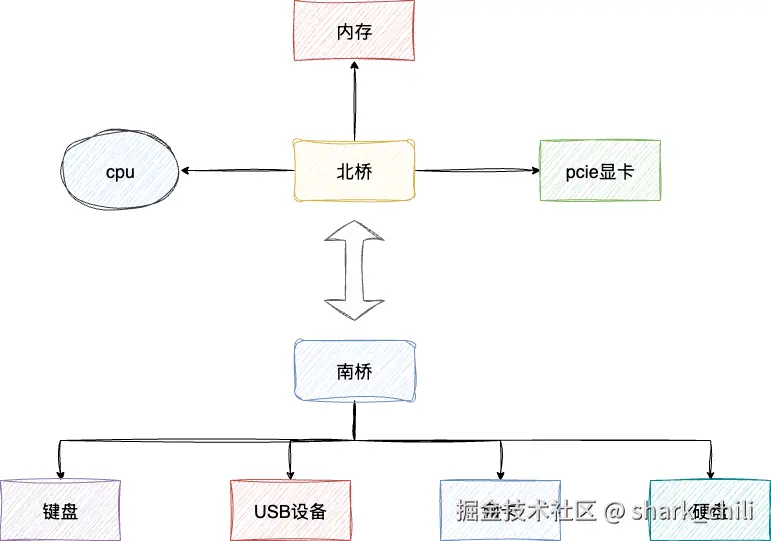

随着CPU频率的提升以及更多硬件设备的引入,原有总线架构的局限性逐渐显现:单位时间内只有一个设备可以使用总线资源,整个计算机的交互效率表现非常差,CPU也未能完全调度和发挥计算机的所有性能,甚至会出现因某个执行效率较慢的设备占用总线而拖累整个系统的情况。为了解决这个问题,设计者考虑到分散硬件竞争压力,提出了南北桥的概念。南北桥虽然称为"桥",本质上是两个芯片,分别位于主板的上部和下部位置:

- 北桥集成了内存控制器、PCI/AGP总线控制器等,负责连接CPU、内存、显卡等需要高速运行的设备

- 南桥负责处理键盘、网卡、硬盘等相对低速的I/O设备

于是就有了下面这样的多设备交互架构雏形:

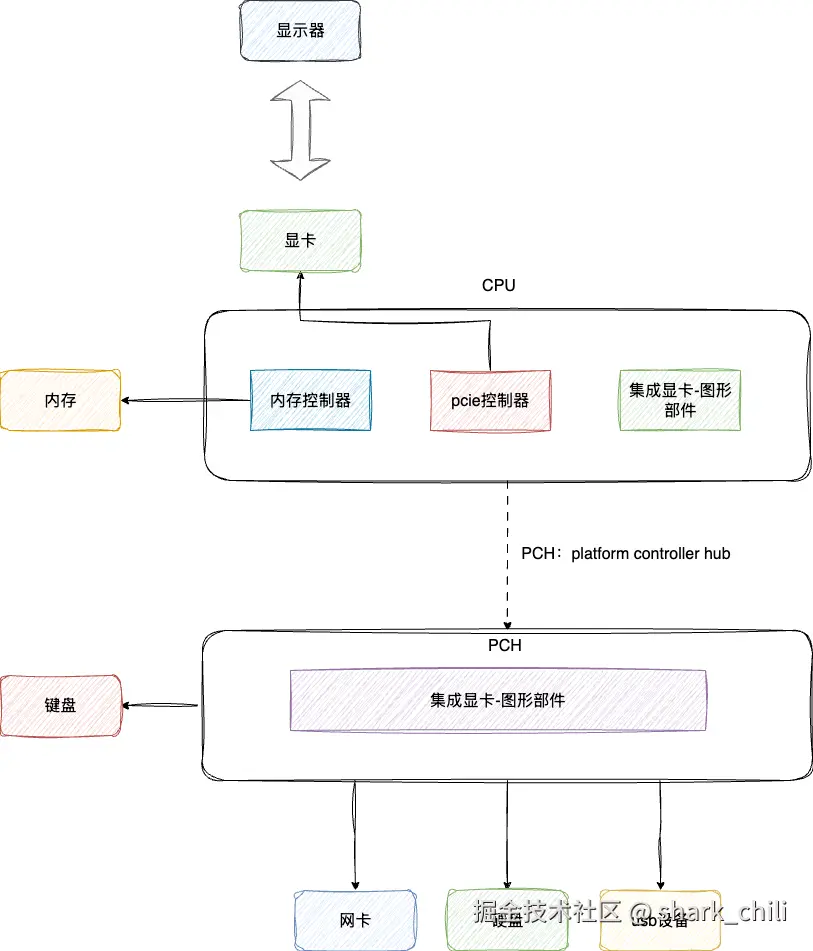

集成化发展与北桥消失

随着CPU和内存通信变得越来越频繁,为了进一步提高效率,CPU厂商开始将内存控制器集成到CPU内部。随着技术的发展,PCIe控制器和图形控制器也逐步集成到CPU中。这样一来,内存和显卡的访问不再需要经过北桥,北桥的概念自此逐渐退出历史舞台。

由于只剩下南桥芯片,也就不再区分南北桥了。对应的架构变为下面这样,可以看到内存控制器和显卡(PCIe控制器)都集成到CPU内部。对外的硬件设备在Intel新架构中通过PCH(Platform Controller Hub)取代原有的南桥芯片,负责进行I/O操作和连接外部硬件设备。

重要技术里程碑

在CPU南北桥发展过程中,有几个重要的技术里程碑值得关注:

- 1990年代初:Intel 8xx系列芯片组首次引入南北桥架构

- 2003年:AMD Athlon 64首次将内存控制器集成到CPU中,标志着北桥概念开始弱化

- 2008年:Intel Nehalem架构引入QuickPath Interconnect (QPI),替代传统的前端总线(FSB)

- 2008年后:Intel开始使用PCH(Platform Controller Hub)替代传统的南桥芯片

主要厂商技术路径差异

不同厂商在CPU架构发展上采用了不同的技术路径:

-

Intel发展历程:

- FSB (Front Side Bus):早期CPU与北桥之间的主要通信总线

- QPI (QuickPath Interconnect):2008年引入,替代FSB,提供点对点连接

- UPI (Ultra Path Interconnect):Skylake-SP及以后使用的高速互连技术

-

AMD发展历程:

- HyperTransport:从AMD K8开始使用,连接CPU与北桥

- Infinity Fabric:Zen架构使用的统一互连架构

关键技术概念

- FSB (Front Side Bus) :Intel早期CPU与北桥之间的主要通信总线,所有内存访问都必须通过FSB,成为性能瓶颈

- DMI (Direct Media Interface) :Intel用于连接CPU与PCH的串行连接技术,替代了传统的PCI总线连接方式

- QPI (QuickPath Interconnect) :Intel的点对点高速互连技术,支持多条链路并行传输

- HyperTransport:AMD的高速低延迟互连技术,支持全双工通信

现代发展趋势

现代CPU架构继续朝着高度集成化方向发展:

- Chiplet设计:AMD的Zen 2+、Intel的Foveros 3D封装技术,通过先进封装技术实现模块化设计

- 新兴互连技术:CXL (Compute Express Link)用于加速器与CPU的高速互连,PCIe 5.0/6.0提供更高带宽的I/O互连

小结

本文深入讲解了计算机发展初期CPU和内存、硬盘等硬件设备如何采用总线仲裁等方式申请总线资源实现硬件之间的通信。后续因性能瓶颈而提出南北桥的概念,这一设计理念通过分散管理高速设备和低速设备,使得计算机整体处理效率显著提升。由于CPU强依赖于内存访问,所以将北桥的内存控制器和显卡控制器逐步集成到CPU中,北桥概念随之消失,芯片组发展为高度集成的架构。

我是 SharkChili,Java 开发者,Java Guide 开源项目维护者。欢迎关注我的公众号:写代码的SharkChili,也欢迎您了解我的开源项目 mini-redis:github.com/shark-ctrl/...

参考

《趣话计算机底层技术》