2.1 总体方案设计流程

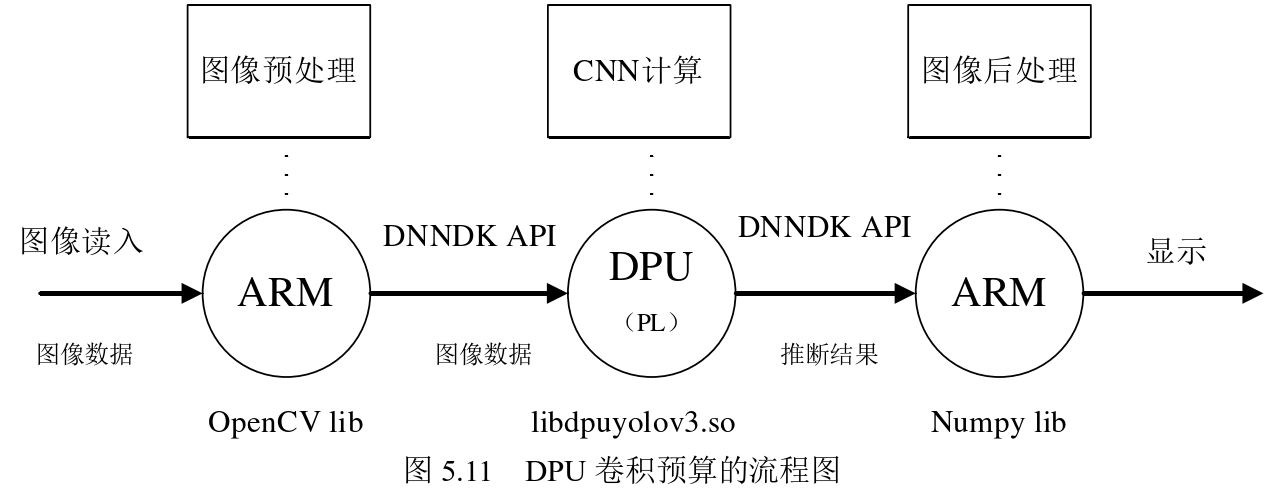

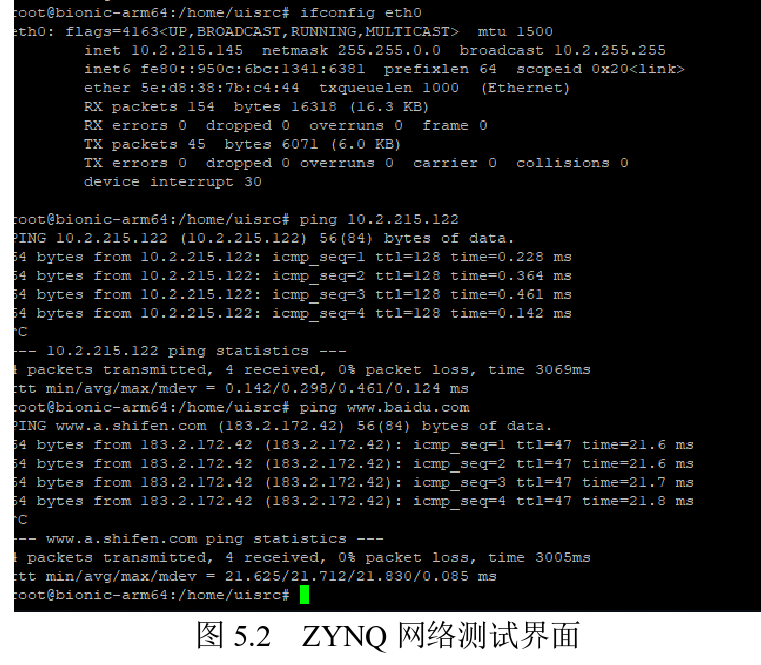

本文研究的是监控系统,因此需要图像采集,系统应能接入摄像头或其他图像传感 器,实时采集图像数据。其次对FPGA进行逻辑设计,实现实时的图像预处理[ 27-28],包 括去噪、高斯滤波和直方图均衡调整等,以提高后续处理的准确性。为了满足系统的可 拓展性,在ARM上移植Linux操作系统[ 29-30],配置以太网连接,方便拓展外设。为了 实现硬件加速,调用Xilinx的DPU模块,提高图像处理的效率和性能。其次,系统应 具备长时间稳定的能力。图2.1为总体方案的原理图。 2.2 监控系统硬件设计

2.2 监控系统硬件设计

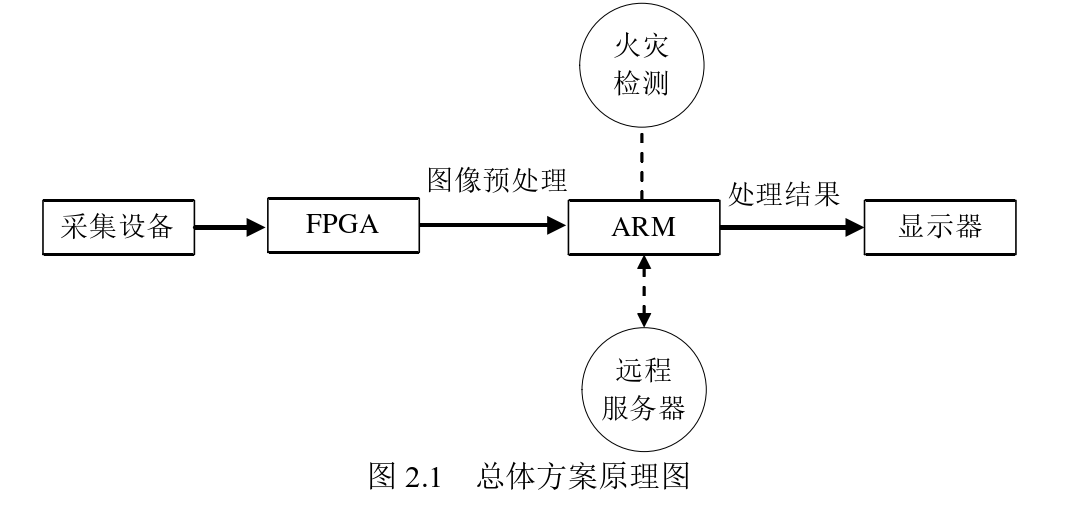

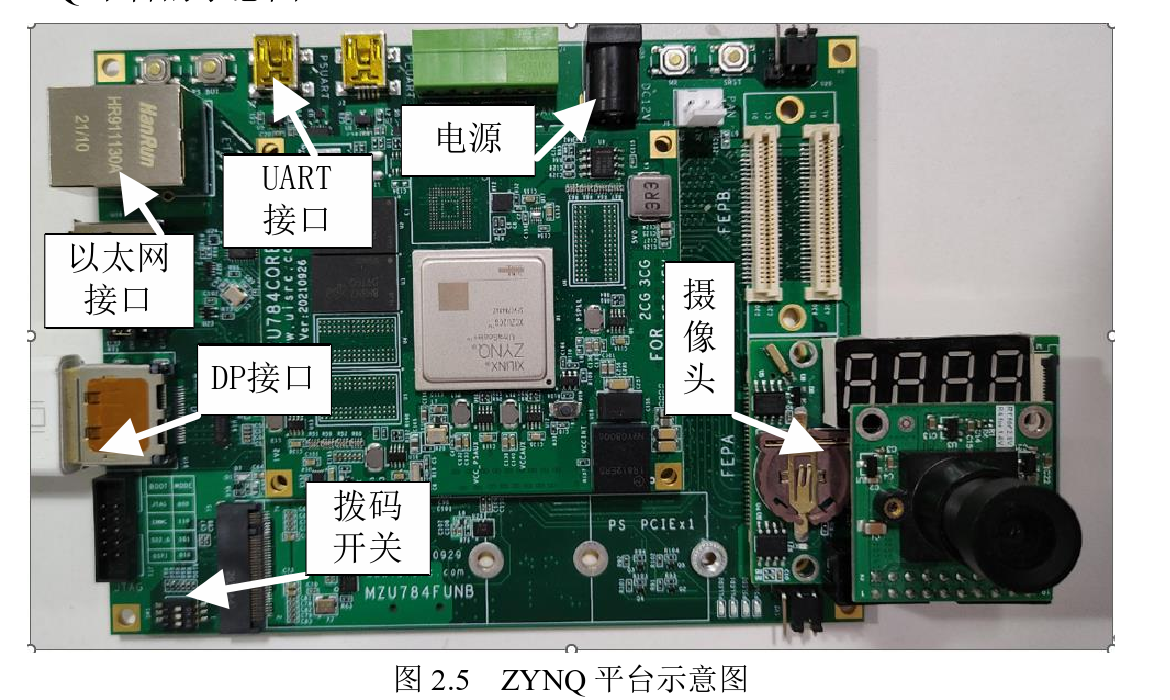

本系统的硬件设计包括电路设计、FPGA的逻辑设计、以及PS端的配置。其中PS 端连接SD卡、UART接口、DP接口和以太网接口,在PL中通过逻辑设计自定义IP 核。图2.2为Zynq的硬件架构图。

2.3 监控系统软件设计

2.3 监控系统软件设计

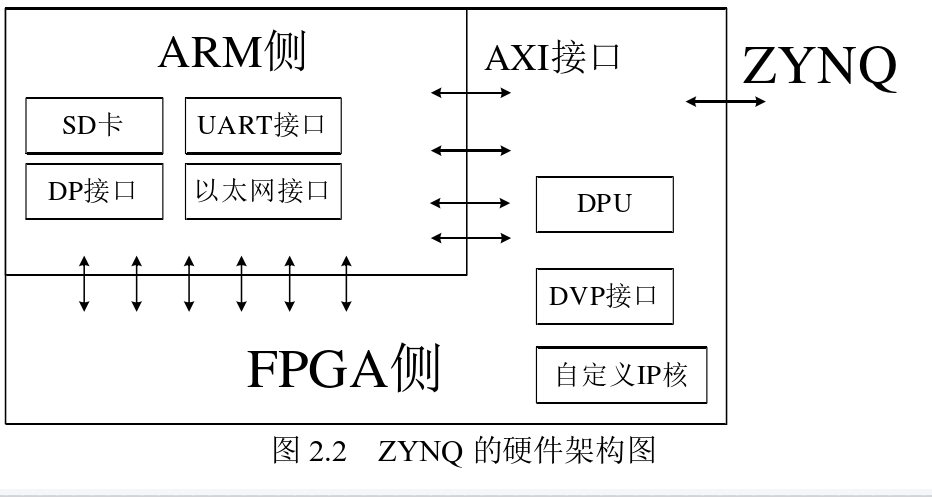

在软件设计中,需要在ARM侧移植Linux,编写摄像头的驱动程序、VDMA的驱

2.4 ZYNQ平台介绍 2.4.1 ZYNQ的开发流程

2.4 ZYNQ平台介绍 2.4.1 ZYNQ的开发流程

在ZYNQ系统级芯片(SoC)的开发流程中,集成了软件与硬件协同设计的理念, 以实现高效的系统性能和功能优化。使用Xilinx套件进行开发,具体包括Vivado、Vitis 软件。图2.4直观表明的Xilinx开发工具的流程。

5.3.2 网络模型训练

一般模型的准确率随着训练次数增大而增大,不少训练次数下准确率波动比较大, 本设计采用了半监督学习的仿真提升识别效果。将前50轮的产生的最佳模型保存起来, 替代初始化模型作为第二轮的初始化模型,可以发现准确率相对稳定。图5.10为三种不 同模型的损失率与准确率变化曲线。 5.3.2 网络模型训练

5.3.2 网络模型训练

一般模型的准确率随着训练次数增大而增大,不少训练次数下准确率波动比较大, 本设计采用了半监督学习的仿真提升识别效果。将前50轮的产生的最佳模型保存起来, 替代初始化模型作为第二轮的初始化模型,可以发现准确率相对稳定。图5.10为三种不 同模型的损失率与准确率变化曲线。

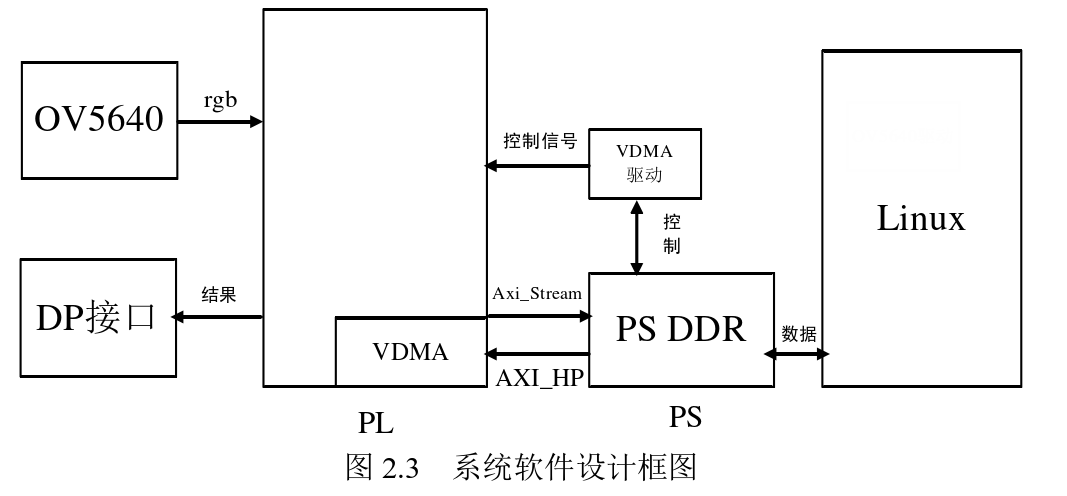

.3.3 DPU加速

Xilinx的专用神经网络单元DPU模块[ 60-62],可以高效地进行运算,特别是卷积模 块中,可以为神经网络模块提升更高的速度。在实际的操作中,在PS端的Linux系统 上,调用dpu的ip进行神经网络的计算。图5.11为DPU卷积预算的流程图。