打工人日报#20250928

本来以为节前可以好好在办公室写代码,想不到还是到南京出差。

知识点

流水灯

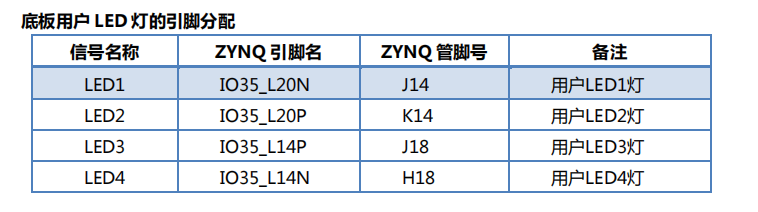

开发板的 PL 部分连接了 4 个红色的用户 LED 灯,LED 灯顺序点亮并熄灭,循环往复产生流水灯的效果

当连接用户 LED 灯的 IO 电压为高时,用户 LED 灯熄灭,当连接 IO 电压为低时,用户 LED 会被点亮。

模块设计

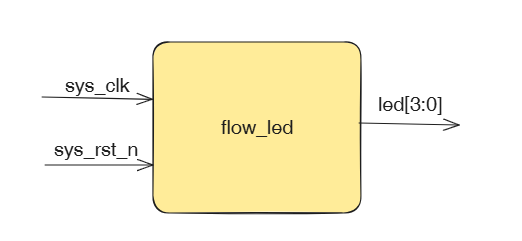

模块命名为 flow_led,灯流水的间隔时间为 0.5s,间隔时间的控制需要通过计数器来实现,即通过计数器来实现计时的功能,因此本次实验需要用

到系统时钟和系统复位;

模块框图如下图所示:

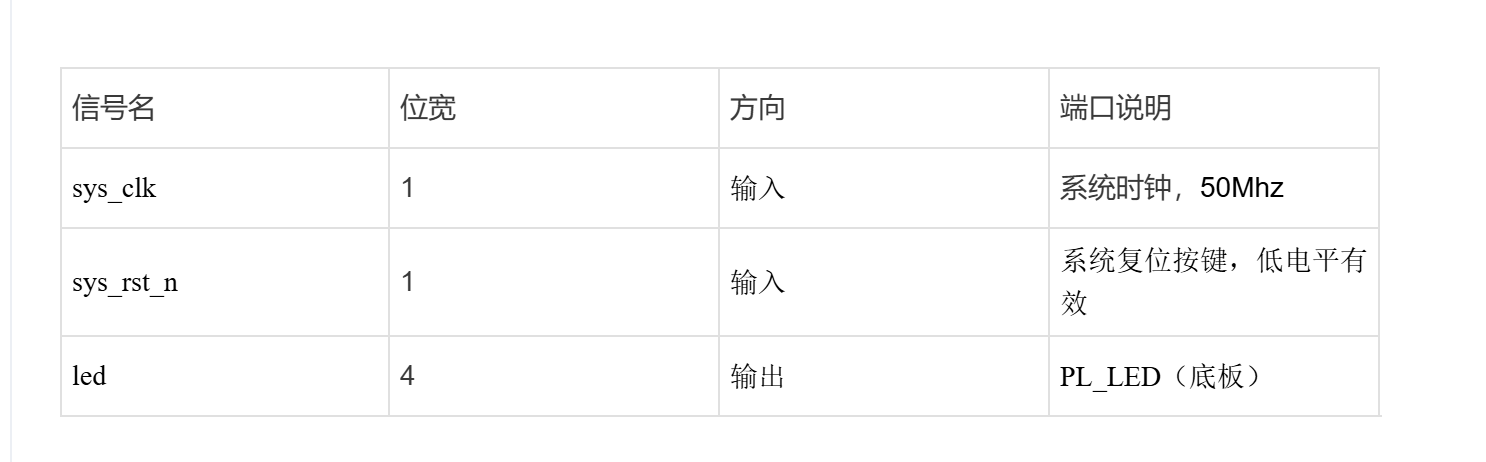

模块端口与功能描述

绘制波形图

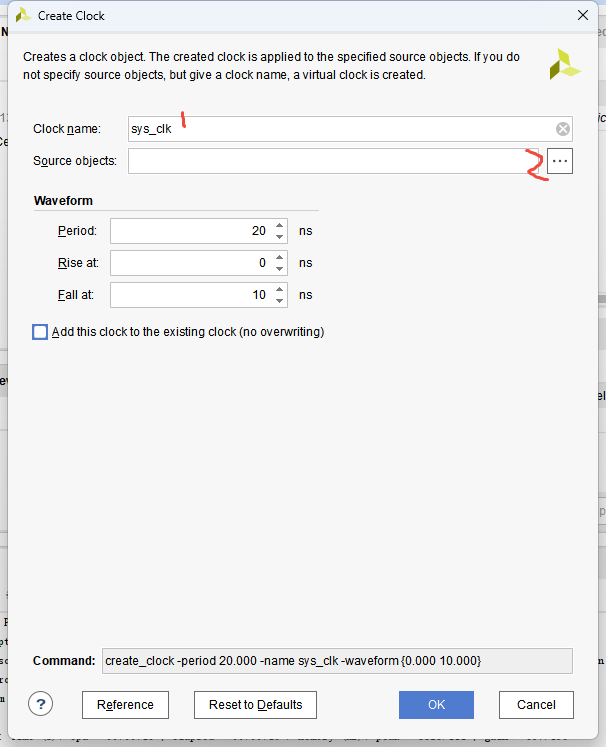

系统时钟 sys_clk 的时钟周期为 20ns(对应开发板板载的晶振频率为 50Mhz),计数器计时 0.5s 需要

0.5s/20ns=500000000ns/20ns = 25000000 个时钟周期,由于计数器是从 0 开始计数,所以计数器最大计数到

25000000-1,刚好是 0.5s

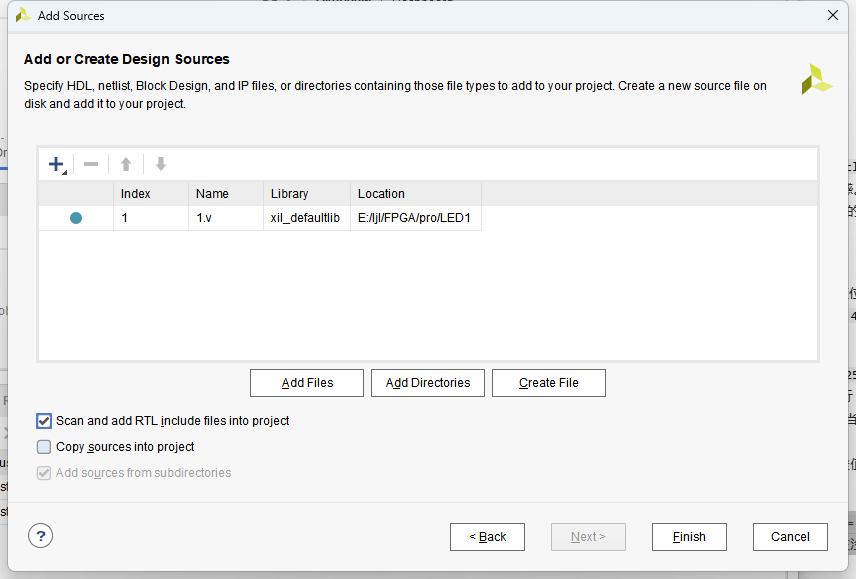

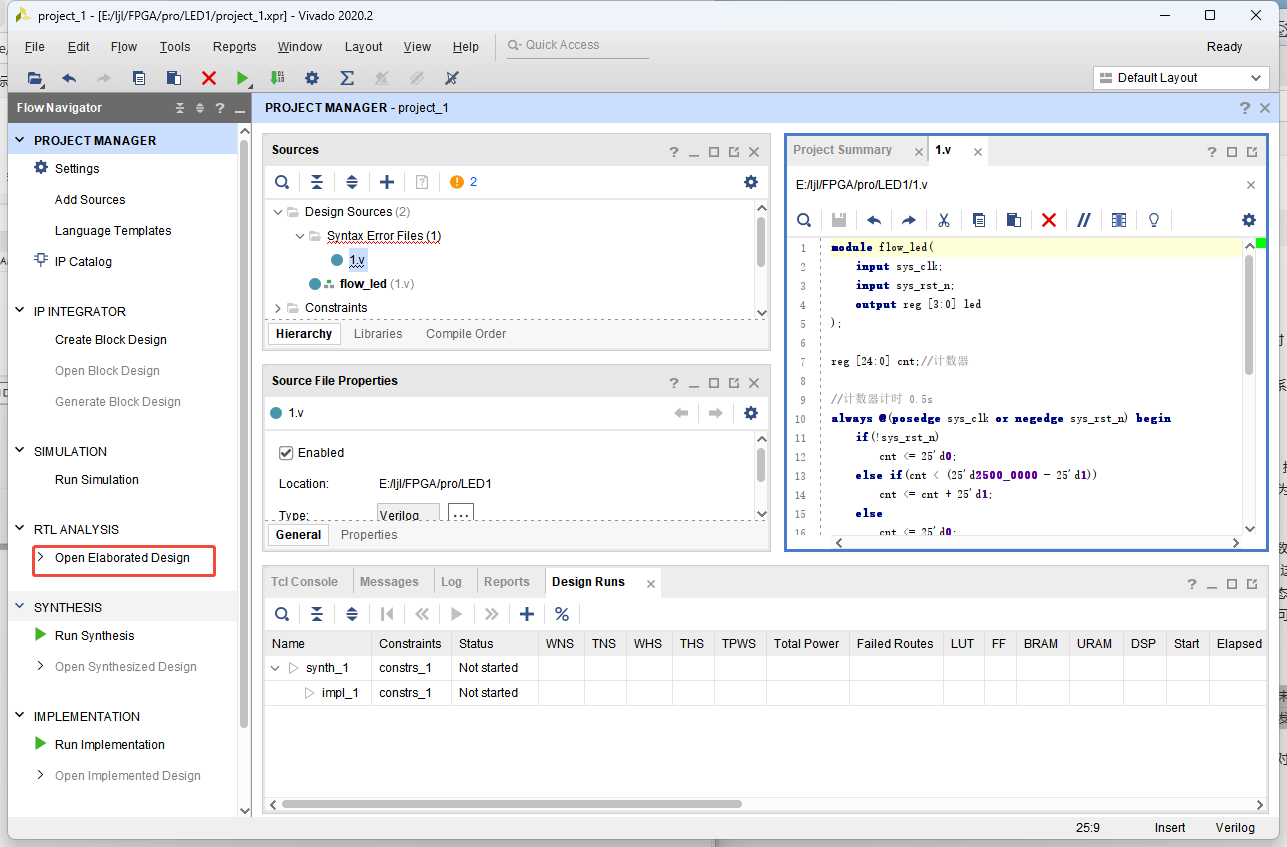

flow_led.v

module flow_led(

input sys_clk,

input sys_rst_n,

output reg [3:0] led

);

reg [24:0] cnt;

// 计数器部分

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

// 复位时,计数器清零

cnt <= 25'd0;

else if(cnt < (25'd2500_0000 - 25'd1))

// 未达到最大计数值时,计数器递增

cnt <= cnt + 25'd1;

else

// 达到最大计数值,计数器归零

cnt <= 25'd0;

end

// LED控制部分

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

// 复位时,初始化led为4'b1101

led <= 4'b1101;

else if (cnt == (25'd2500_0000 - 25'd1))

// 当cnt达到指定值时,led循环右移

led <= {led[0], led[3:1]};

else

// 其他情况下,led保持当前状态

led <= led;

end

endmodule

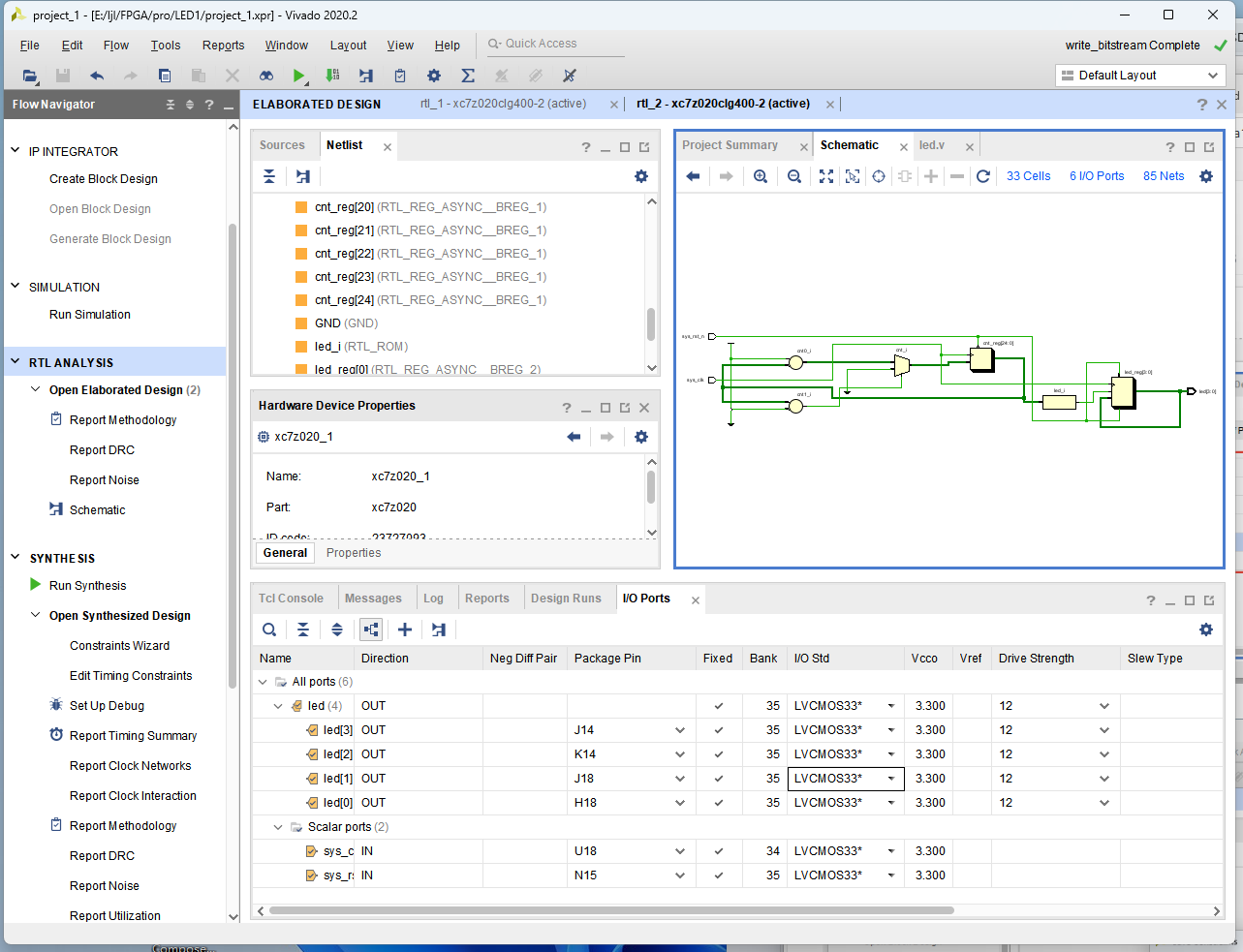

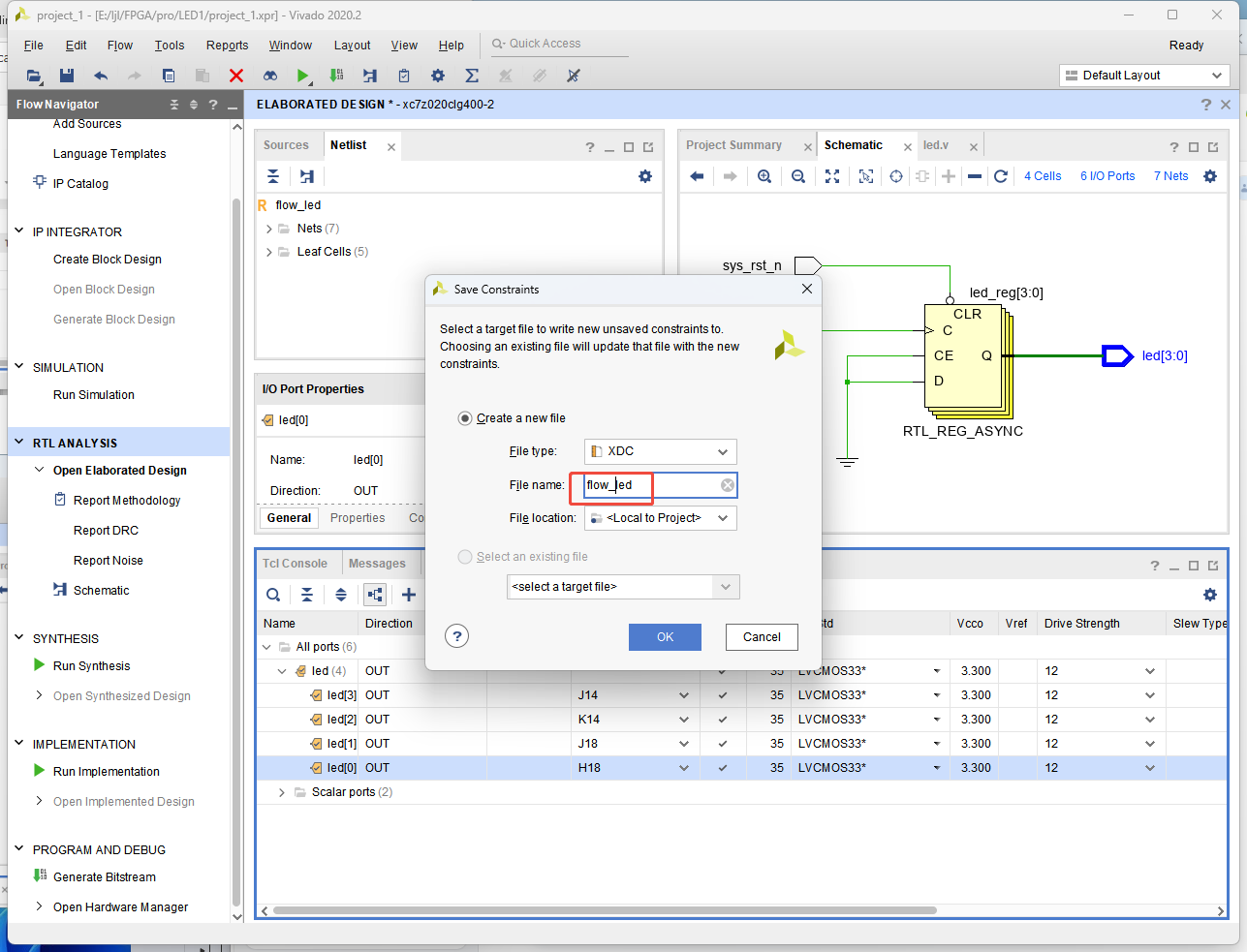

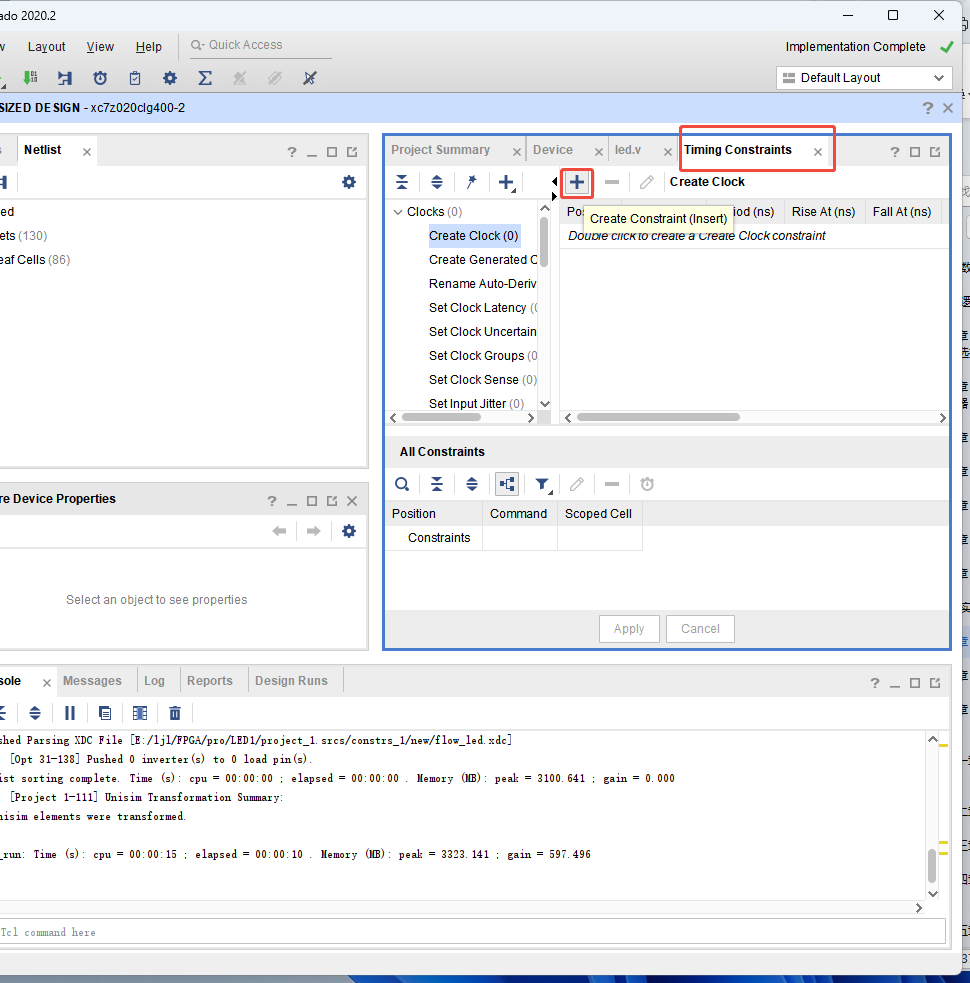

添加约束

保存

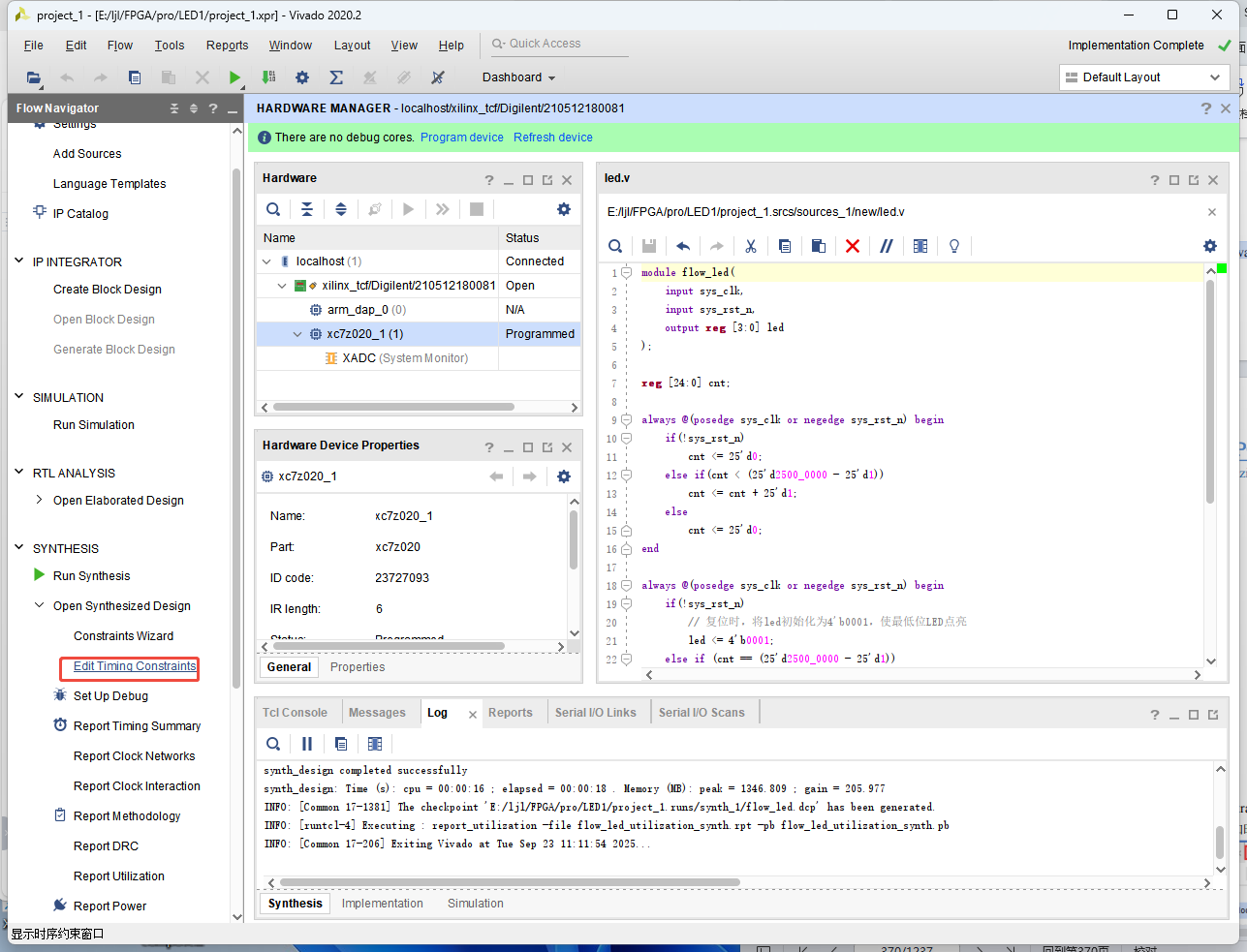

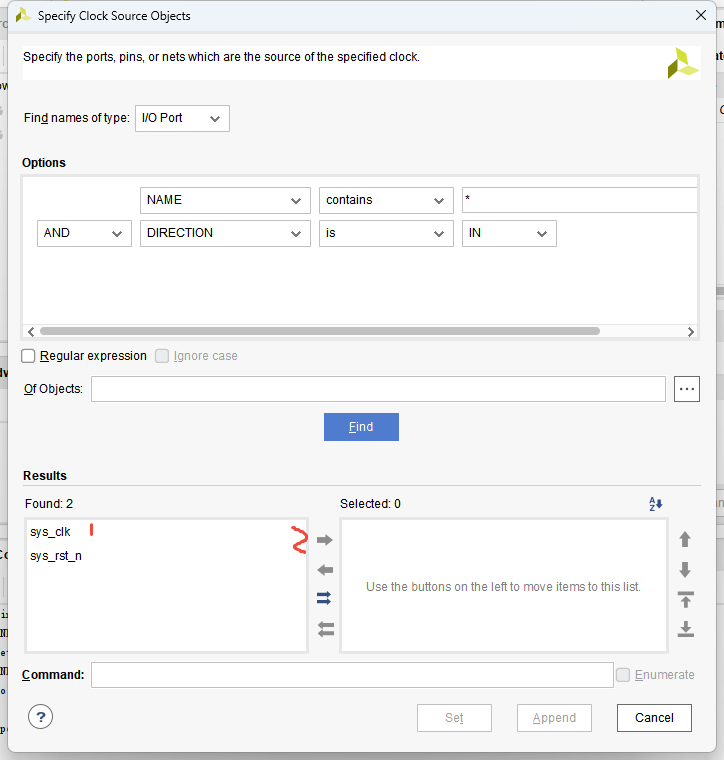

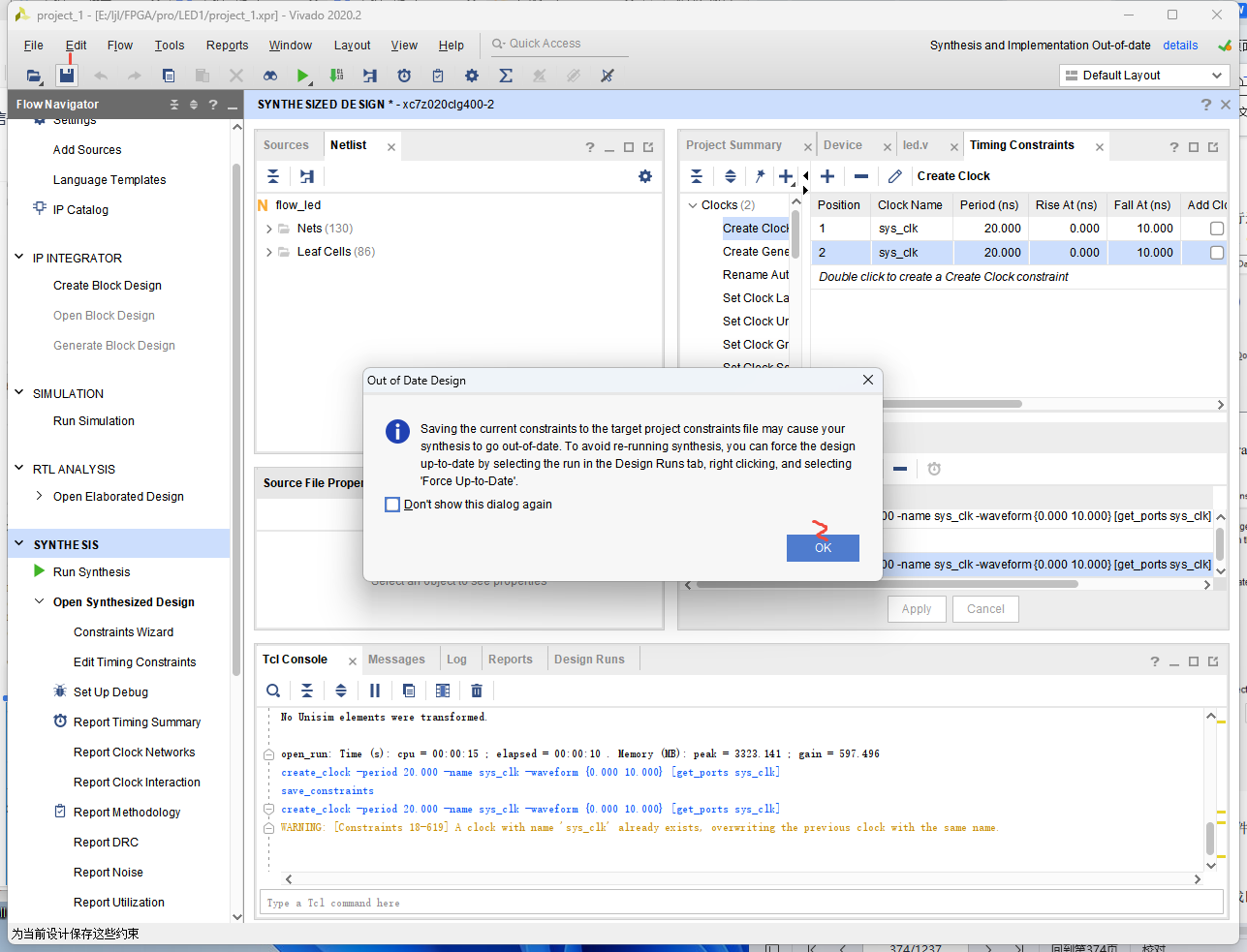

添加时序约束

点击 Vivado 左侧"Flow Navigator"窗口下的"Edit Timing Constraints"按钮

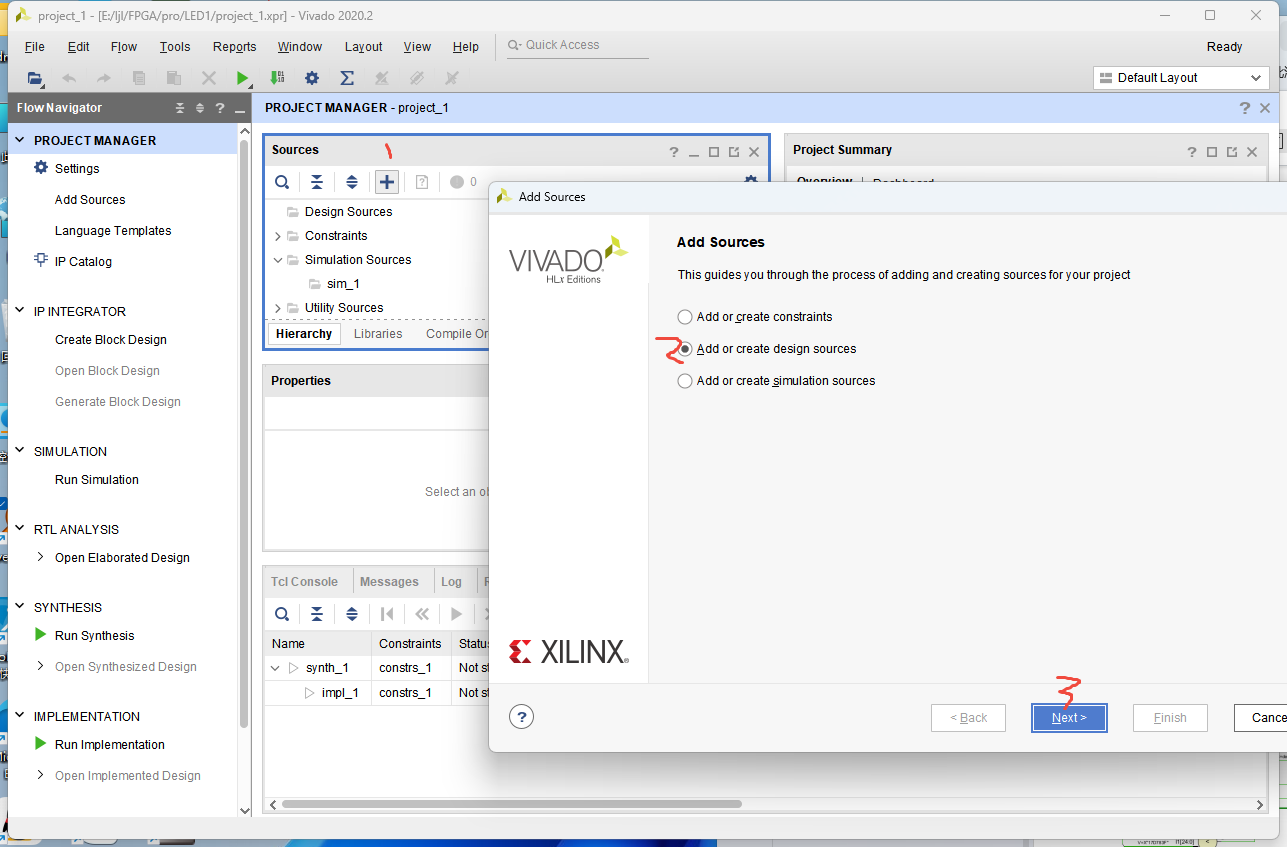

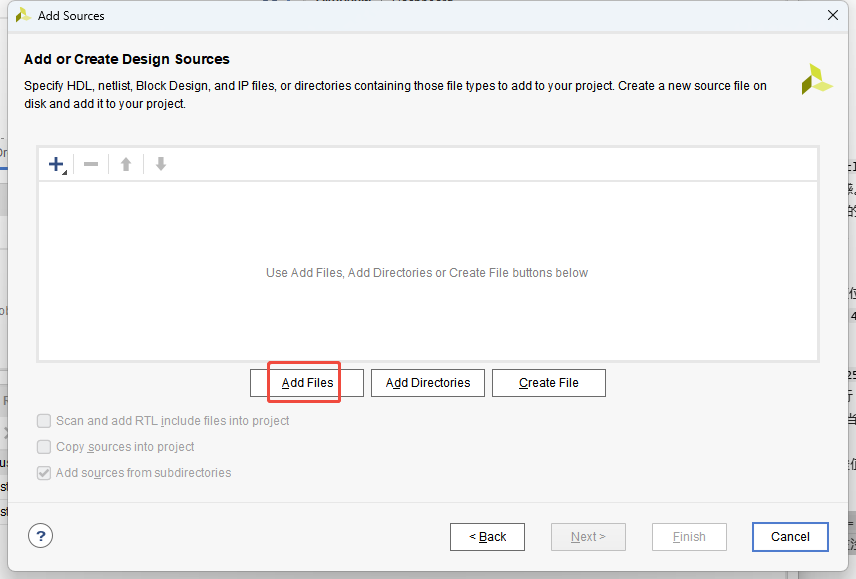

FPGA 开发流程

需求分析

系统设计

硬件选型

绘制系统框图

绘制波形图

编写 RTL 代码

软件仿真

新建工程 Create Project

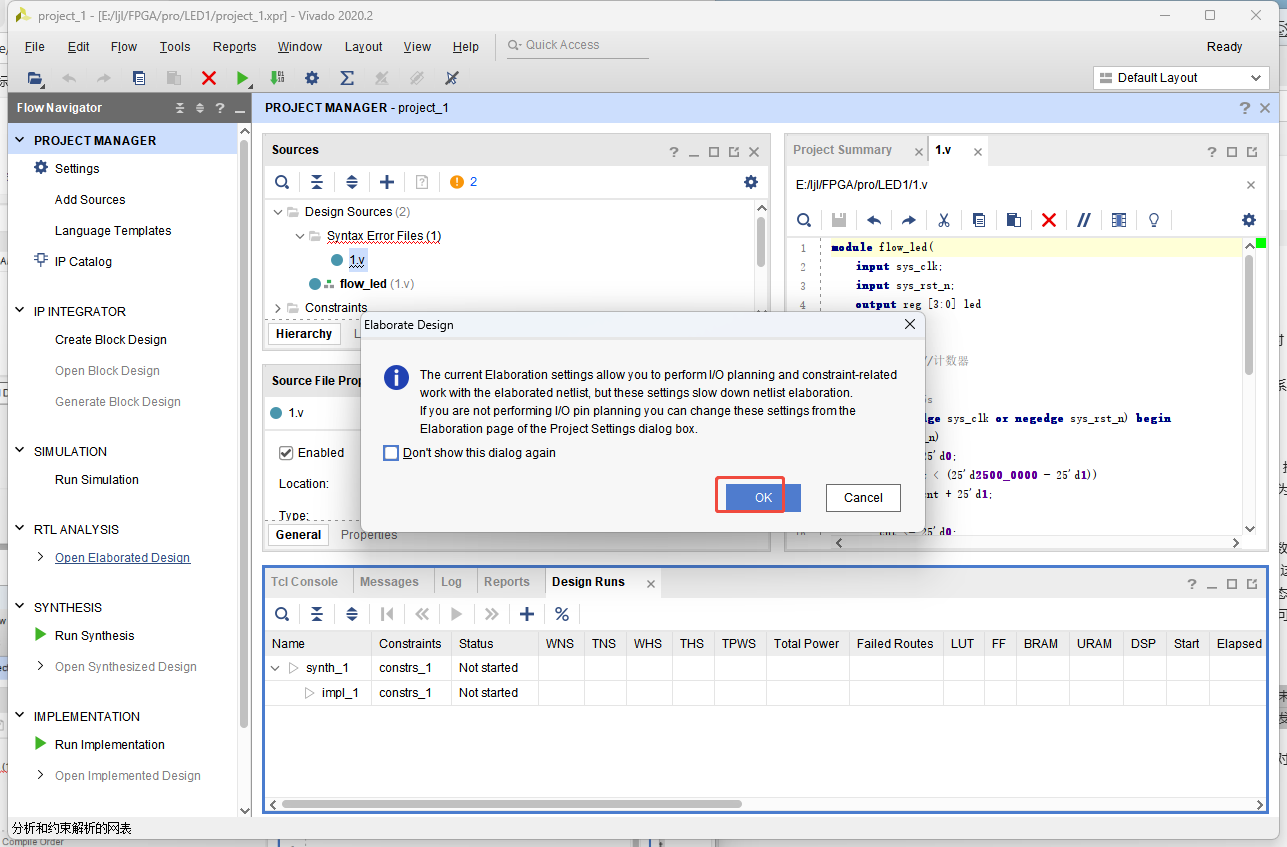

分析与综合 pen Elaborated Design

约束输入 XX.xdc

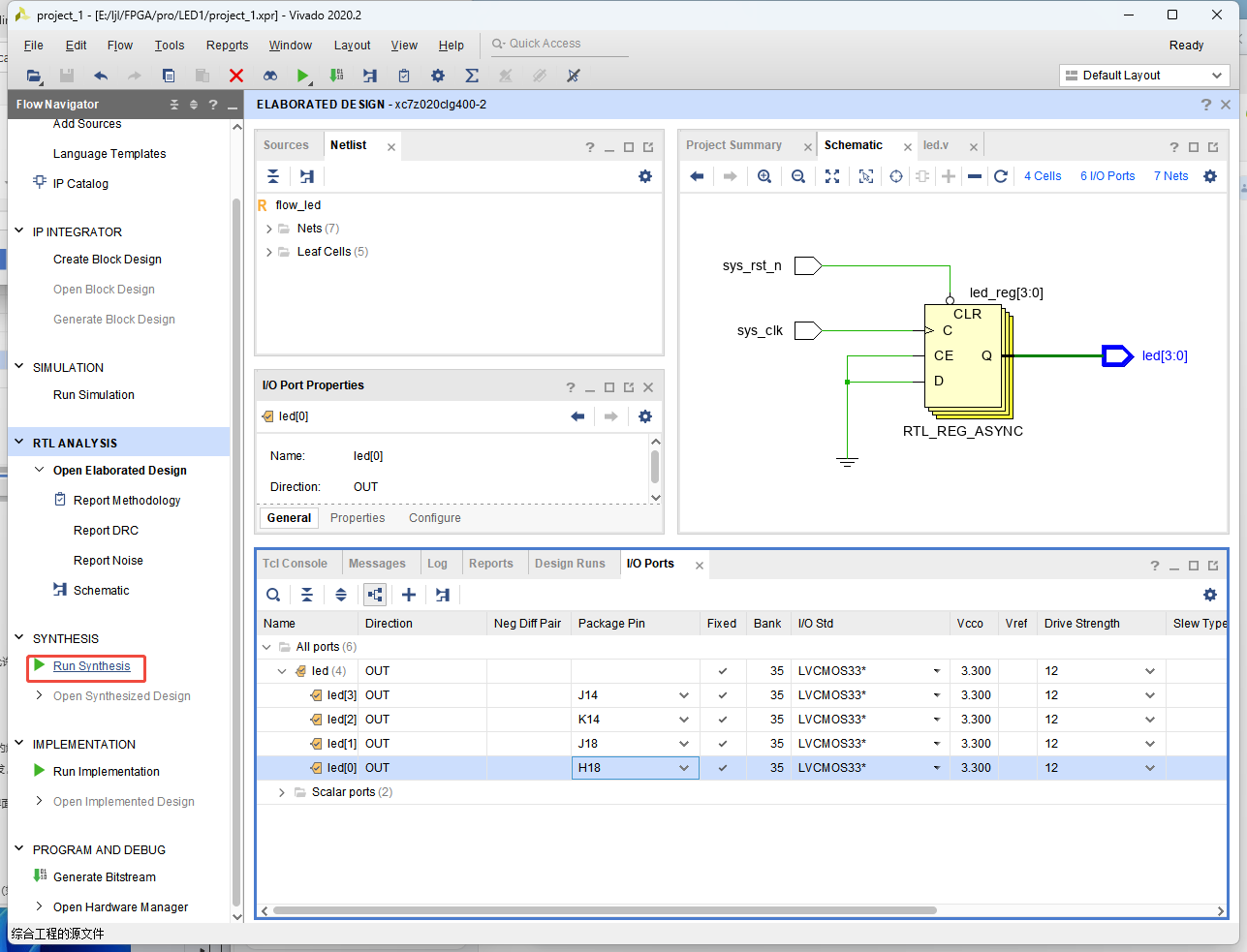

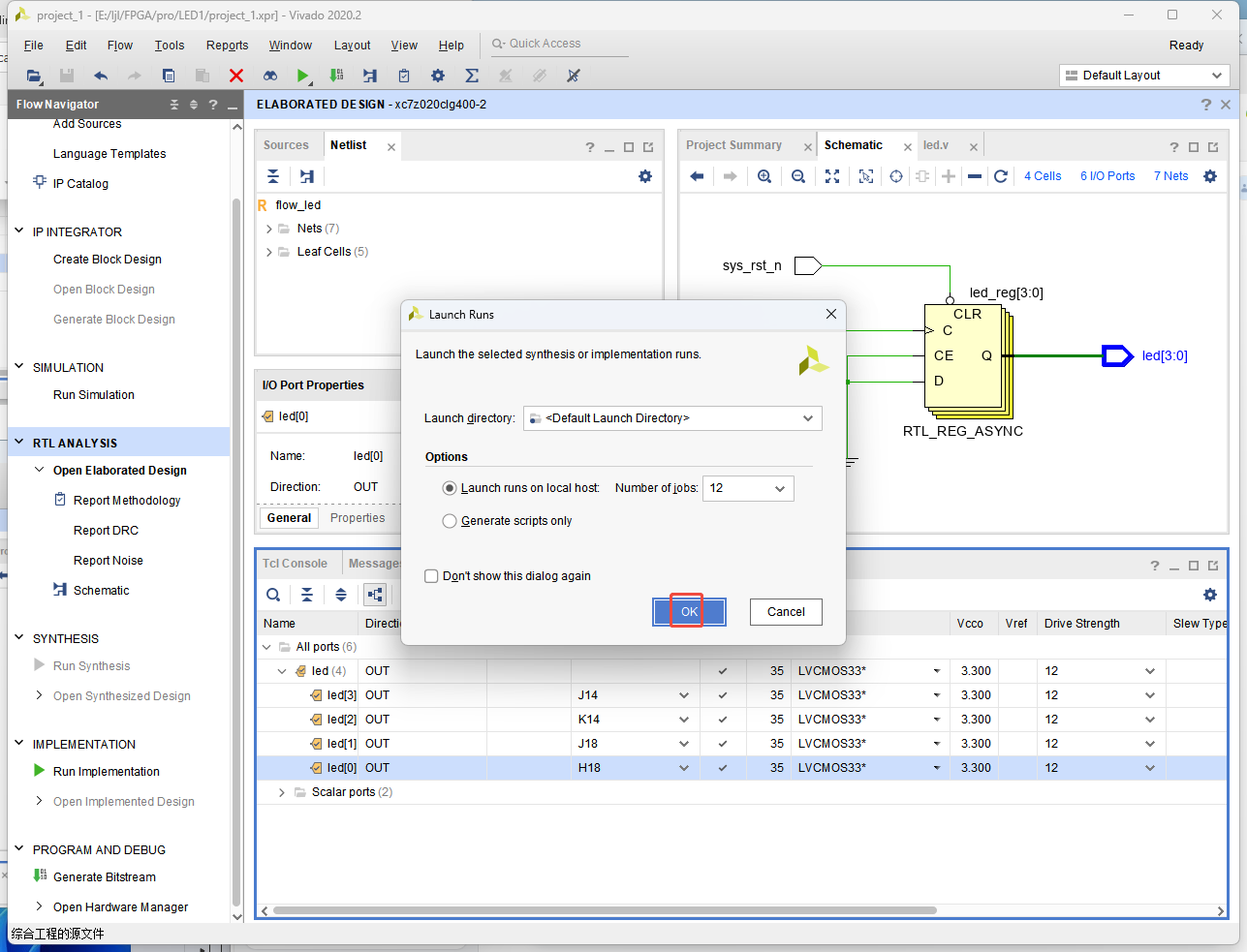

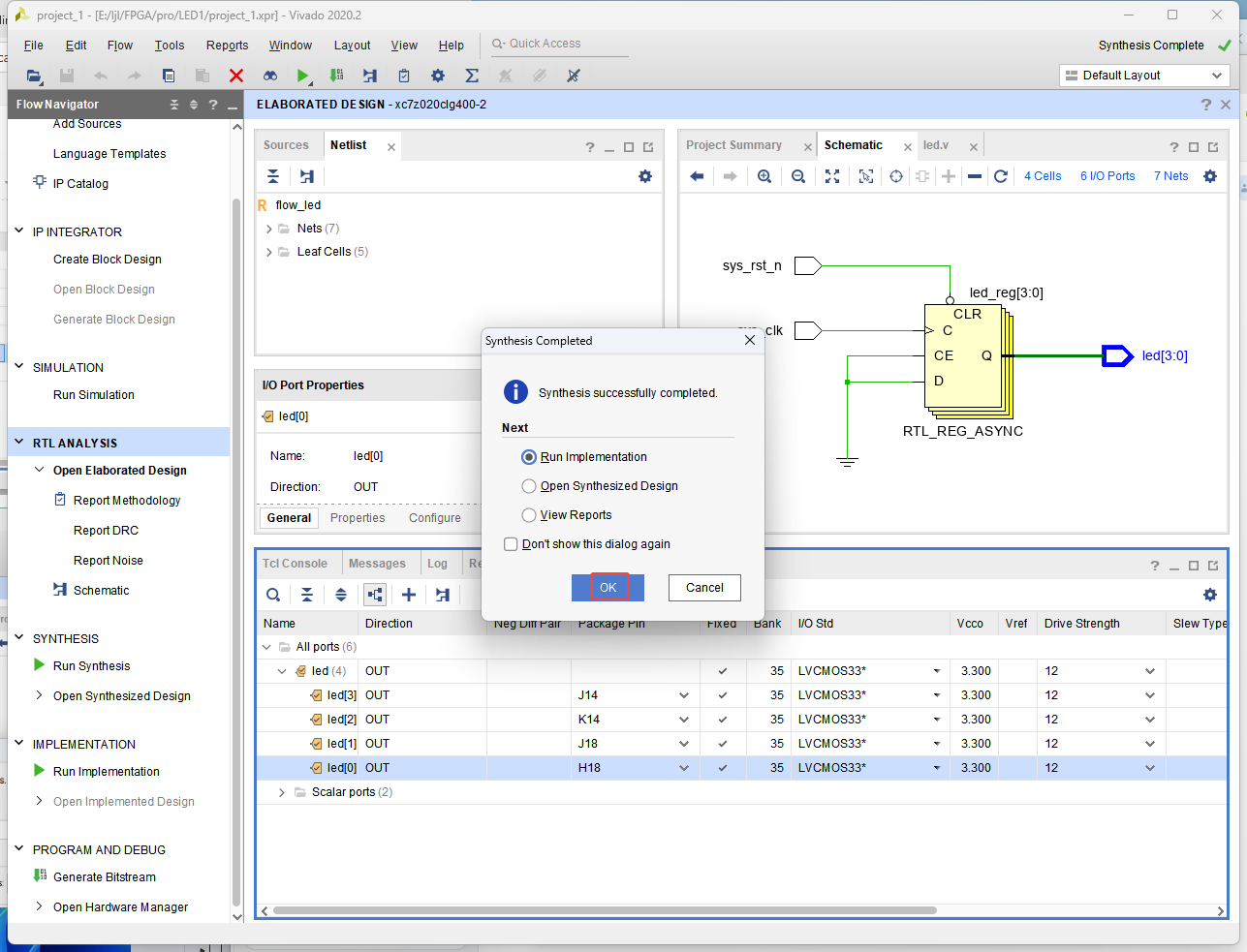

综合 Run Synthesis

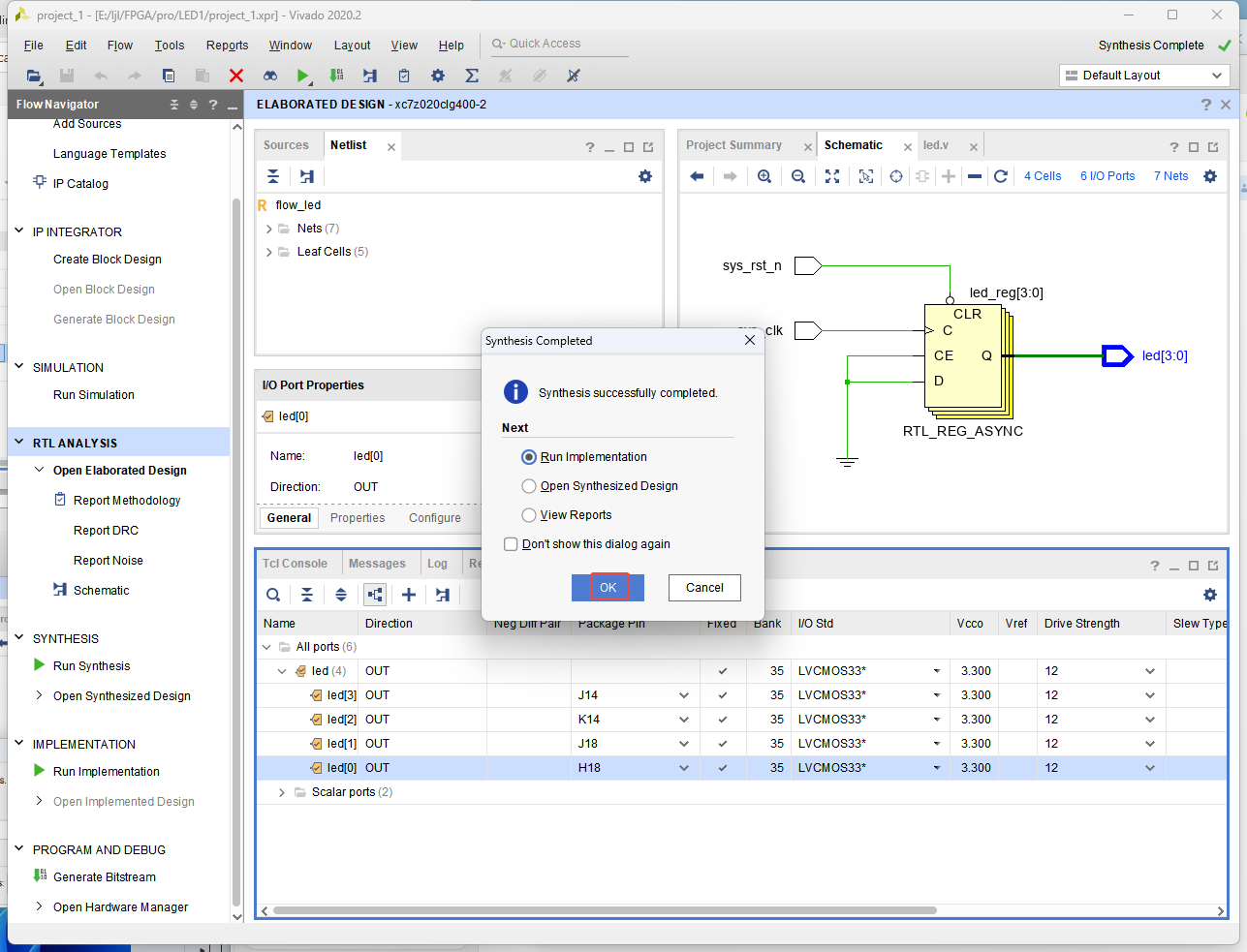

设计实现 Run Implementation

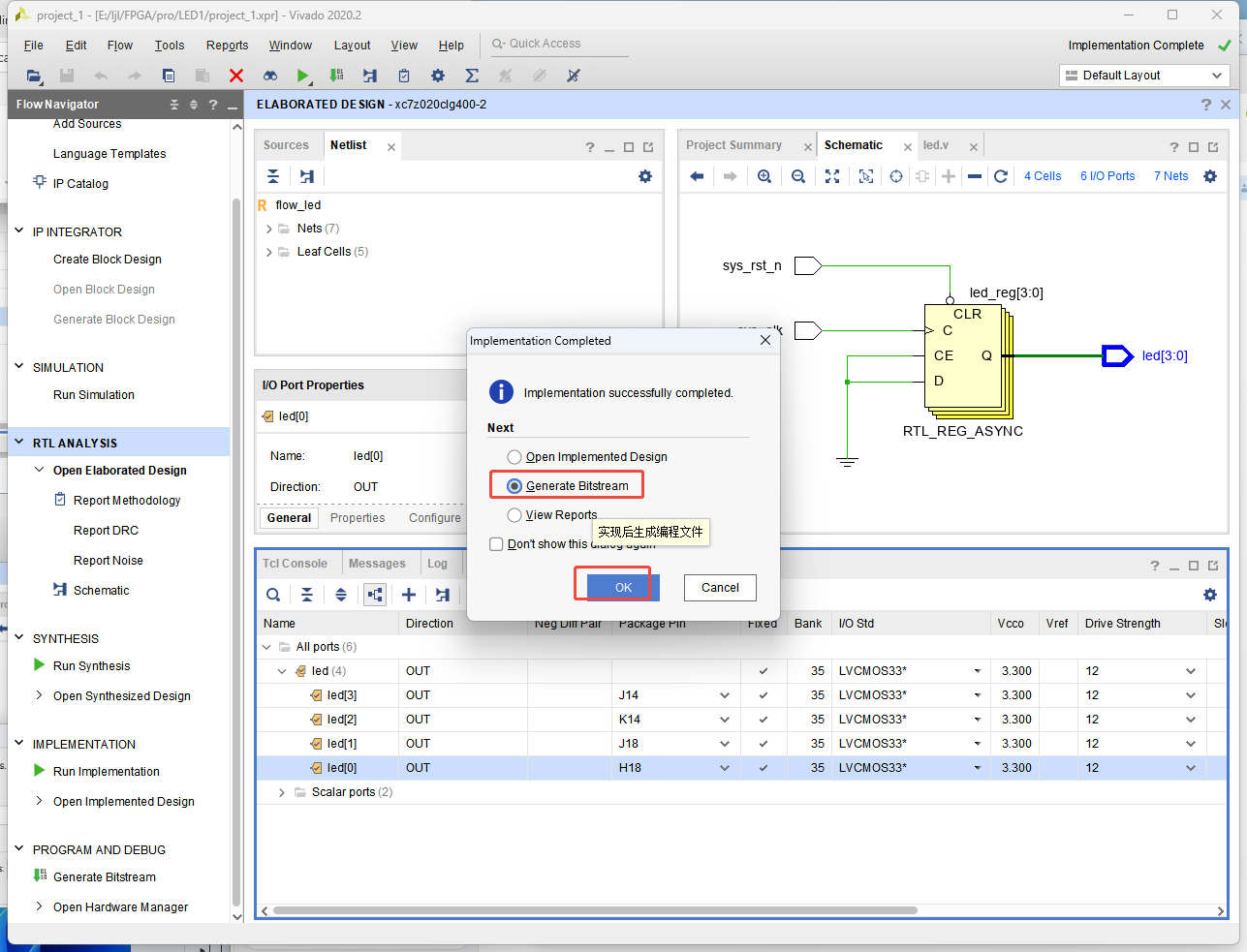

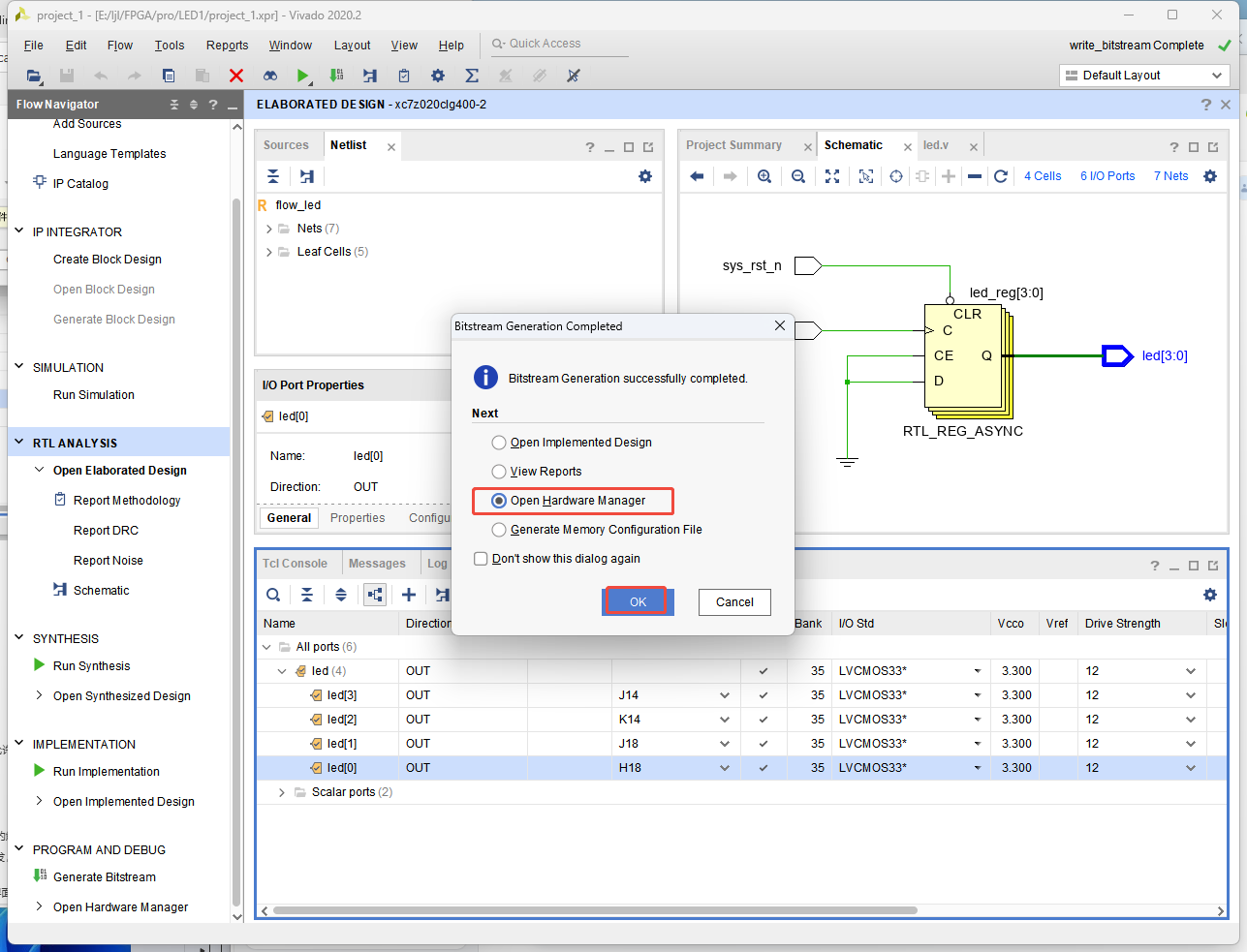

Generate Bitstream

Open Hardware Manager

Program Device

上板验证及调试

在 Vivado 设计工具中,这些流程是从项目创建到硬件编程的关键步骤,每个步骤都有其特定功能和目的:

1.新建工程 Create Project

- 功能:此步骤用于初始化一个新的设计项目。用户需要指定项目的名称、存储路径,并选择所使用的芯片型号或 FPGA 开发板。此外,还可选择添加已有的源文件(如 Verilog 或 VHDL 代码)和约束文件。

- 目的:为整个设计流程搭建框架,设定项目的基本参数和环境,确保后续设计工作基于正确的硬件平台和文件集合进行。

2.分析与综合 Open Elaborated Design

- 功能:分析阶段会检查源文件的语法错误,并将设计文件中的各个模块整理成一个层次化的结构。综合阶段则将高层次的设计描述(如 RTL 级代码)转换为门级网表,优化逻辑结构,以满足目标器件的资源和性能要求。这个过程会根据设定的约束条件(如时序约束)对逻辑进行优化,例如对逻辑门的类型和连接方式进行调整。

- 目的:将用户编写的硬件描述语言代码转化为与目标硬件结构相匹配的门级表示,为后续的实现步骤提供基础,同时确保设计在逻辑上正确且符合目标器件的特性。

3.约束输入 XX.xdc

- 功能:XDC(Xilinx Design Constraints)文件用于对设计添加各种约束条件。主要包括时序约束(如时钟频率、建立时间和保持时间等)、I/O 约束(指定引脚的电气特性和连接关系)以及面积约束(对逻辑资源使用的限制)等。通过这些约束,指导后续的综合和实现过程,使设计满足特定的性能和硬件连接要求。

- 目的:确保设计在目标硬件上能够按照预期的性能指标运行,同时保证输入输出接口与外部电路正确连接。例如,通过设置时钟约束,可以保证设计在指定的时钟频率下稳定工作。

4.综合 Run Synthesis

- 功能:再次执行综合过程,这次会结合之前输入的约束条件,进一步优化门级网表。综合工具会根据约束对逻辑进行映射、优化和布局,将逻辑门适配到目标 FPGA 或 ASIC 的资源上,生成一个满足约束条件的优化后的网表文件。

- 目的:生成一个针对目标硬件的、经过优化的门级描述,为后续的设计实现做好准备,在满足约束条件的前提下,尽可能提高设计的性能、降低资源消耗。

5.设计实现 Run Implementation

- 功能:实现过程分为布局(Placement)和布线(Routing)两个主要步骤。布局阶段会将综合生成的逻辑单元(如逻辑门、寄存器等)分配到目标器件的具体物理位置上,考虑逻辑单元之间的连接关系和资源利用效率。布线阶段则负责在布局完成后,通过金属导线连接各个逻辑单元,形成完整的电路连接,同时确保满足时序和电气要求。

- 目的:将逻辑设计映射到实际的硬件物理结构上,生成最终可用于编程目标器件的比特流文件所需的中间文件,保证设计能够在目标硬件上正确运行,满足所有的约束条件。

6.Generate Bitstream

- 功能:此步骤将实现阶段生成的布局布线信息转换为二进制的比特流文件。比特流文件包含了对目标 FPGA 进行编程的详细配置信息,用于配置 FPGA 内部的可编程逻辑单元、互连资源以及输入输出单元,使其实现设计所期望的功能。

- 目的:生成能够直接用于对 FPGA 进行编程的文件,该文件包含了将设计烧录到硬件所需的全部信息。

7.Open Hardware Manager

- 功能:打开硬件管理器,用于建立计算机与目标硬件(如 FPGA 开发板)之间的连接。它可以检测连接的硬件设备,识别设备的类型和状态,并提供与硬件交互的界面。

- 目的:为将比特流文件下载到目标硬件设备做准备,确保计算机能够与硬件进行通信,以便进行后续的编程操作。

8.Program Device

- 功能:通过硬件管理器将生成的比特流文件下载到目标 FPGA 设备中。这个过程会配置 FPGA 的内部逻辑,使其按照设计的功能运行。一旦编程完成,FPGA 就成为一个实现了特定数字逻辑功能的硬件电路。

- 目的:使目标硬件设备实现用户设计的功能,完成从设计到实际硬件运行的最终步骤。

阅读

《杀死一只知更鸟》

第四章OK