1 相关文档

看门狗可以不使用,但推荐使用,增强系统稳定性。依据手册:

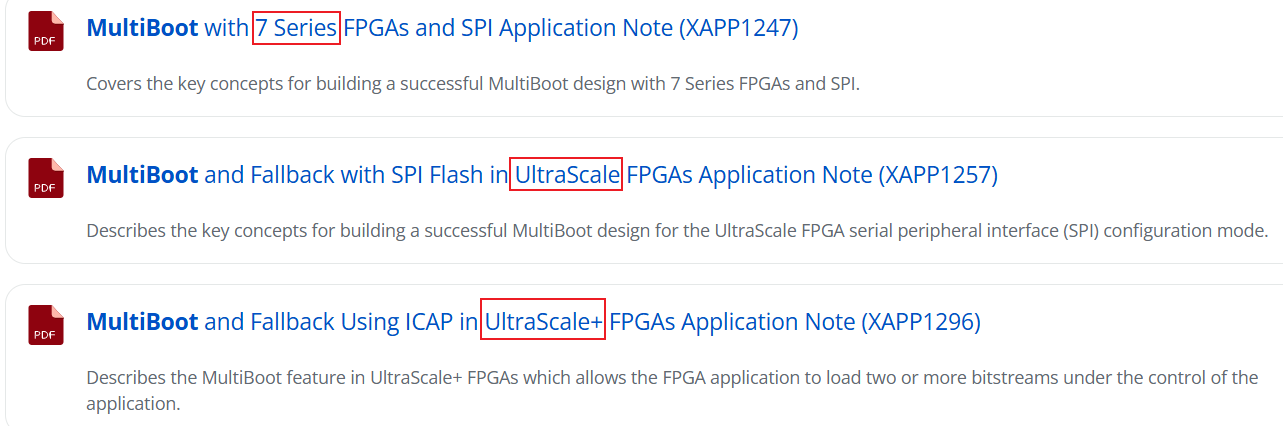

XAPP1247《MultiBoot with 7 serial FPGAs and SPI》

UG470 《7 Series FPGAs Configuration》

XAPP1257《MultiBoot and Fallback with SPI Flash in UltralScale FPGAs》

看门狗时间设置影响两个镜像Golden image和Update image的正确加载。

2 两个看门狗的reg设置

2.1和2.2提到的两种方式,都是在golden/update image的头部中设置。而《3.1.2使用单独的timer image》中提到的方法用独立的bin文件设置看门狗,golden/update image的头部中仅执行关闭,不推荐该方法。

2.1 在XDC文件中用指令设置reg

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design]

set_property BITSTREAM.CONFIG.SPI_FALL_EDGE YES [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 31.9 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGFALLBACK Enable [current_design]

set_property CONFIG_VOLTAGE 1.8 [current_design]

set_property CFGBVS GND [current_design]

#Update/Multi image

set_property BITSTREAM.CONFIG.TIMER_CFG 0x3000000 [current_design]

#Golden image

#set_property BITSTREAM.CONFIG.TIMER_CFG 0x1000000 [current_design]

#set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x2000000 [current_design]

#set_property BITSTREAM.CONFIG.NEXT_CONFIG_REBOOT Enable [current_design]

2.2 通过在Vivado GUI设置reg

下图中只截取了部分xdc指令的GUI。

2.3 各设置reg的具体内容

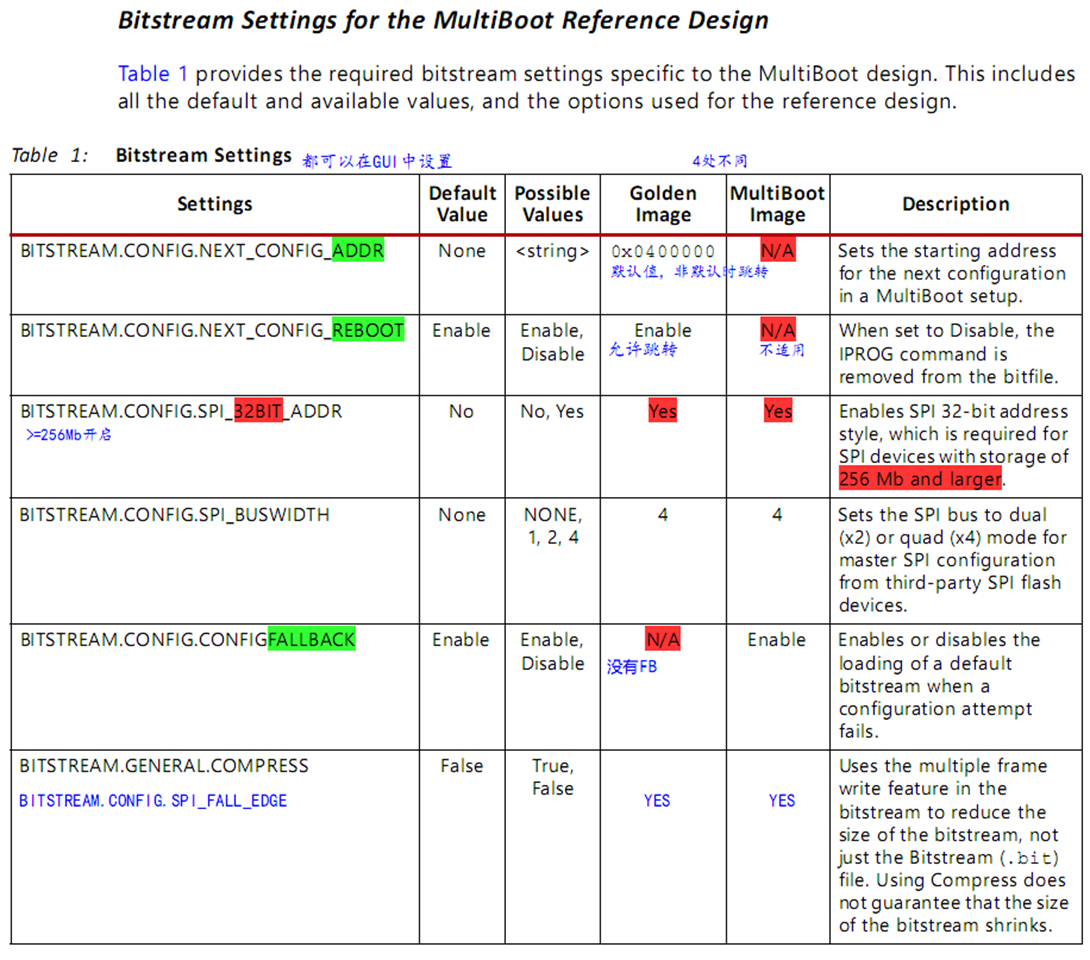

2.3.1常规、回退、跳转reg

建议图中Golden的FALLBACK也开启,在没有Update的头部时,仍可以回滚。

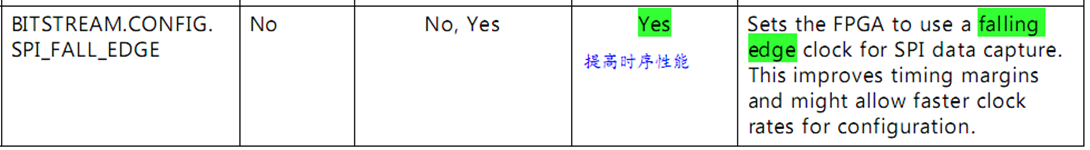

第一次烧写FLASH后没有正常启动,改为FALL_EDGE后重写生成bit并烧写正常启动。

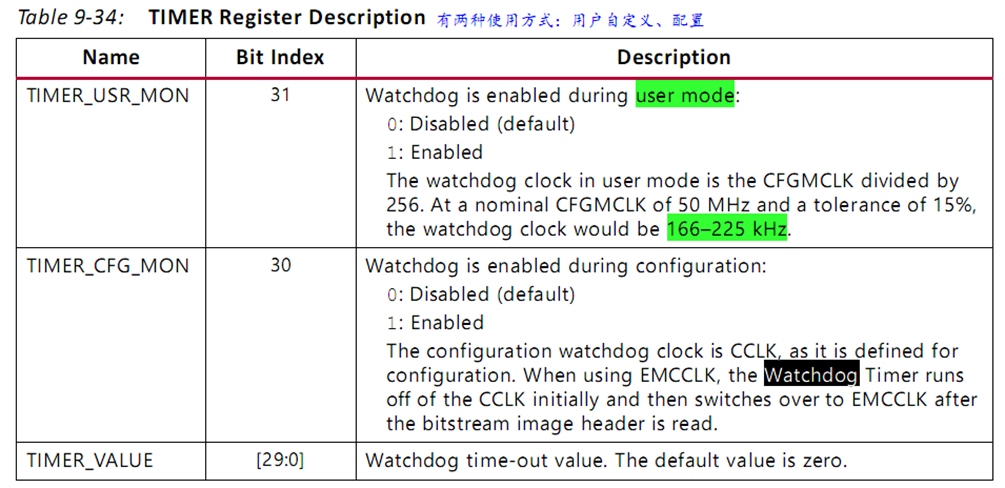

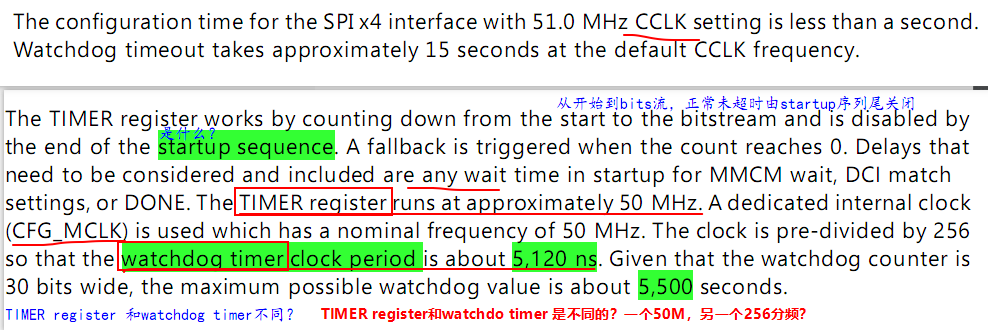

2.3.2 看门狗定时器reg

看门过定时器,分用户、配置两种用法,当上电配置过程中执行配置模式,即本文用到的模式。

M CLK是用户模式CLK ,时钟为内部50MHz 按256分频得到,不同于bit流加载的配置模式 。配置模式时,C CLK由BITSTREAM.CONFIG.CONFIGRATE配置,也可以使用外部的高精度时钟EMCCLK,但上电先用CCLK,读到bit中使用EMCCLK的相关配置后才切换CLK。

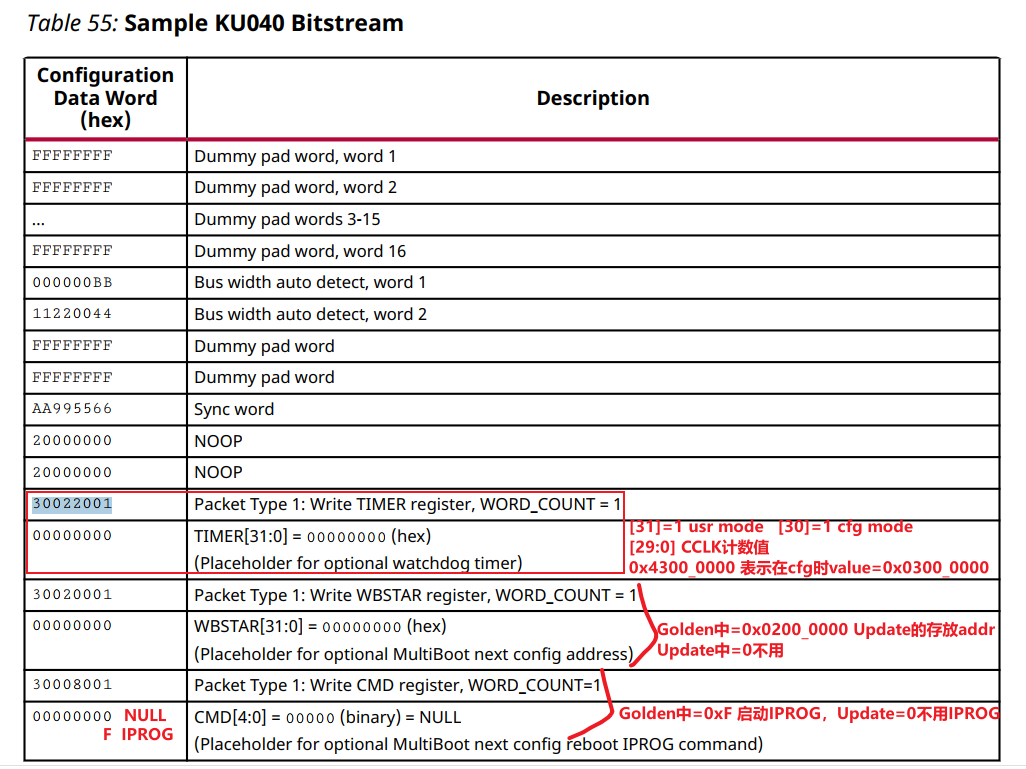

2.4 设置的reg在bit流中的形式

bit流的结构在《UG470 7 Series FPGA Configuration》和《UG570 UltraScale Architecture Configuration》Bitstream Composition中详细描述。所有的设置最终都以reg的形式存储在bit流中,FPGA内有专用的控制器,负责bit流的加载、解析、跳转、复位、控制重启等。SPI位宽,加载时钟频率等COR reg也在其中。

3 工作流程

3.1 正常的工作流程

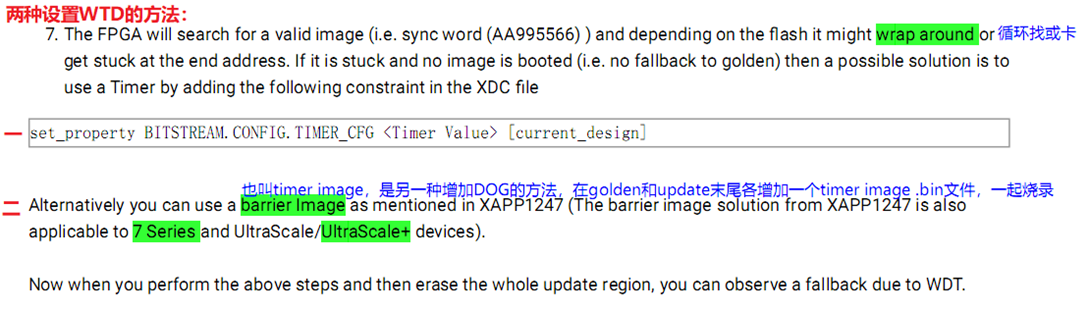

在**《Tips and Considerations while implementing MultiBoot / Fallback with FPGAs in 7 Series, UltraScale and UltraScale+ devices》** 文中提到了两种看门狗的使用方法,两种狗的设置位置不同,看管的时间段也不同:

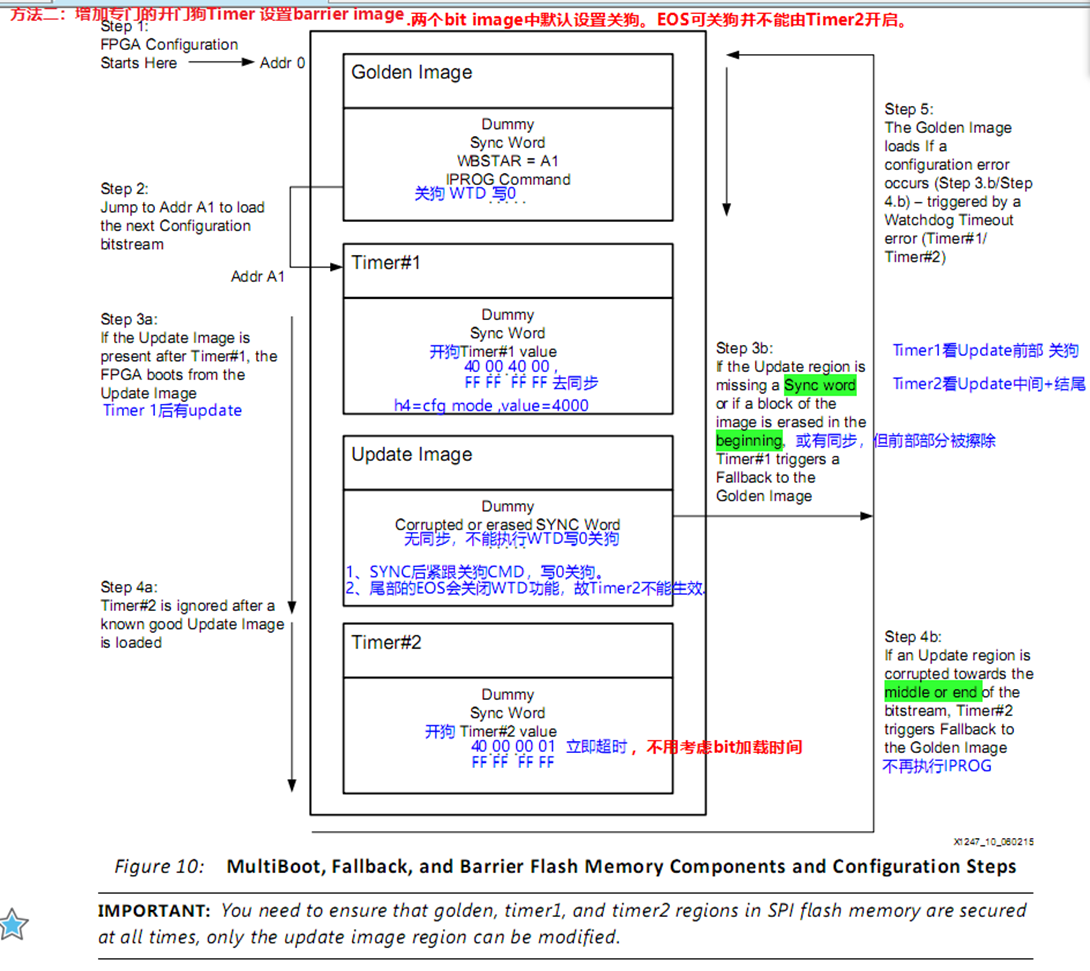

第一种在工程golden/update image中设置狗。先是golden image头中设置狗值,跳转到update image头中时狗值被更新(此狗看管update的头到尾),任何一个EOS都可以关闭狗;

第二种在单独的timer image中设置开启狗,golden/update image中设置关闭狗,两者配合工作。则会有4个= golden + timer_1 + update + timer_2。当update正确执行后会用EOS关闭并屏蔽狗功能,后面的time_2不能再次开启。

3.1.1直接在golden/update image中设置

狗超时->回滚并关狗。

WTD超时的异常分为:有/无Update Image。

若没有Update image,则WTD的值仍然是Golden中的设置,没有被Update重写。

若有Update image的头,则WTD被Update重写,并用此值来检测bit流配置结束EOS(End Of Startup)关狗(包括CCLK和SPI位宽也被更新)

- 只有Golden时,WTD只有Golden中值,且此值超时触发Fallback(IPROG会复位使CCLK=2.7M,SPIx1,直到被Update头重写);

- 正常的Update时,WTD被更新为Update中值,且用于监测整个bit的加载过程,被EOS关闭;

- 尾部损坏的Update时,WTD被更新为Update中值,无EOS关闭WTD,造成超时fallback;

Golden中的WTD值:

- 不用来检测Update超时,Update正常加载时头部有自己的WTD值;

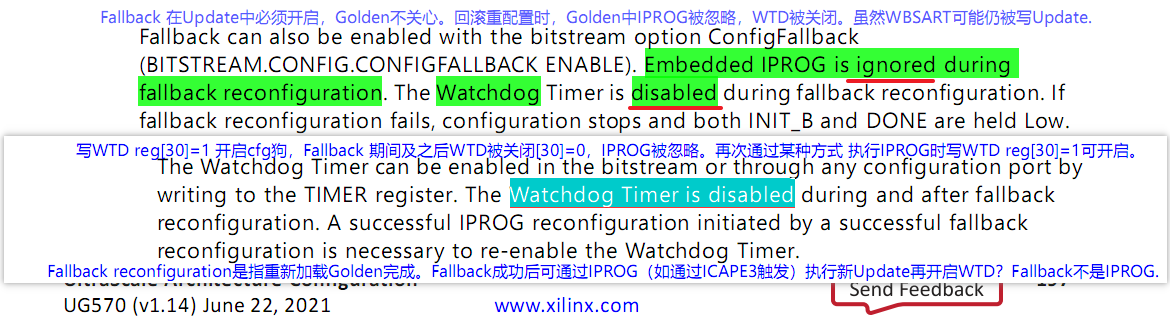

- 不用来监测Golden超时,Fallback时WTD已被关闭,忽略IPROG;

- **只能用来监测查找Update Image 头中的新WTD值超时(**CCLK=2.7M,SPIx1,正常IPROG跳转后立即找到)。

Update中的WTD值:

- 用来监测自己是否执行到EOS,没有则超时触发Fallback,并被关闭。

看门狗被关闭的情况:

- 被EOS关闭。正常关,此时timer counter还未到0;

- 被Fallback关闭。(可能由error、timeout造成)

3.1.2 使用单独的timer image

该方法中需要用vivado把4个BIN文件合并为一个,不推荐用,可理解执行过程。

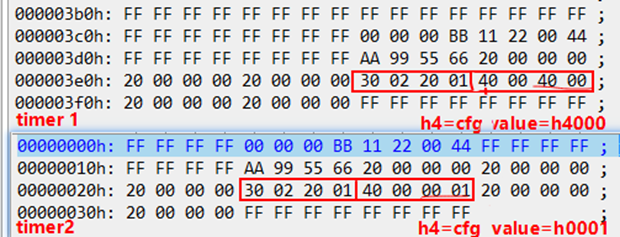

两个timer image中的设置值

3.1.3 bit流的加载启动过程

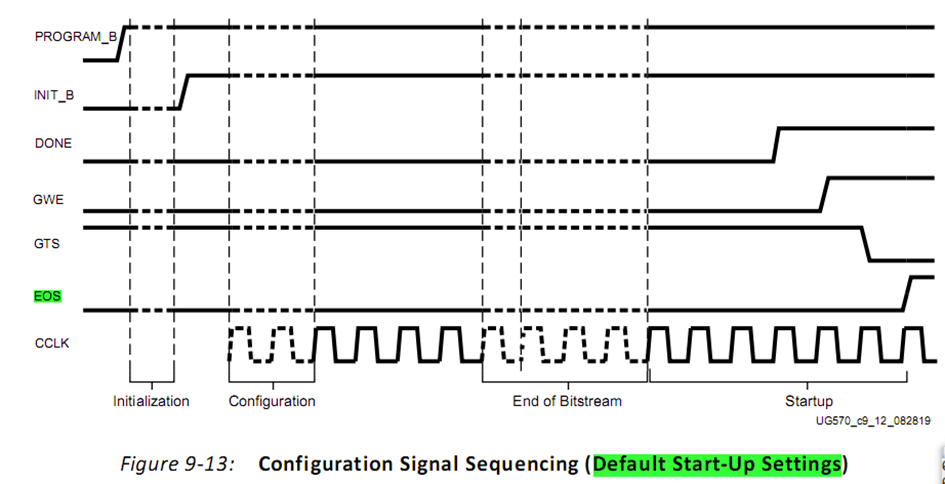

bit流加载过程

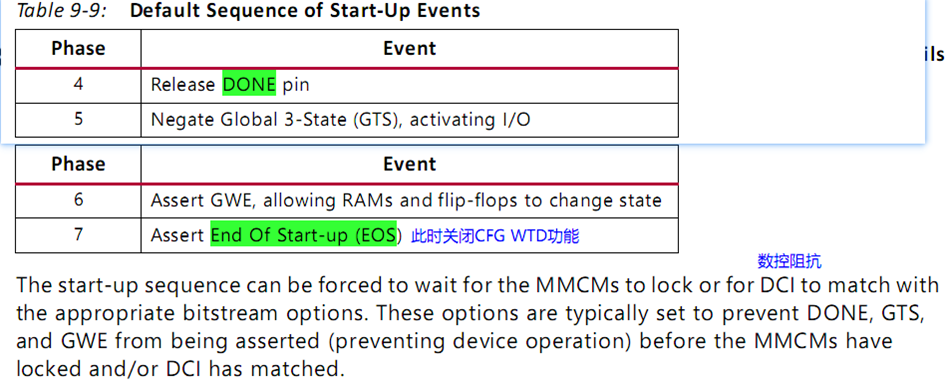

EOS是第8阶段的结束标志,会关闭屏蔽狗功能。

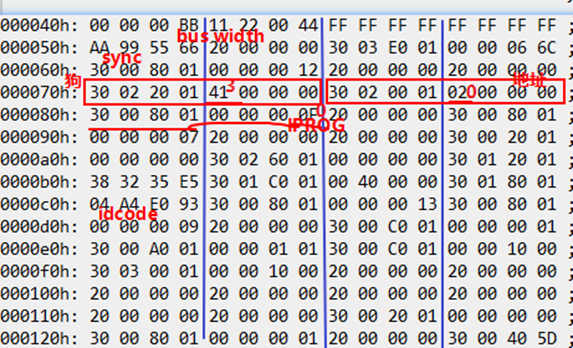

bit流头部的部分配置信息

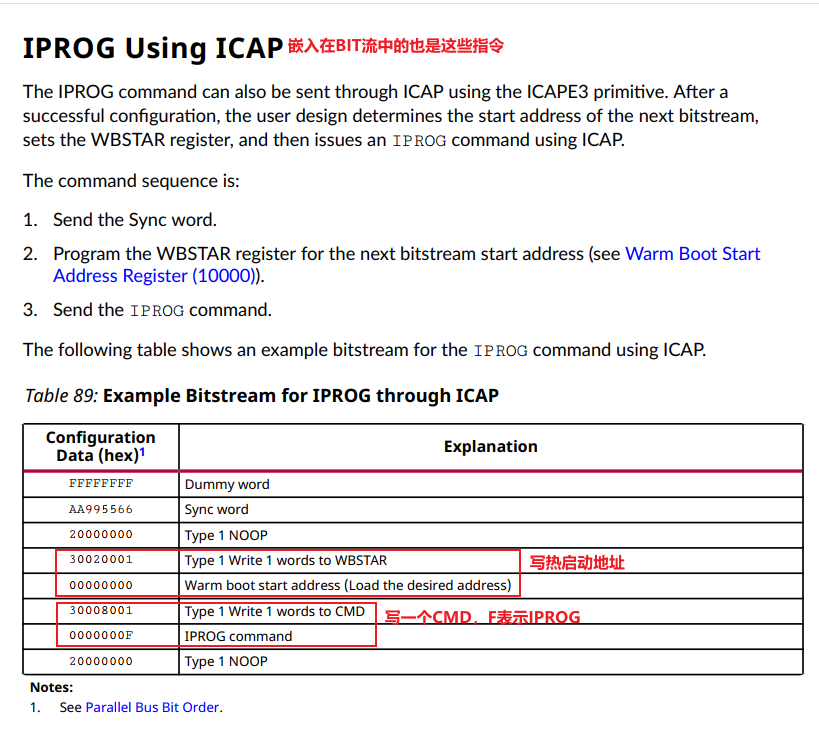

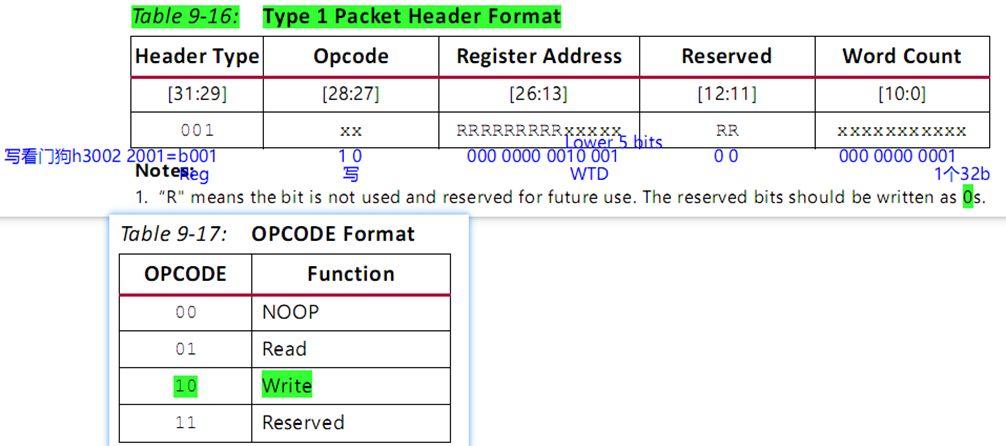

reg读写格式

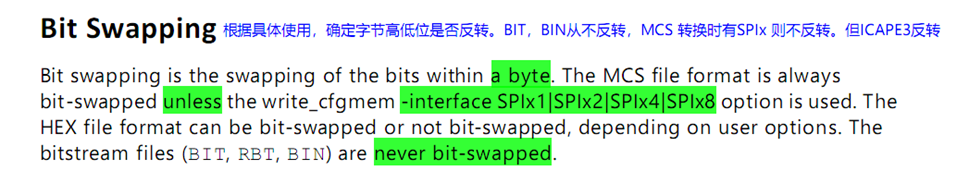

bit流中的数据被处理器分包,type1操作FPGA的reg。Tpye2紧跟type1并用1的地址写大块数据。详细信息查询手册,通过ICAPE3控制FPGA软重启时需要知道指令格式,且要注意字节内的位反序。

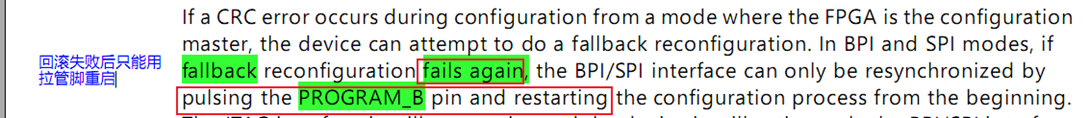

CRC或IDcode错误也可触发回滚

4 通过JTAG调试跳转

4.1 带JTAG的两种重新加载bit方法

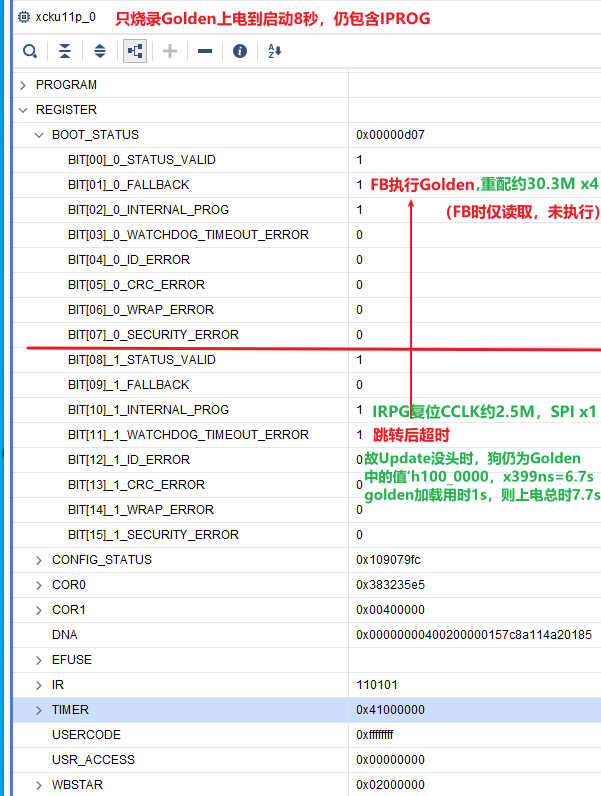

带JTAG上电的影响:已正确烧录Golden+Update,带JTAG上电启动仅加载了Golden。(首次IPROG后WTD超时,fallback到Golden,此时Golden中的IPROG和WDOG流已加载并记录在状态reg中,但功能被屏蔽不执行)。

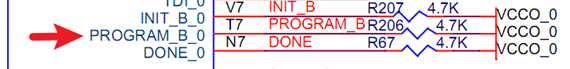

4.1.1硬件管脚

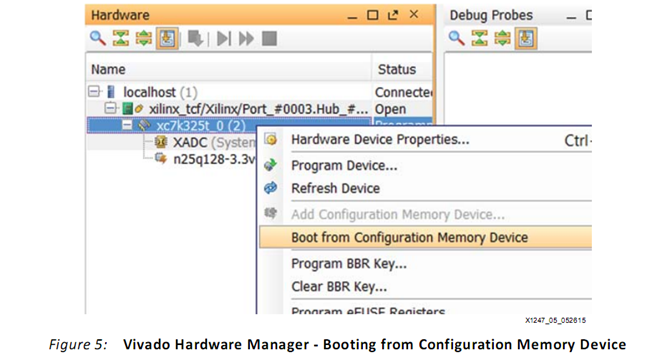

4.1.2 软件选择

4.2 通过JTAG读取状态reg

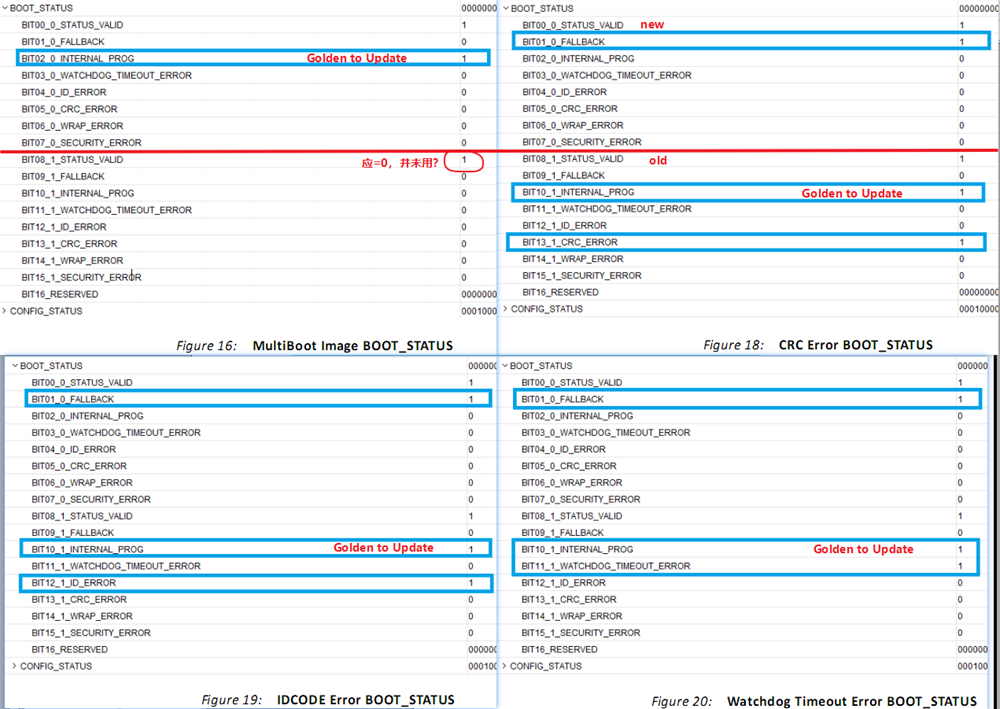

连接JTAG上电后,使用软件重启的方式再次完整执行bit流加载过程(同不带JTAG),用JTAG调试抓取跳转状态STS。

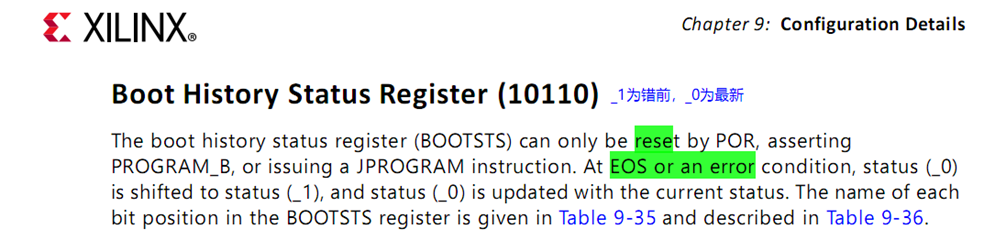

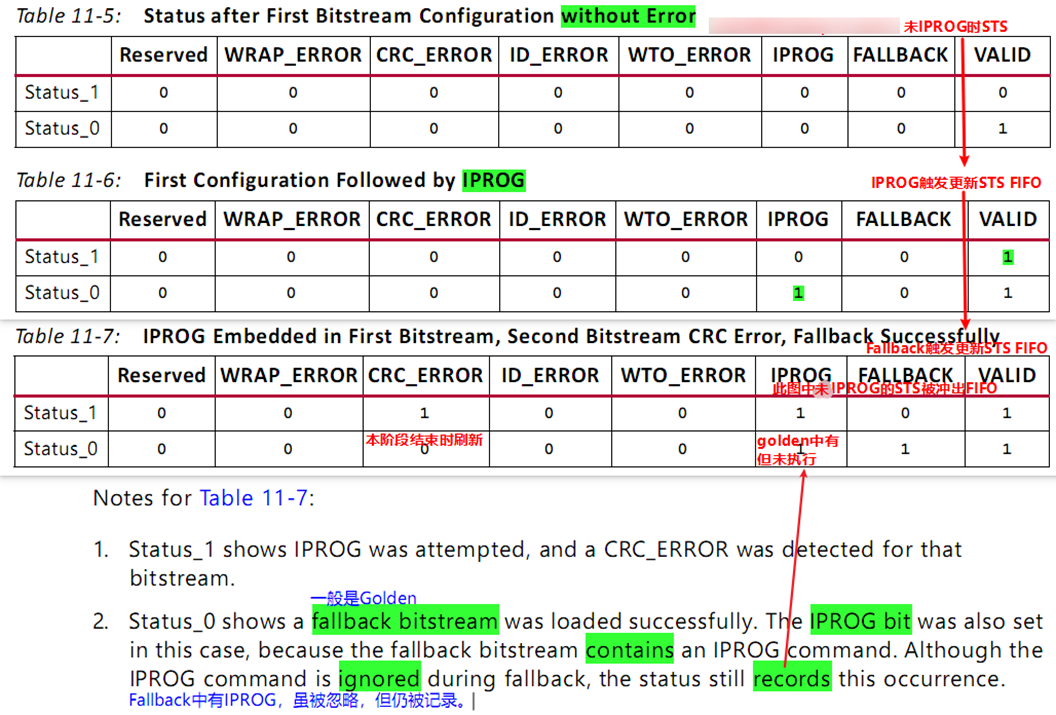

4.2.1 状态FIFO深度为2

一共3个阶段状态,Golden -> IPROG -> Fallback(FB 时Golden中的IPROG未执行仍加载记录),最先的Golden状态被冲出STS FIFO(深度仅2)。从STS_0向STS_1移动。

4.2.2 实测KU+的状态STS与7系列的略有不同

FPGA内部有MCU控制bit流加载的整个流程,并且可以通过reg调整某些步骤。MCU解析bit中的指令,来设置自己的reg及流程,在fallback时ignore Golden中的IPROG,关闭WTD。

5 重要的问题

5.1 Fallback时执行Golden为何不会再进Update,形成死循环?

Fallback 时IPROG被忽略关闭,WTD被关闭,若fallback golden失败则停止尝试。

5.2 看门狗时间设置

- Update/Multi image中狗超时值的设置。16MB的image,SPIx4,CCLK=31.9M,正常加载用时T=16Mx8/(31.9Mx4)=1s,则1s的clk个数=31.9x1024x1024=33,449,574=0x1FE_6666,增加30%误差后=0x297_851E,取整0x300_0000约1.6s。

- Golden中的时间首次执行时仅用于检测Update的头,可适当减少,用0x100_0000(fallback时该值被忽略狗不执行)。

5.3 固化FLASH是否启用32b地址

FPGA默认的flash地址线为24bits?

>=256Mb时必需扩展地址位宽到32才能访问所有空间。开启下降沿提升时序性能。

5.4 Multiboot中Update未烧录或头损坏时WTD时间

当仅烧录Golden或Update的头被擦除后断电,实测上电后工作时间约8秒,其中Fallback加载Golden约1s(31.9M_SPIx4),WTD约7秒。并非Golden中设置的h'100_0000*golden中设置的CCLK(31.9M)周期=526ms。原因为IPROG后CCLK、位宽被复位默认2.7M_SPIx1,若有Update头重新配置则按照新的时钟和位宽,否则仍保持默认。

Update头好尾坏时,WTD用Update中的0x300_0000,且CLK=31.9M,则超时等待约1.6s。

测试方法:连接JTAG后,选择从FLASH启动,见下图中流程正确,WTD超时后fallback,0进1出。