【FPGA+DSP系列】------(3)中断学习(以定时器中断为例)

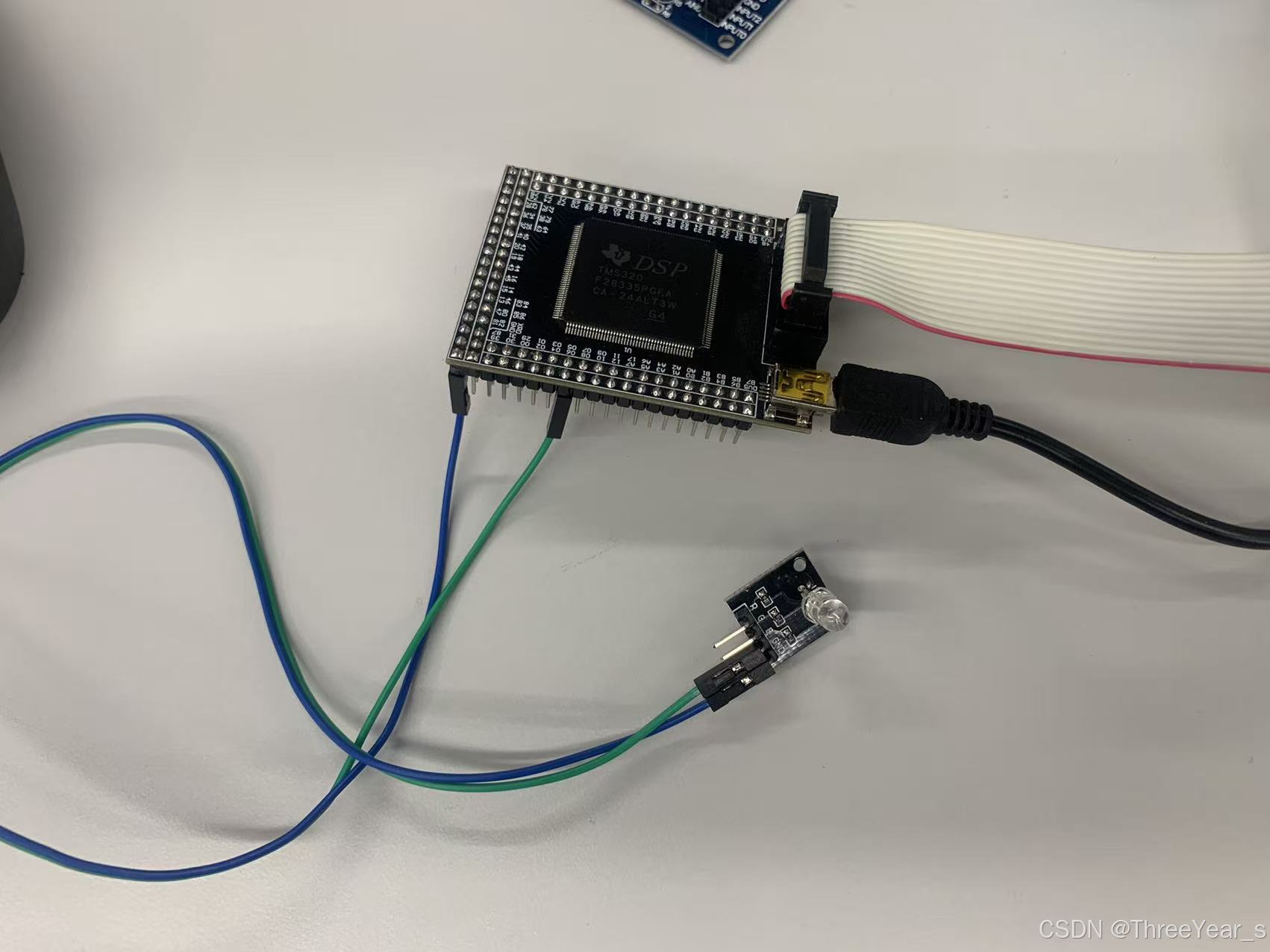

实验准备

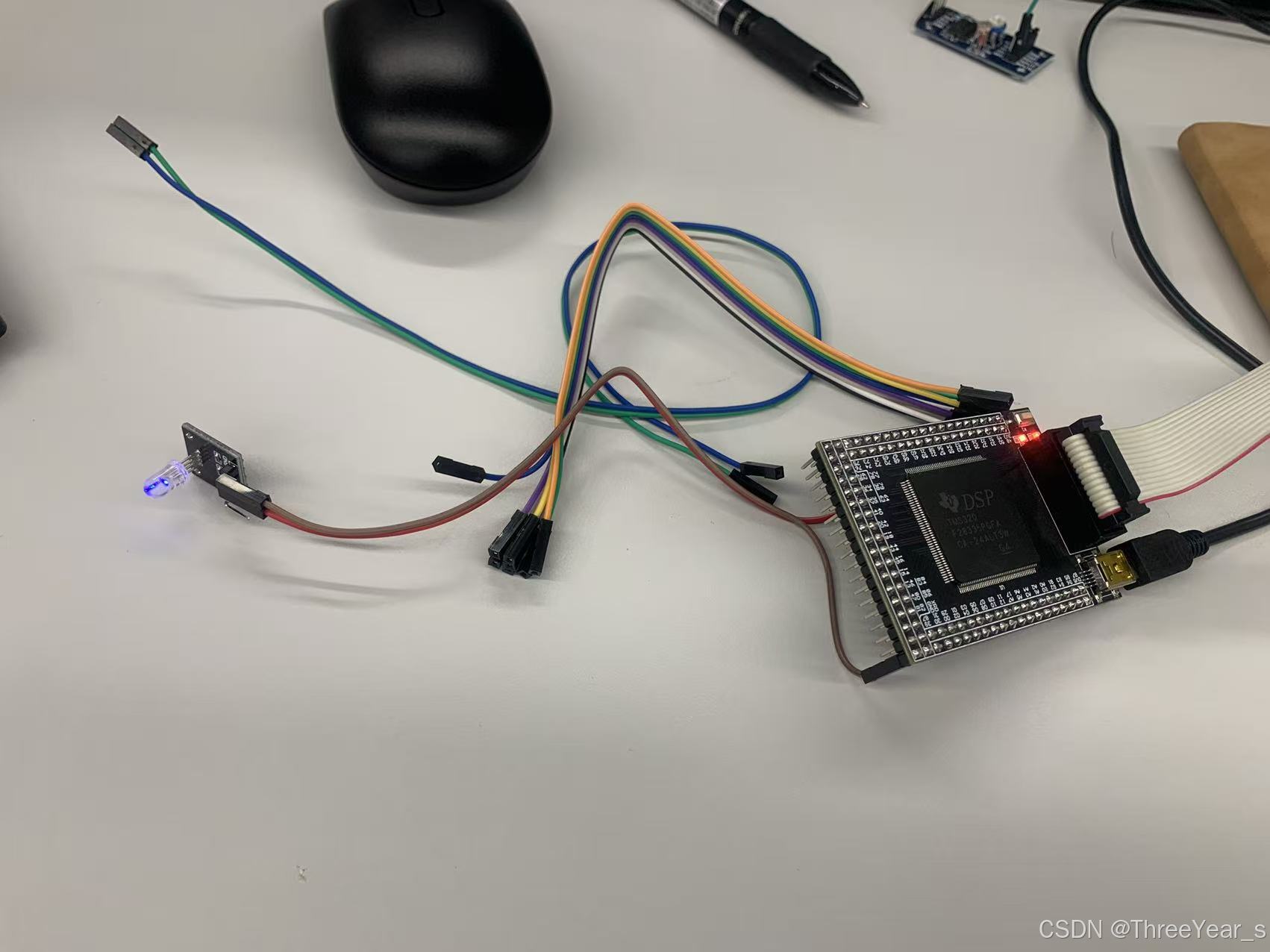

准备:LED灯/DSP核心板/下载器

实现定时器中断进行LED灯闪烁,复习中断的基本概念,学习中断在ccs里面的配置,了解相关寄存器的含义。

一、中断介绍

中断概念

中断是嵌入式开发中一个十分重要的技术手段,触发中断后,CPU暂停现有进程,去完成中断服务函数,完成后结束中断回到现有进程。有些中断还能够被其他高优先级的中断所中断,那么这种情况又叫做中断的嵌套。

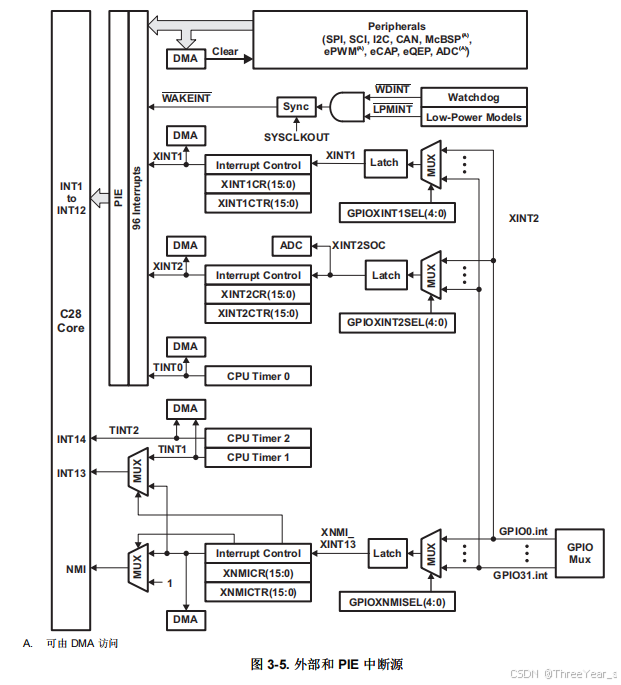

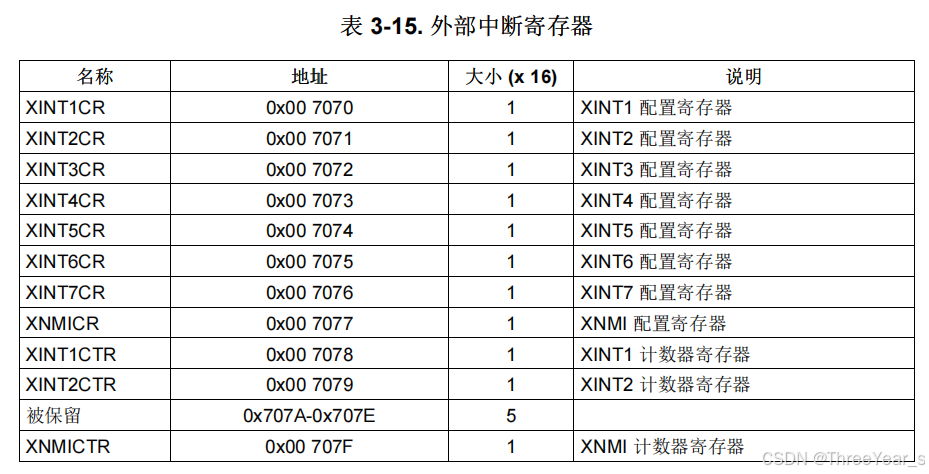

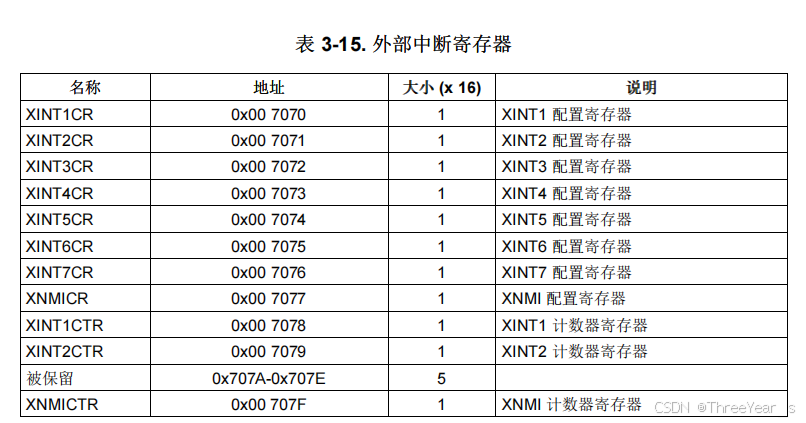

如下图是整体中断的分布,此器件支持 8 个被屏蔽的外部中断 (XINT1--XINT7, XNMI)。 XNMI 可被连接至 INT13 或者 CPU 的 NMI 中断。 这些中断中的每一个可被选择用于负边沿、正边沿或者正负边沿触发,并且可被启用或禁用。 XINT1, XINT2,和 XNMI 还包含一个 16 位自由运行的上数计数器,当检测到一个有效的中

断边沿时,该计数器复位为 0。 这个计数器可被用于为中断精确计时。 与 281x 器件不同,没有用于外部中

断的专用引脚。

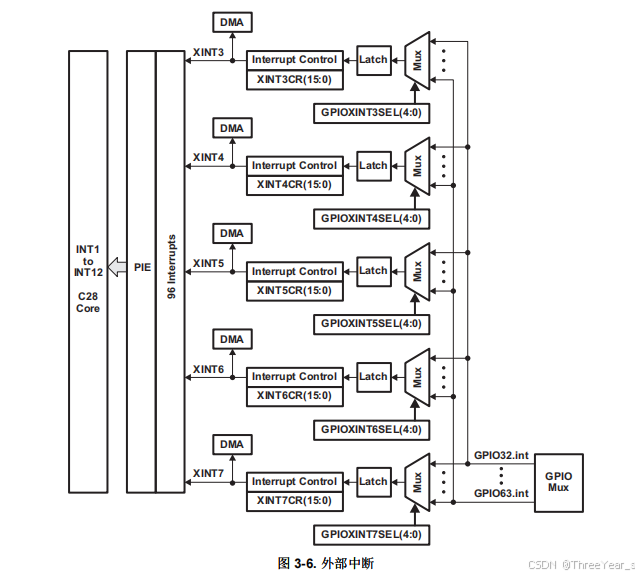

XINT1,XINT2 和 XINT 中断可接受来自 GPIO0-GPIO31 引脚的输入。 XINT3--XINT7 中

断可接受来自 GPIO32-GPIO63 引脚的输入。

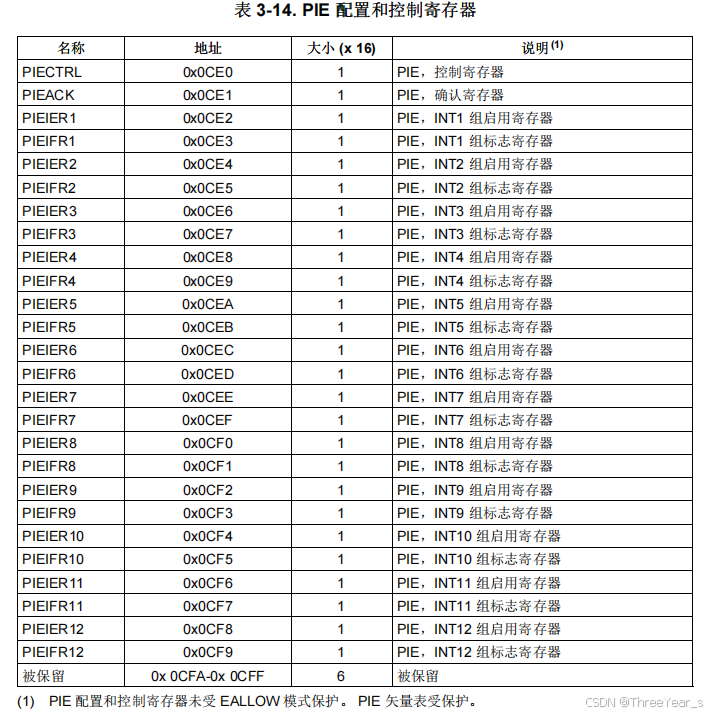

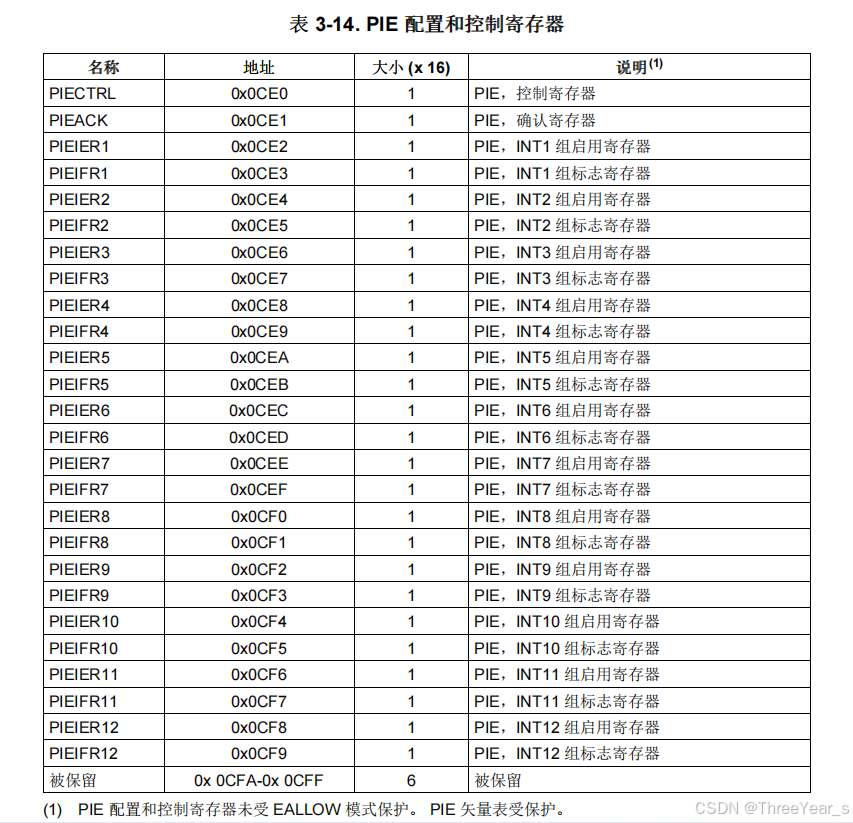

中断相关寄存器

PIE 控制寄存器(PIECTRL)

中断机制描述

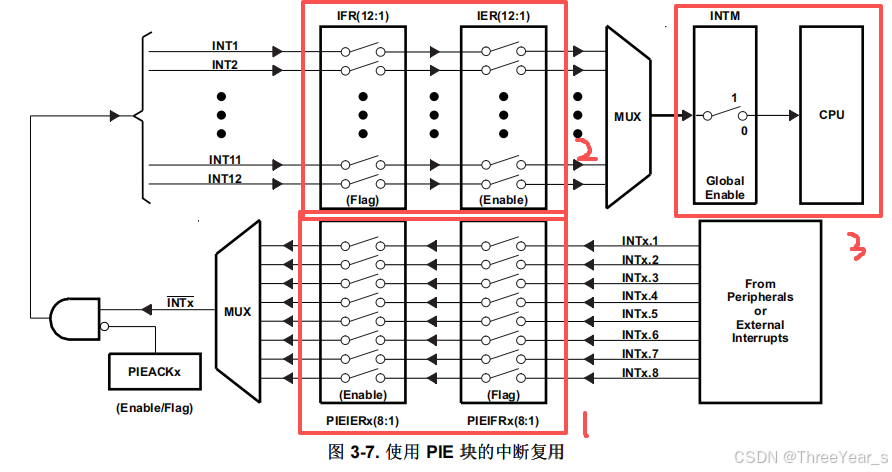

F28335 的中断采用的是 3 级中断机制,分别是外设级中断、PIE 级中断和 CPU级中断,最内核部分为 CPU 级中断,即 CPU 只能响应从 CPU 中断线上过来的中断请求,但 F28335 中断源很多,CPU 没有那么多中断线,在有限中断线的情况下,只能安排中断线进行复用,其复用管理就有了中间层的 PIE 级中断,外设要能够成功产生中断响应,就要首先经外设级中断允许,然后经 PIE 允许,最终 CPU做出响应。其工作原理流程图如下图所示

外设中断

CPU 正常处理程序过程中,外设产生了中断事件(比如定时器定时时间到,串口接收数据完成),那么该外设对应中断标志寄存器(IF)响应的位将被自动置位,如果该外设对应中断使能寄存器(IE)中响应的使能位正好置位(需要软件控制),则外设产生的中断将向 PIE 控制器发出中断申请。如果对应外设级中没有被使能,就相当于该中断被屏蔽,不会想 PIE 提出中断申请,更不会产生CPU 中断响应,但此时中断标志位寄存器的标志位将保持不变,一直处在中断置位状态,要使该中断信号消失,中断标志寄存器复位,就需要软件编程清楚,如果没有被清楚,中断产生以后,一旦中断使能位被使能,同样会向 PIE 申请中断。进入中断服务后,有部分硬件外设会自动复位中断标志寄存器,多数外设需要在中断服务中手动复位中断标志寄存器。

重点就是如果你要使用某个外设中断,比如说要使用定时器中断,你一定要使能对应的pie寄存器,不然产生中断也不会到CPU。同时就是如果产生了外设中断,但是没有使用,一定要清除中断标志位,避免一旦使能后触发。

PIE 级中断

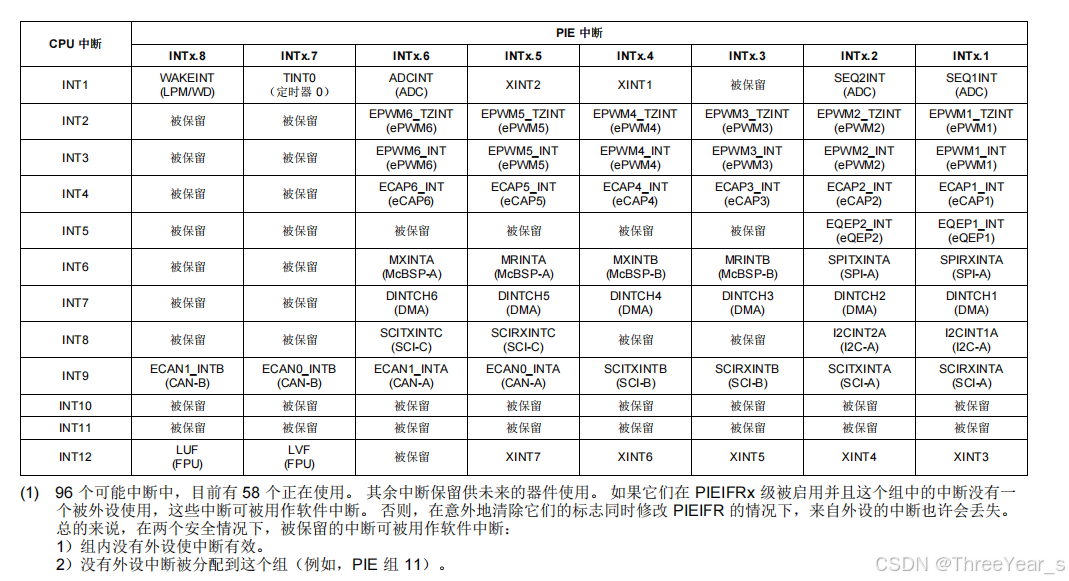

实际有效外设中断为 58 个,其余为保留。PIE 第一组中断分别为 WAKE、TIMER0、ADC、XINT2、XINT1、第三个中断保留、SEQ2、SEQ1。和外设级中断类似,在 PIE 模块内每组中断有相应的中断标志位(PIEIFRx)和使能位(PIEIERx.y)。除此之外,每组 PIE 中断(INT1~INT12)有一个响应标志位(PIEACK)。下图给出了 PIEIFR 和 PIEIER 不同设置时的 PIE 硬件的操作流程。

CPU中断

一旦 CPU 申请中断,CPU 级中断标志位(IFR)将置 1。中断标志位锁存到标志寄存器后,只有 CPU 中断使能寄存器(IER)或中断调试使能寄存器(DBGIER)相应的使能位和全局中断屏蔽位(INTM)被使能时才会响应中断申请。CPU 级使能可屏蔽中断采用 CPU 中断使能寄存器(IER)还是中断调试使能寄存器(DBGIER)与中断处理方式有关。标准处理模式下,不使用中断调试使能寄存器(DBGIER)。只有当 F28335 使用实时调试(Real-time Debug)且 CPU 被停止(Halt)时,才使用中断调试使能寄存器(DBGIER),此时 INTM 不起作用。如果 F28335 使用实时调试而 CPU 仍然工作运行,则采用标准的中断处理。

中断优先级

CPU 响应中断是通过中断线的,而且只能 1 次响应其中 1 条中断线,每条中断线连接的中断向量都在中断向量表中占 32 位地址空间,用来存放中断服务程序的入口地址。有可能这 16 条中断线上的中断请求同时到达 CPU,这时就要对各个中断请求进行优先级定义。每条中断线对应的不是唯一中断,每组 PIE 对应的也不是唯一中断,中断服务程序要处理所有输入的中断请求,这就要求编程人员在服务程序的入口处采用软件方法将这些中断线复用的中断分开,以便能够正确响应中断。但是软件分离的方法会影响中断的响应速度,在实时性要求高的应用中不能使用。这就涉及如何加快中断服务程序的问题。

CPU 的中断优先级有高到低依次是从INT1-INT12。每组 PIE 控制的 8 个中断优先级依次是从 INTx.1-INTx.8。

软件设置中断优先级。使用 CPU IER 寄存器控制全部中断的优先级,PIEIER寄存器控制每组中断的优先级,只有与被服务的中断在同一组时,修改 PIEIFR寄存器的值才有意义,当 PIEACK 位保持来自 CPU 中断时,修改操作才被最终执行。当来自无关本组的中断被执行时,禁止本组的 PIEIER 位没有意义。

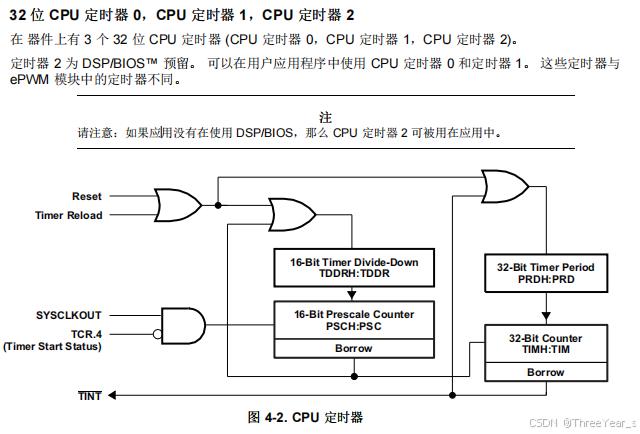

二、定时器中断

TMS320F28335 的 CPU Time 有三个,分别为 Timer0,Timer1,Timer2,其中Timer2 是为操作系统 DSP/BIOS 保留的,当未移植操作系统时,可用来做普通的定时器。这三个定时器的中断信号分别为 TINT0, TINT1, TINT2,分别对应于中断向量 INT1,INT13,INT14。

三、代码分析

time.h

c

/*

* time.h

*

* Created on: 2025年9月29日

* Author: DELL

*/

#ifndef APPS_TIME_TIME_H_

#define APPS_TIME_TIME_H_

#include "DSP2833x_Device.h" // DSP2833x 头文件

#include "DSP2833x_Examples.h" // DSP2833x 例子相关头文件

void TIM0_Init(float Freq, float Period);

interrupt void TIM0_IRQn(void);

#endif /* APPS_TIME_TIME_H_ */time.c

c

/*

* time.c

*

* Created on: 2025年9月29日

* Author: DELL

*/

#include "time.h"

#include "led.h"

//定时器0初始化函数

//Freq:CPU时钟频率(150MHz)

//Period:定时周期值,单位us

void TIM0_Init(float Freq, float Period)

{

EALLOW;

SysCtrlRegs.PCLKCR3.bit.CPUTIMER0ENCLK = 1; // CPU Timer 0

EDIS;

//设置定时器0的中断入口地址为中断向量表的INT0

EALLOW;

PieVectTable.TINT0 = &TIM0_IRQn;

EDIS;

//指向定时器0的寄存器地址

CpuTimer0.RegsAddr = &CpuTimer0Regs;

//设置定时器0的周期寄存器值

CpuTimer0Regs.PRD.all = 0xFFFFFFFF;

//设置定时器预定标计数器值为0

CpuTimer0Regs.TPR.all = 0;

CpuTimer0Regs.TPRH.all = 0;

//确保定时器0为停止状态

CpuTimer0Regs.TCR.bit.TSS = 1;

//重载使能

CpuTimer0Regs.TCR.bit.TRB = 1;

// Reset interrupt counters:

CpuTimer0.InterruptCount = 0;

ConfigCpuTimer(&CpuTimer0, Freq, Period);

//开始定时器功能

CpuTimer0Regs.TCR.bit.TSS=0;

//开启CPU第一组中断并使能第一组中断的第7个小中断,即定时器0

IER |= M_INT1;

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;

//使能总中断

EINT;

ERTM;

}

interrupt void TIM0_IRQn(void)

{

EALLOW;

LED1_BLINK;

PieCtrlRegs.PIEACK.bit.ACK1=1;

EDIS;

}main.c

啥也不用管,初始化time即可

c

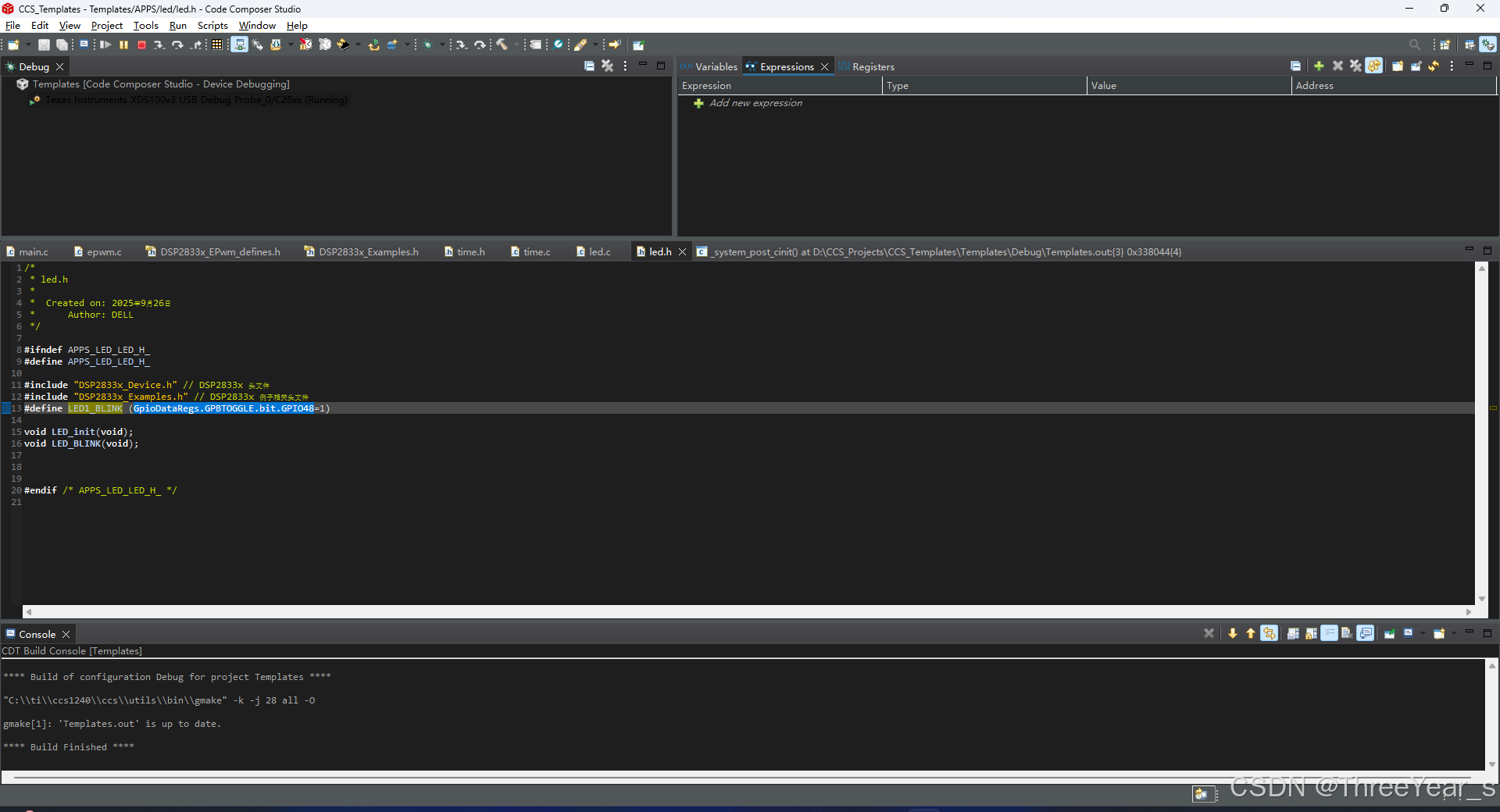

TIM0_Init(150,500000);下载界面

实现LED闪烁

总结

本文介绍了基于FPGA+DSP的定时器中断实验,通过LED灯闪烁演示中断机制。内容涵盖:1)中断概念与三级中断机制(外设级、PIE级、CPU级);2)F28335定时器中断配置方法,包括相关寄存器设置;3)实验代码解析,重点说明定时器初始化流程和中断服务函数编写要点。实验采用150MHz主频、500ms周期的定时器中断控制LED状态切换,展示了中断优先级管理、中断使能配置等关键技术。文中配有寄存器配置图、中断流程图和CCS工程截图,适合嵌入式开发人员学习DSP中断系统设计。