Calibre部分提参的debug过程

经过后仿一个反相器之后时钟下降沿失真严重,不知道是版图哪里有问题?该如何debug?

【Calibre部分提参】

-

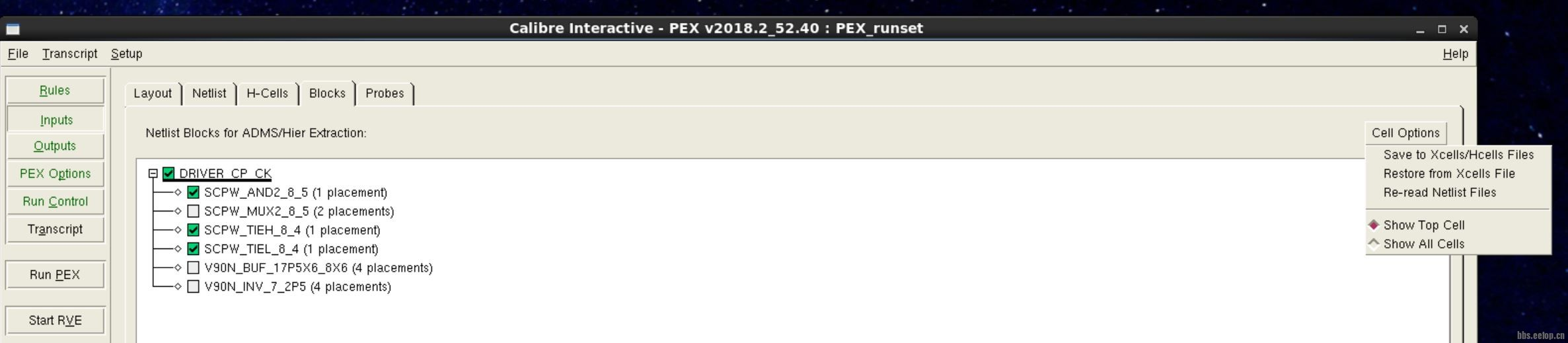

hecll和xcell,配合起来将你指定模块屏蔽起来,作为一个黑盒子,不抽寄生。

gate level + 如图片所示可以生成hcell文件和Xcell文件(决定你要屏蔽的子模块,两文件格式一样的),PEX生成的DSPF文件会不提子模块的RC,在DSPF文件的最后,会include子模块的前仿网表。

-

pex的图形界面include这个命令PEX Extract Exclude [LAYOUTNAME] [SOURCENAME]。hcell和xcel也是这个意思,不过一个是文件,一个是命令,可以参考svrf手册和calibre的xrc的手册

-

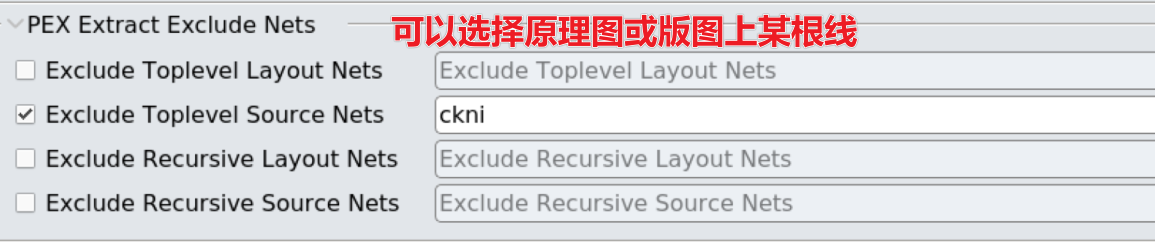

在 options 里面 选择 PEX Extract Exclude Nets 可以选择排除不需要的net(基于calibre22版)

EETOP上有个帖子提到:

使用Gate level提取方式加 输出calibreview格式,同时使用Xcell定义了不提取的模块电路。

结果发现提出的结果,直接用来仿真的话,内部那些模块电路好像不在netlist 里面,根本仿不出来正常的结果。

-可以先看看生成的calibre view 里有没有那些模块。如果是生成calibre view, cell map 里也得把这些模块加进去。

-你说的内部那些模块不在netlist里面------指的就是Calibreview里面没有那些模块。在Calibre Interactive and Calibre RVE,User's Manual里面找到了Creating a Gate-Level Calibre View,里面提到了Create the cellmap file。

Debug

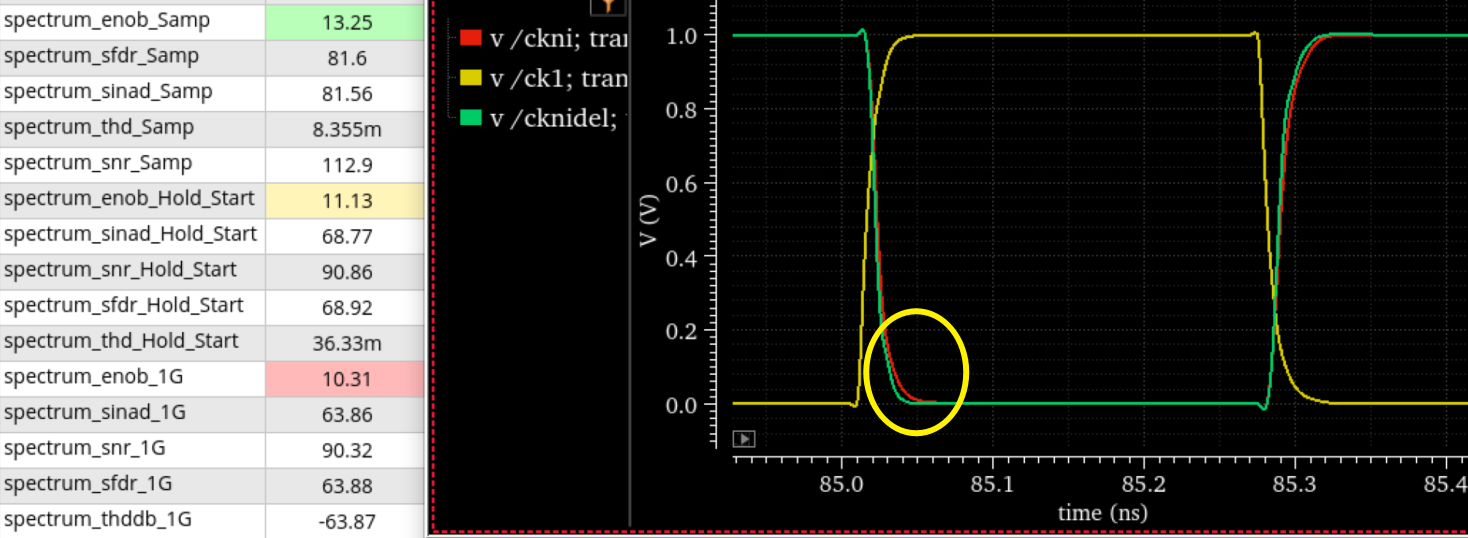

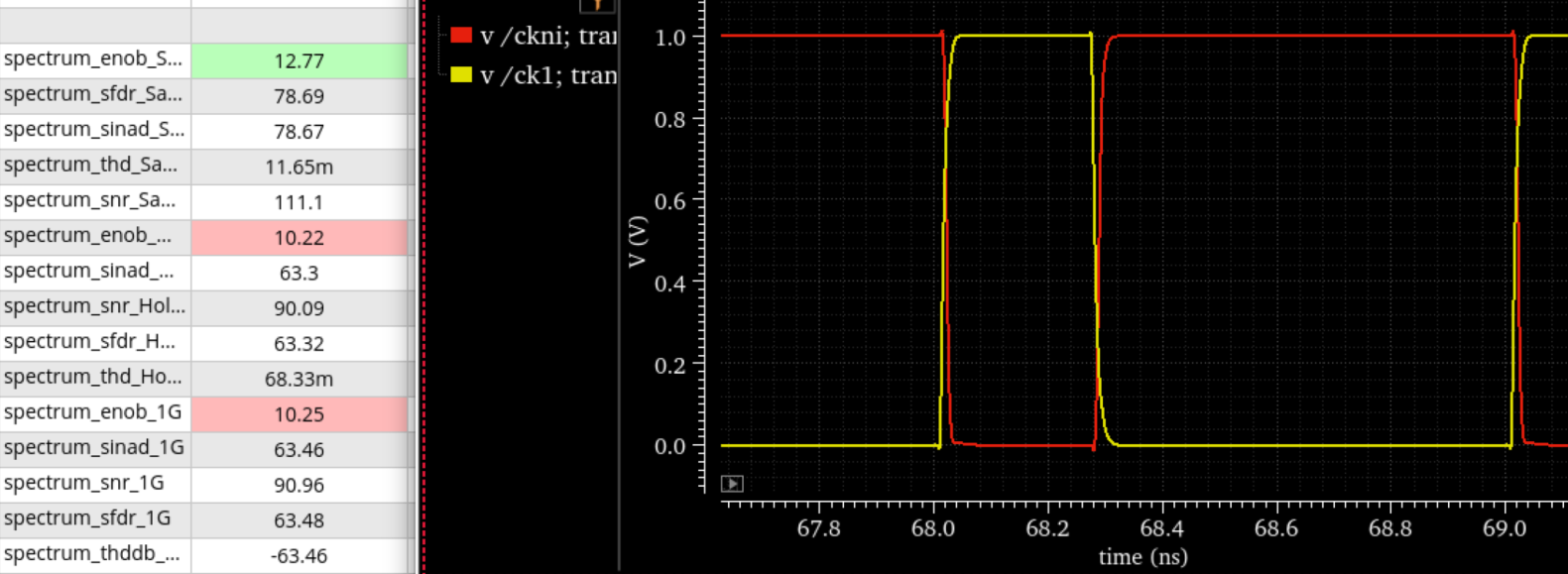

【Step1】采用方法三exclude原理图中ckni这条线,后仿真结果时钟正常,性能一般(先不管)。

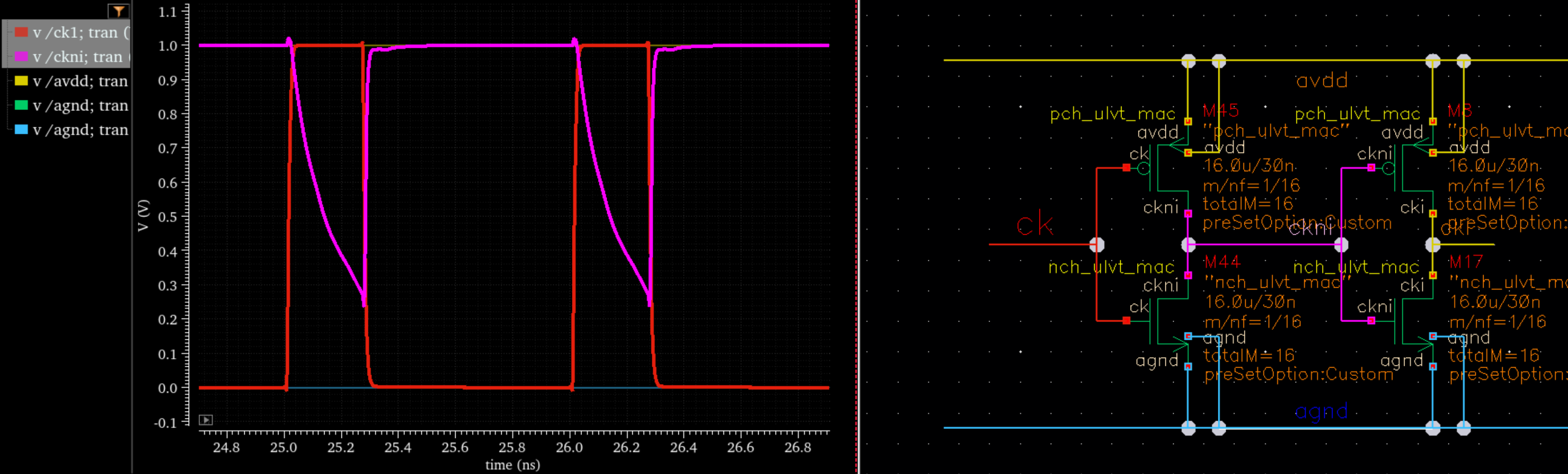

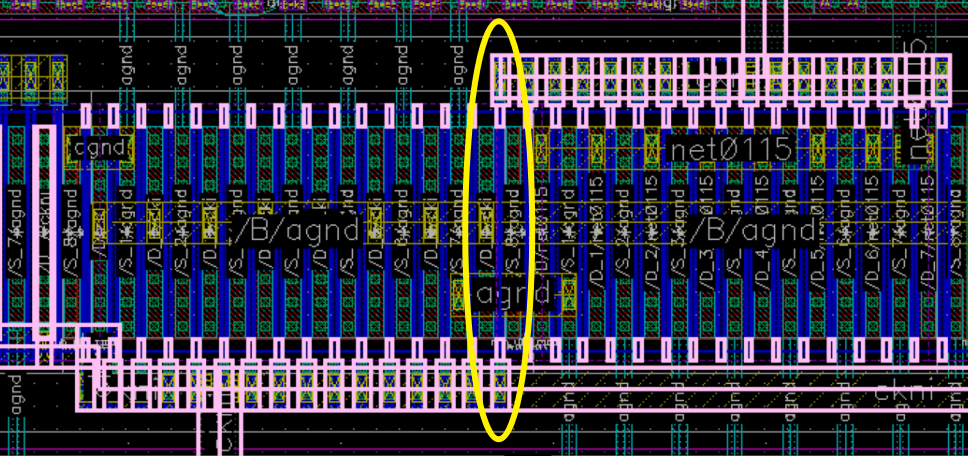

猜测可能是同一个时钟信号,不想跨晶体管接所以用同一个栅极上下打孔,导致信号必须经过栅电阻。

结论:一般不会像下图这样操作,这里你可以想象是加了一根poly电阻,也有见过用gate当走线的,小工艺用不太好吧。poly阻抗很大。

【Step2】