打工人日报#20251005

知识点

HDL 实例化调试探针流程

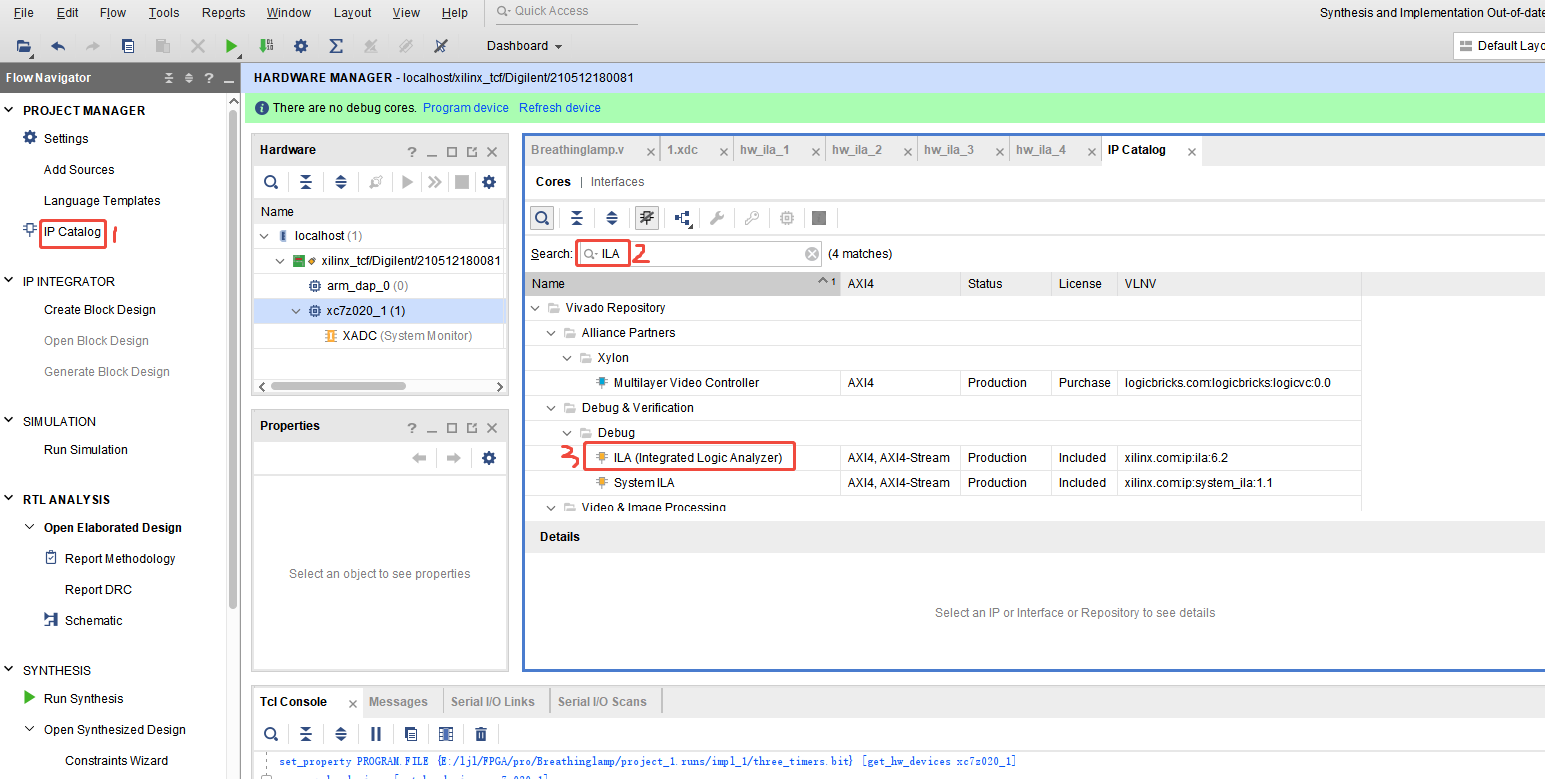

点击"Flow Navigator"窗

口中的"IP Catalog"按钮,

双击"ILA(Integrated Logic Analyzer)"会弹出"ILA IP"核的配置页面

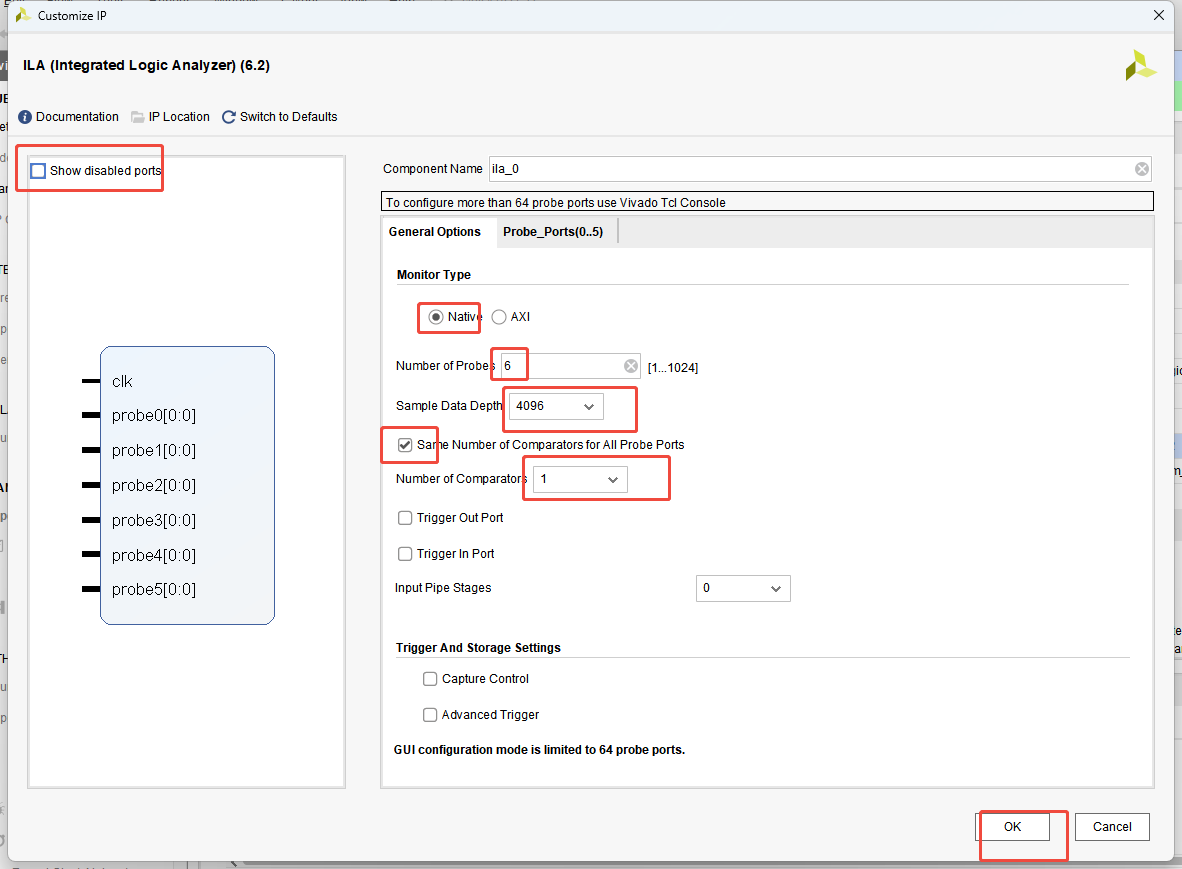

Documentation、IP Location、Switch to Defaults 三个设置

Documentation:IP 相关文档入口

- Product Guide:IP 手册查看入口

- Change Log:是 IP 版本更新记录

- Product Webpage:是 IP 相关介绍的网页版

- Answer Records:是与 IP 相关的 Xilinx 官方疑问解答记录网页

IP Location:设置 IP 的存放路径入口,点击出现如下图所示窗口,在窗口里可以通过点击"..."更换存放路径

Switch to Default:点击后所有的设置恢复到默认值。

Component Name:设置生成 IP Core 的名称

General Options(常规选项)

:ILA 探针接口类型设置,ILA 探针接口有两种类型,Native 与 AXI。Native 是普通接口模式;AXI 是 AXI 接口模式,用于调试 AXI 接口信号。Native 通常是用来测量电平或一定位宽信号,AXI 就比较明显了直接测量 AXI 总线的信号。

Number of Probes:探针数量设置,在 GUI 界面最大可设置 64 个,如果需要调试的内部信号超过 64个,可以通过 TCL 脚本去生成 IP Core

Sample Data Depth:采样数据深度,设置的数值越大,采样的数据越多,看到的波形数据越多

Same Number of Comparators for All Probe Ports:这里是设置相同探针接口的 Comparators 的个数

Trigger Out Port:触发输出端口,可用于 ILA 模块的级联或一些高级功能,

Trigger In Port:触发输入端口,可用于手工设置添加触发信号或进行 ILA 模块的级联或一些高级功能,

Input Pipe Stages:设置待探测信号打拍次数

Trigger And Storage settings:触发器和存储设置。

Capture Control:捕获控制,支持基本触发(时间点捕获)外的捕获类型,比如信号变化的间歇捕获。

Advanced Trigger:高级触发,该模式下可以创建和使用复杂的触发序列。如果这里勾选,可在调试查看波形窗口进行对 Trigger mode 的设置;如果不勾选,后面有关 Trigger mode 就不可修改。

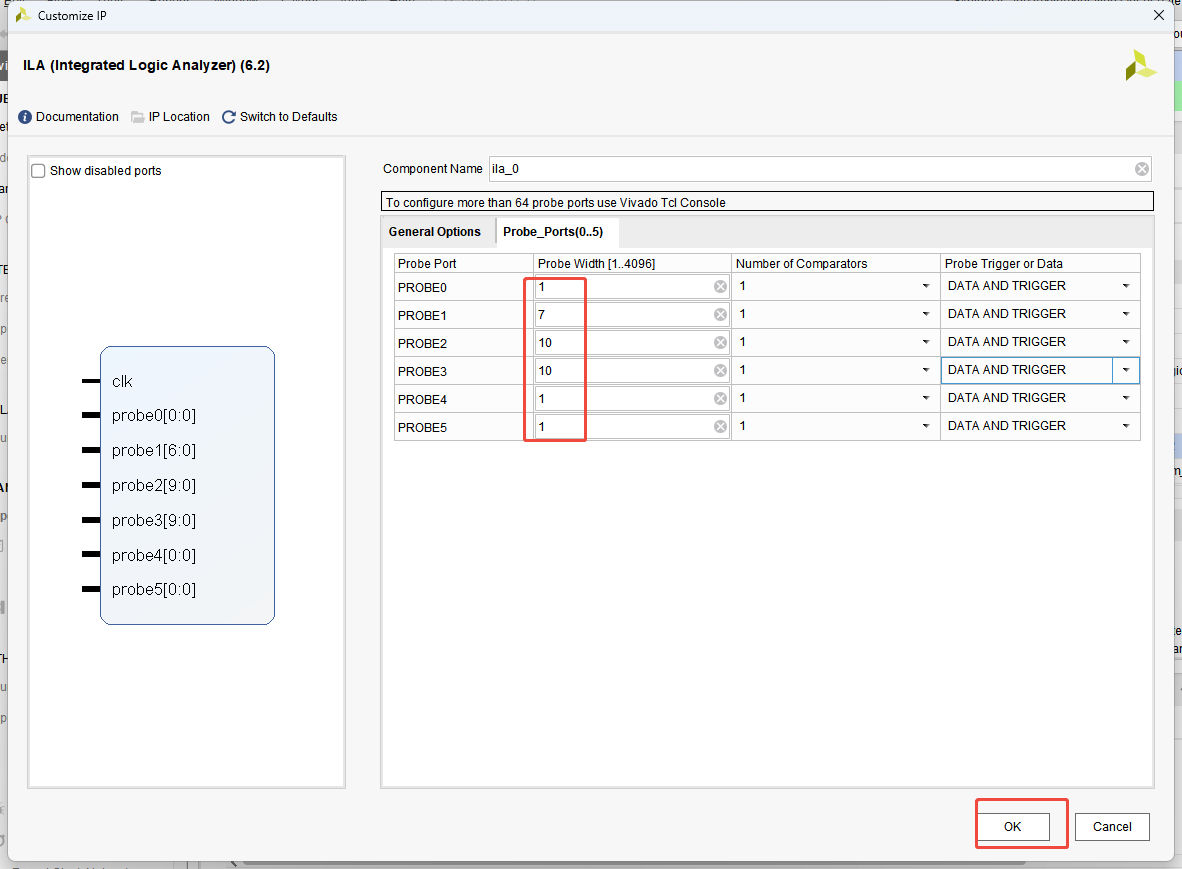

Probe Port:探针

Probe Width:设置探针信号的位宽,范围为[1~4096]。

Number of Comparators:前面没有勾选,这里不可设置

Probe Trigger or Data:对探针设置触发器或数据,

DATA AND TRIGGER:既是数据又可作为触发条件;

DATA:仅作为数据,不可作为触发条件;

TRIGGER:仅可作为触发条件。

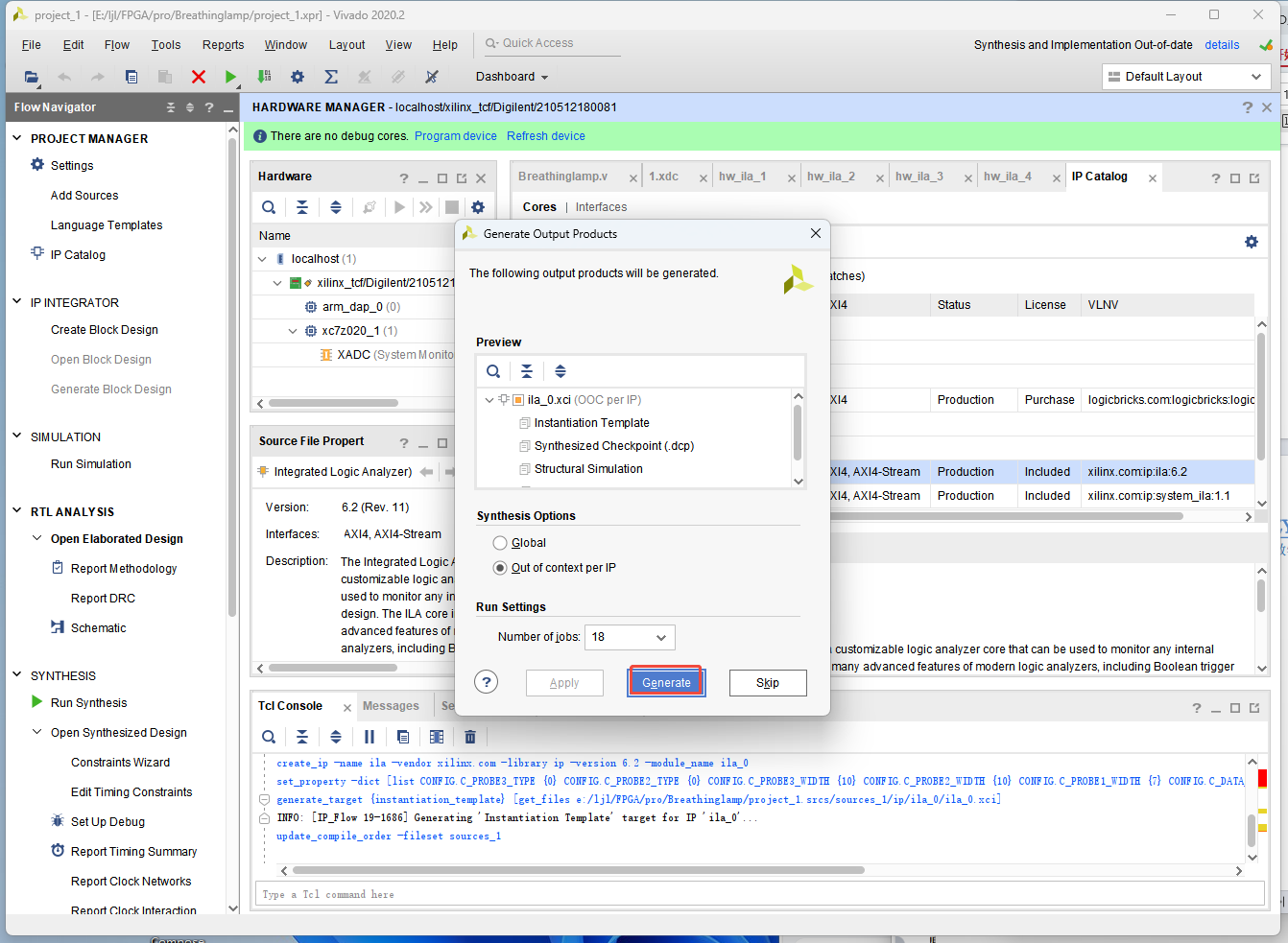

开始为 ILA IP 核生成输出文件

选择的是 Out of context per IP,简称 OOC

OOC 模块只会在综合顶层之前被综合一次,这样在顶层的设计迭代过程中,OOC模块就不必跟随顶层模块而一次次产生相同结果的多余综合了,所以 OOC 流程减少了设计的周期,并消除了设计迭代

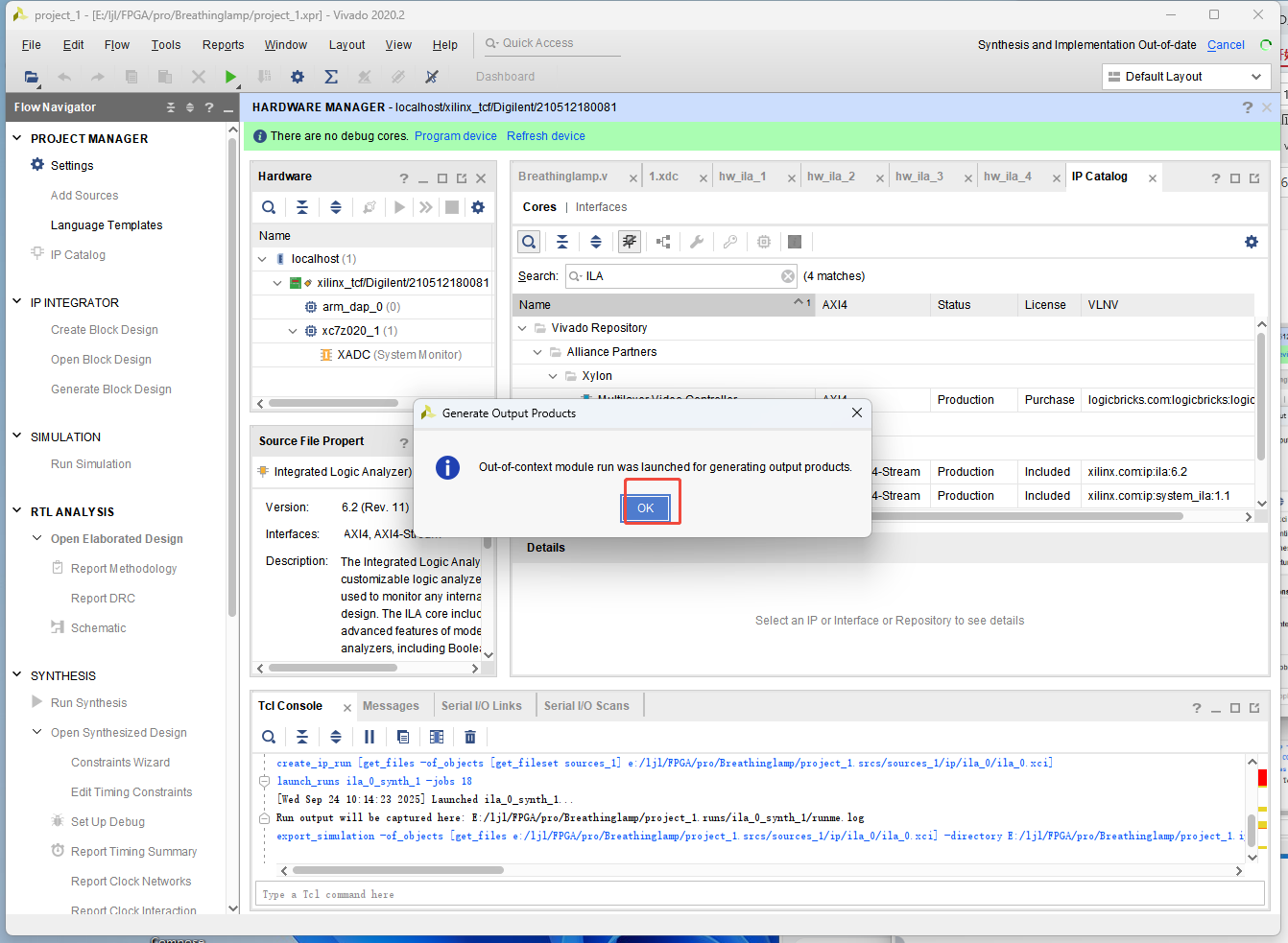

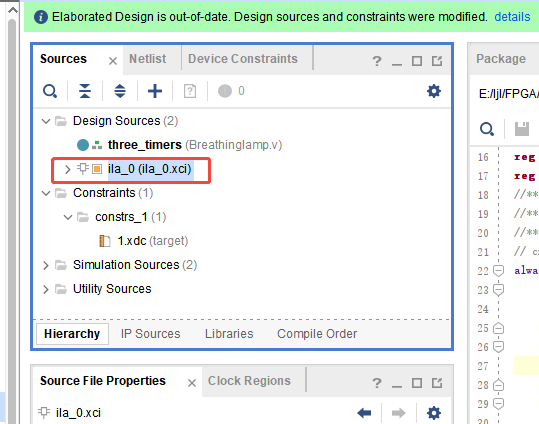

OOC 综合完毕之后

可以在"Source"窗口中看到已经出现了 ILA IP 核

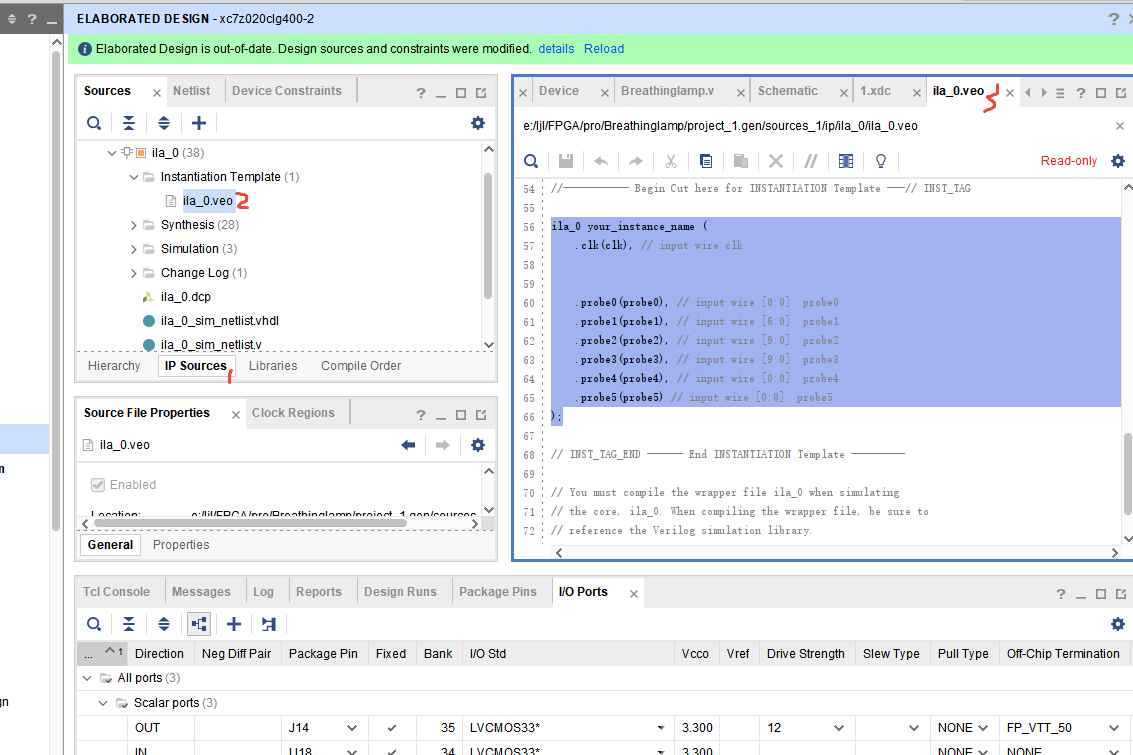

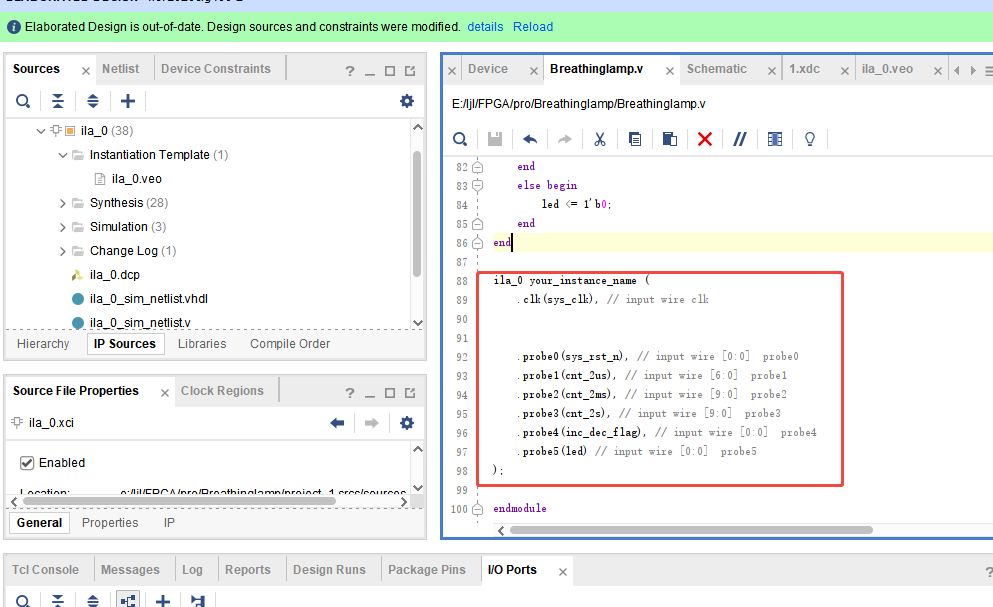

将其例化到顶层的 HDL 代码中

将图红色方框中的模板代码复制并粘贴到 XXX.v 顶层 HDL 代码中

ila_0 your_instance_name (

.clk(sys_clk), // input wire clk

.probe0(sys_rst_n), // input wire [0:0] probe0

.probe1(cnt_2us), // input wire [6:0] probe1

.probe2(cnt_2ms), // input wire [9:0] probe2

.probe3(cnt_2s), // input wire [9:0] probe3

.probe4(inc_dec_flag), // input wire [0:0] probe4

.probe5(led) // input wire [0:0] probe5

);例化 ILA IP 核的代码

保存源文件之后就可以直接综合并实现设计,最后生成比特流,然后将比特流下载到FPGA中,并对信

号进行在线观察。至此,我们就成功地使用"HDL实例化调试探针"方法将ILA IP核添加到了设计中

怎么查看,请关注明天的内容。

阅读

《杀死一只知跟鸟》

第九章 黑人 辩护 过节 大人 偷听