mem在设计中一般都会用到,最终在fpga中会被综合成3种RAM,第一种是寄存器搭建成RAM,第二种是DRAM,第三种就是BRAM。这三种你是可以指定的,具体怎么指定或者什么时候生成什么ram比较好在我之前的文章Synaplify综合的常用命令(1)https://blog.csdn.net/weixin_39896700/article/details/129280066中有详细的介绍。今天要说的是一个很细节的东西,也是生成的最多的BRAM,并不是你指定了就一定会成功的。

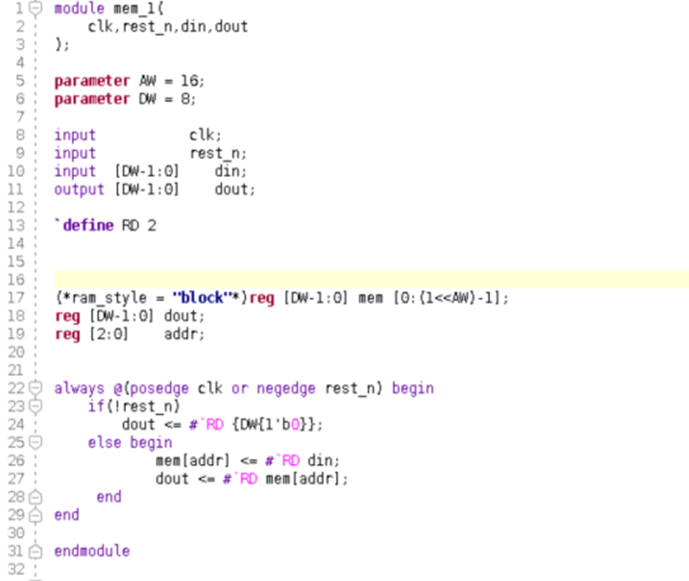

指定格式顺带一下,指定的格式是在申明mem的前面用括号去注释(*ram_style="block")reg [DW-1:0] mem[AW-1:0];

但是要注意一点,就是要想综合成BRAM必须是同步复位,因为BRAM不支持异步复位,所以如果你用了异步复位是综合不成BRAM的。如下图我的代码是异步复位,而且我也指定了综合成BRAM:

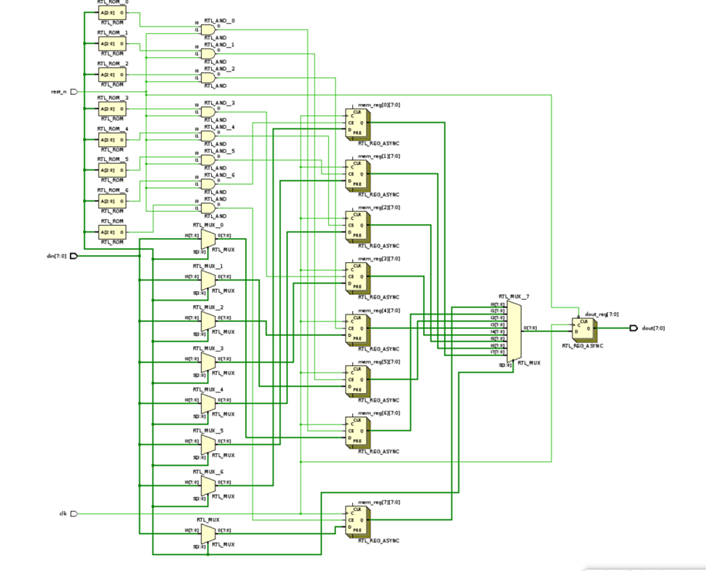

综合完成之后,打开电路图,可以看到,全是寄存器搭建的,没有综合成BRAM。

从资源当中也可以看到:

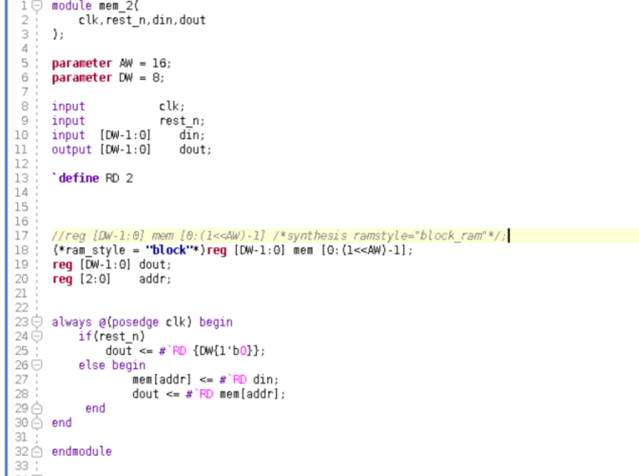

换一个同步复位的写法:

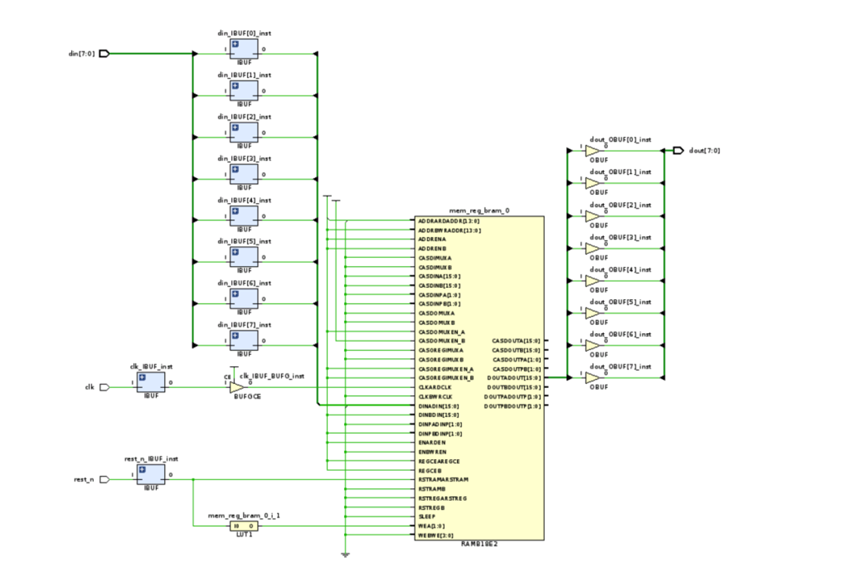

打开电路图:

可以清楚的看到这是一个BRAM,好看多了,这是FPGA的专用资源器件,也不会占用lut。打开资源报告查看:

可以很清楚的看到综合成了BRAM。所以并不是你指定了就一定能成功的。要了解器件的底层逻辑要求。不然你就会很迷茫的找不到答案。