1、概述

VPX-RFSOC-6U 是一款标准6U VPX 的信息处理板卡。板卡选用ilinx®Zynq®ultrascle+™RFSOC 和xilinx®virtex®ultrascale+™FPGA 来实现,具体型号为XCZU27DR-2FFVG1517I 和XCVU13P-2FHGB2104I;可完成AD 转换、DA 转换、数字变频、信号模拟、信号组合、波束合成和网络通信等功能。

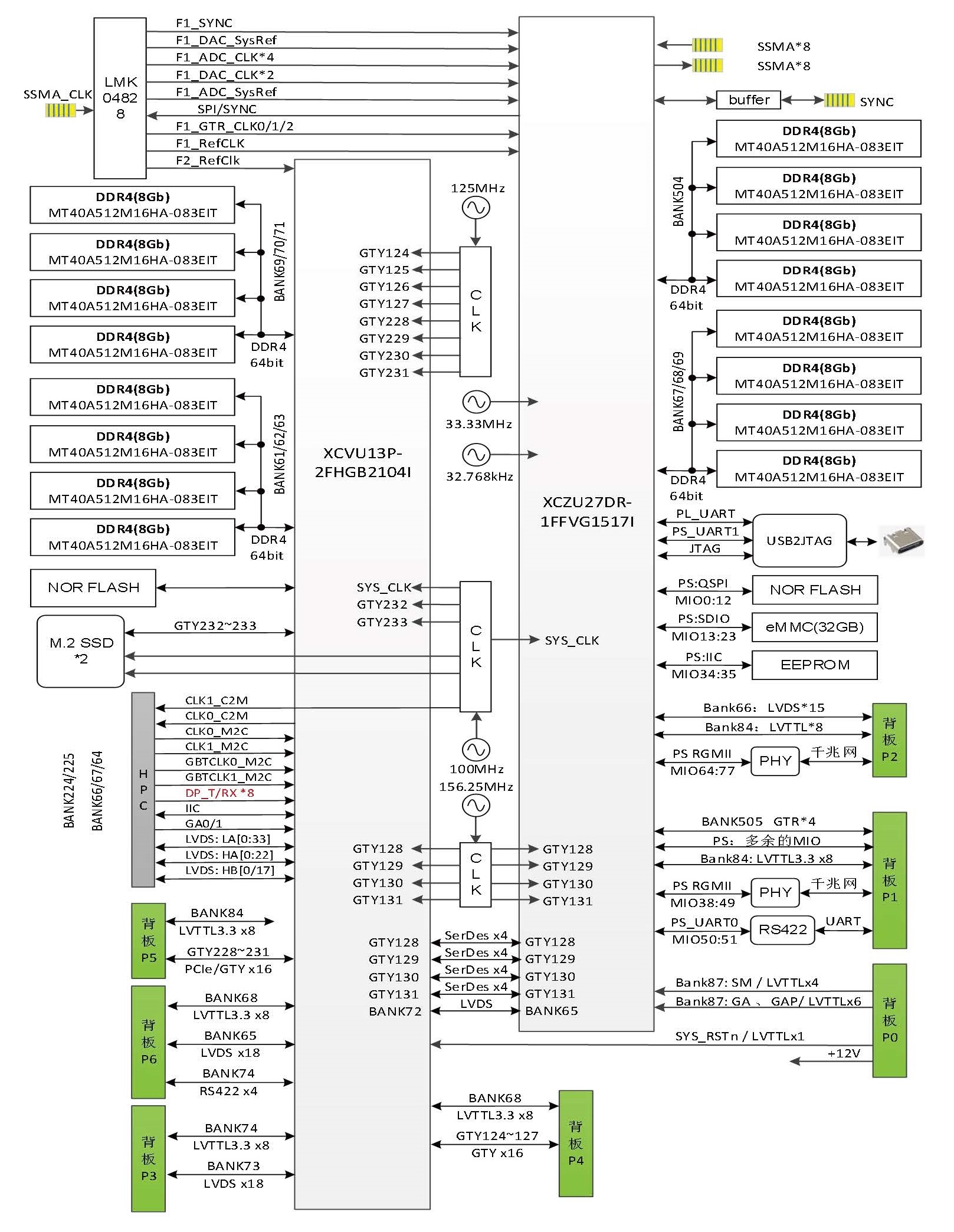

板卡总体框图如下图所示。

2、产品特点

丰富的接口资源和逻辑资源

一片Xilinx®Zynq®UltraScale+™ RFSoC,型号为XCZU27DR-2FFVG1517I;

一片xilinx®virtex®ultrascale+™FPGA,型号为XCVU13P-2FHGB2104I;

含8 路12-bit ADC

采样率可设置;

最高为4.096GSPS;

含8 路14-bit DAC

采样率可设置;

最高为6.554GSPS;

RFSOC 和FPGA 各外扩1G 的FLASH

支持外时钟参考

支持外部触发输入

3 技术参数

-

一片Xilinx®Zynq®UltraScale+™ RFSoC,型号为XCZU27DR-2FFVG1517I;

-

一片xilinx®virtex®ultrascale+™FPGA,型号为XCVU13P-2FHGB2104I;

-

FPGA 外扩2 组DDR4 存储器,每组4GB;

-

FPGA 外扩1Gb FLASH 存储器;

-

FGPA 外扩GTYx16 接口,从VPX-P1 连接器引出,GTYx16 可分割为4 组

GTYx4 或2 组GTYx8,所有GTY 接口支持PCIe3.1 协议;

-

FGPA 外扩LVDSx24 接口,从VPX-P2 连接器引出;

-

FGPA 外扩4 通道RS422 接口,从VPX-P2 连接器引出;

-

RFSOC 外扩2 组DDR4 存储器,每组4GB,分别在PL 和PS 端;

-

RFSOC 外扩1Gb FLASH 存储器;

-

RFSOC 外扩1 通道DP 显示接口,从VPX-P5 连接器引出;

-

RFSOC 外扩2 通道USB2.0 接口,从VPX-P5 连接器引出;

-

RFSOC 外扩3 通道千兆网接口,一路从前面板引出,2 路从VPX-P5 连接

器引出;

-

RFSOC 外扩1 通道RS422 接口,从VPX-P5 连接器引出;

-

RFSOC 含8 路12-bit ADC,采样率可设置,最高为4.096GSPS;

-

RFSOC 含8 路14-bit DAC,采样率可设置,最高为6.554GSPS;

-

外时钟/参考支持,可通过前面板的SMP 接口输入;

-

外触发支持,可通过前面板的SMP 接口输入或输出。

4、物理环境参数

尺寸:标准6U VPX

输入电压:DC 12V

功耗:≤100W

工作温度:-40℃~+70℃

存储温度:-45℃~+85℃

湿度:95%无冷凝

气压要求:海拔高度4500m 以下可正常工作

使用寿命:≥8 年