在高速数据交换、服务器加速卡、嵌入式系统里, PCIe 接口几乎是"必备武器"。但对于很多 FPGA 工程师来说,自己实现一条 PCIe 通道从零起步仍然很困难------涉及 TLP 层、BAR 映射、DMA 引擎、收发逻辑、时钟域交叉、PHY 配置...... 好消息是,有一个开源项目 LitePCIe 为你扫清了这条路。

✅ 项目简介

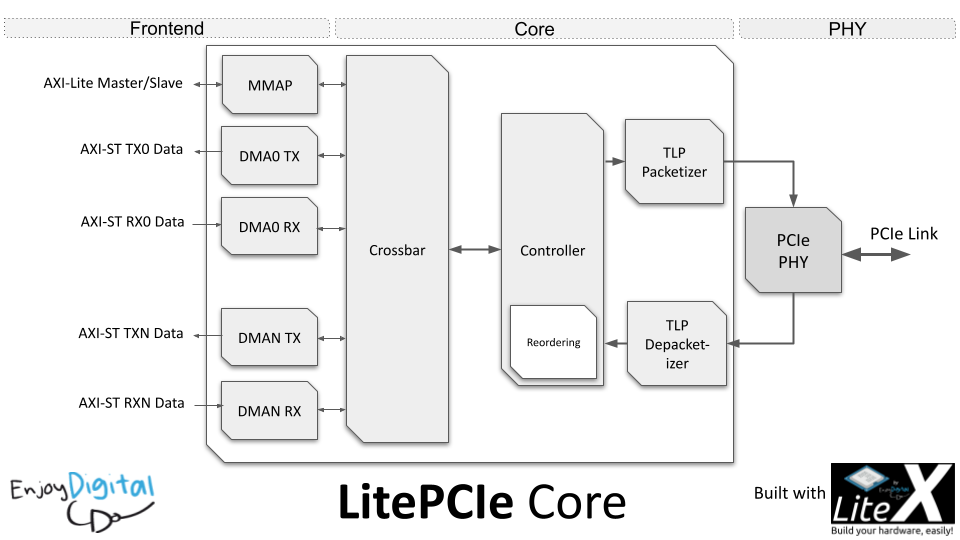

LitePCIe 是一个由 Enjoy‑Digital(https://github.com/enjoy-digital) 组织维护的"轻量级且可配置"的 PCIe 核心。它主要特点包括:

-

支持多种 FPGA 设备:例如 Xilinx 7 系列(可达 Gen2 x8)、UltraScale(+) (可达 Gen3 x16)等。

-

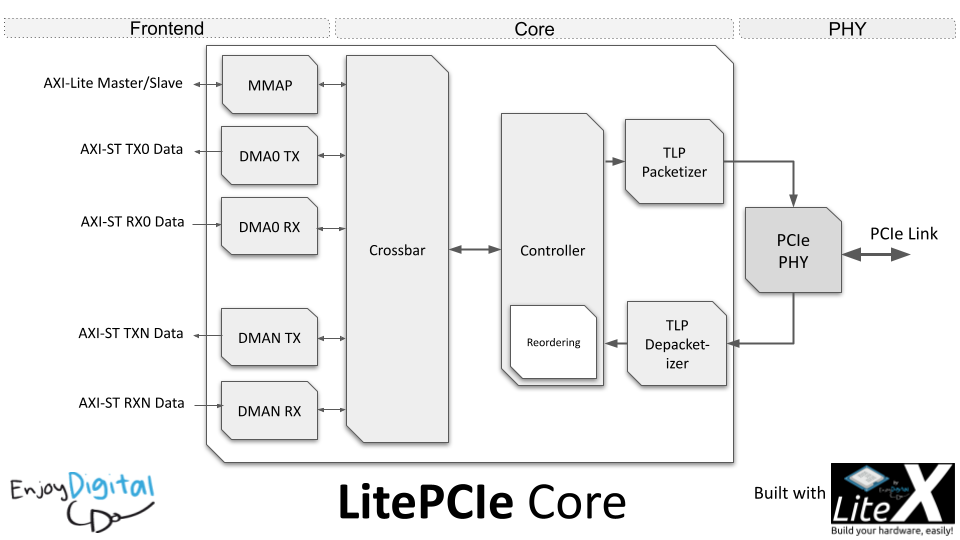

内置 TLP 层、重排序机制 (reordering)、MSI / MSI-X 支持、交叉开关 (crossbar) 结构。

-

支持 DMA(Scatter-Gather)、映射接口 (MMAP)、AXI/Wishbone 主/从等。

-

采用 Python + Migen 工具链描述逻辑,高度可配置,也可生成 Verilog 供传统 FPGA 流程使用。

也就是说,如果你要在 FPGA 上实现高速 PCIe 数据通道、构建高性能卡片或加速器,LitePCIe 绝对是一个"起点即战力"的开源方案。

🧱 架构亮点拆解

以下是几个核心技术亮点:

• PHY 接口支持

LitePCIe 支持如下 PHY 层:

-

Xilinx Ultrascale(+):高带宽、支持 Gen3、x16。

-

Xilinx 7 系列:支持 Gen2 x8。

-

Intel Cyclone5:支持 Gen2 x4。

这说明项目兼具"高端扩展性"和"入门门槛低"的优势。

• 核心功能层

包括 TLP 层、重排序、交叉开关、MSI 支持等,这些都是传统 PCIe 核中最难实现、但也是最关键的部分。LitePCIe 将其模块化、开源化,使 FPGA 工程师能够直接"拿来用",再在此基础做定制。

• 前端接口

支持DMA + Scatter-Gather、MMAP (AXI/Wishbone) 等方式进行数据读写。也就是说,这个核不只是为了 "连通 PCIe",更是为了让你 真正在 FPGA 内部做数据搬运/加速/交互。

• 开源工具链 &可生成 RTL

项目是用 Python + Migen 编写,用户既可以在 LiteX 生态中使用,也可以导出 Verilog 加入传统 FPGA 开发流程。对于国内团队来说,这意味着"开源 + 可定制 + 易迁移"。

• 架构说明

① LitePCIe 内部模块划分示意

**用途:**直观展示整个 LitePCIe 核心结构(PHY 层、TLP 层、DMA、跨总线等)。

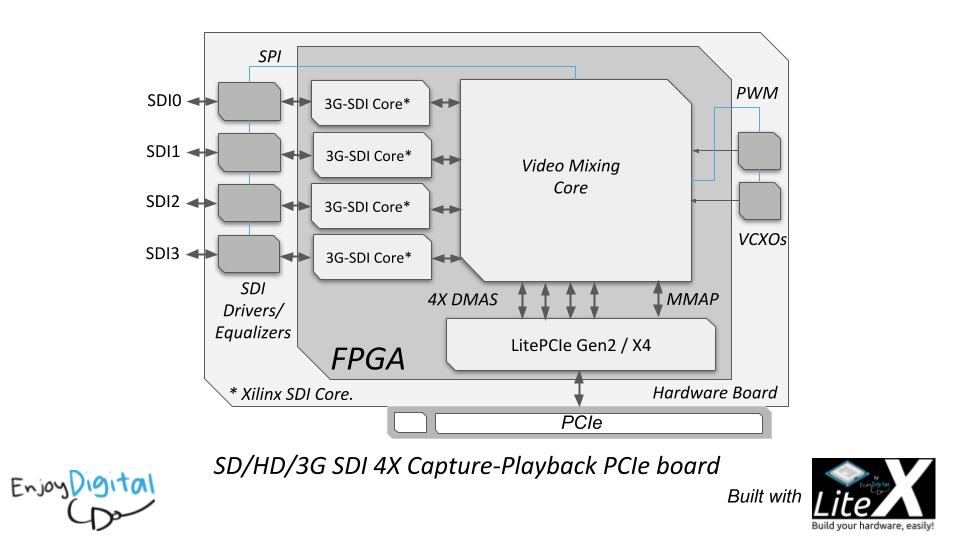

② LitePCIe + LiteX 平台生态图

**用途:**展示 LitePCIe 如何融入整个 LiteX 生态,与 LiteDRAM / LiteEth / LiteSDCard 等协同。

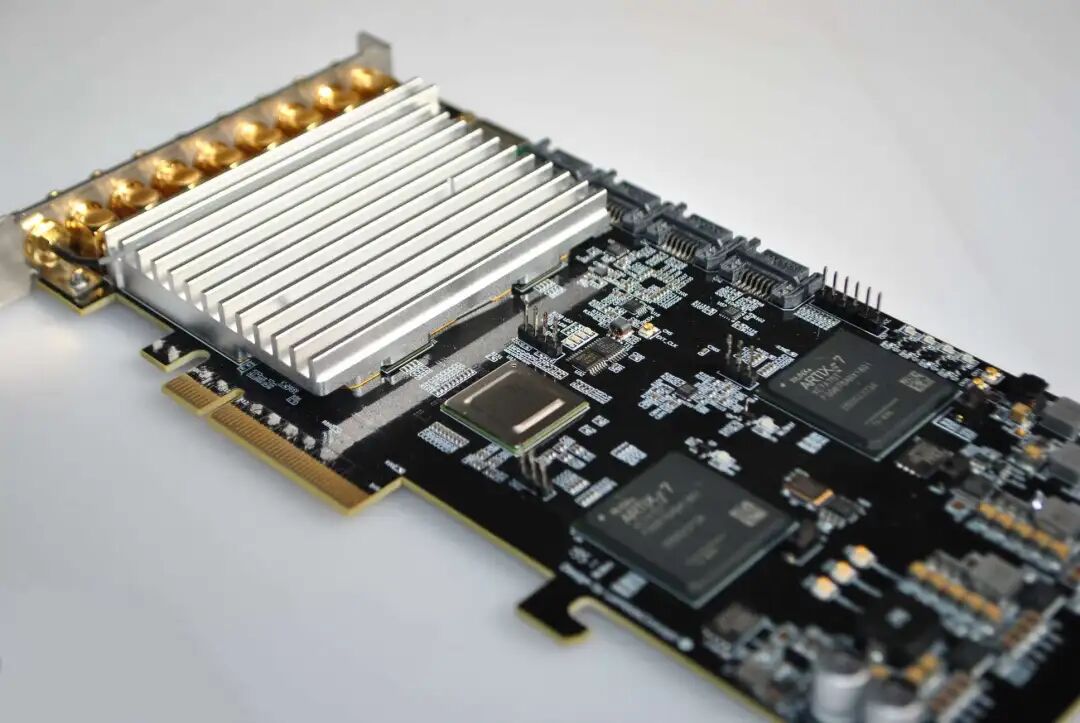

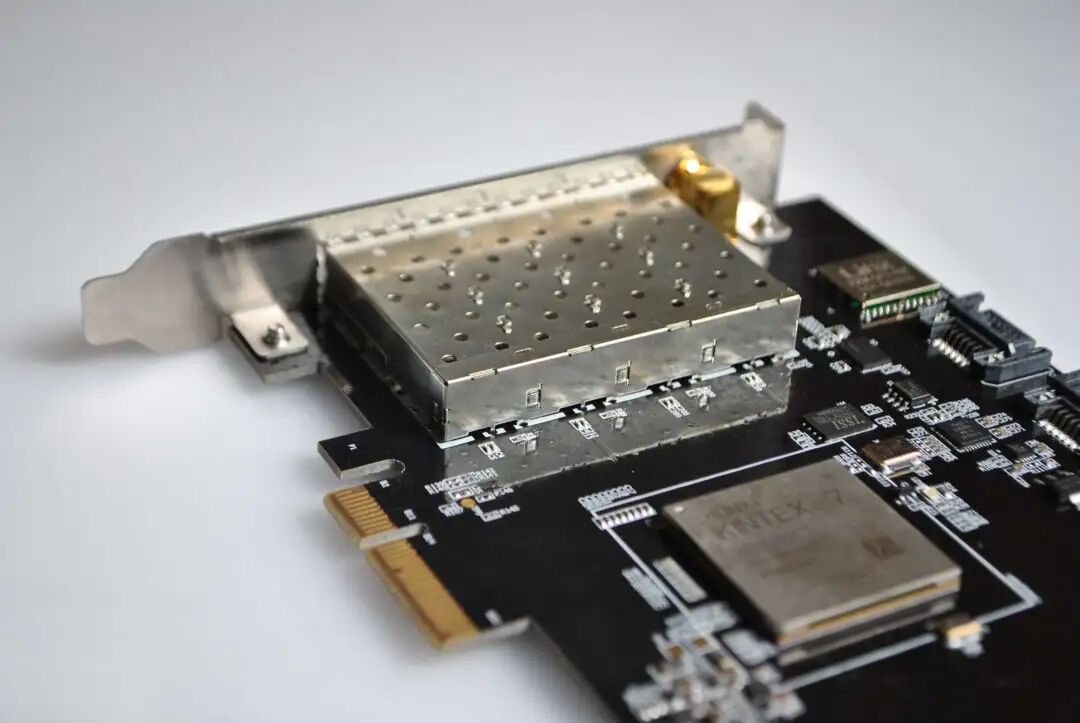

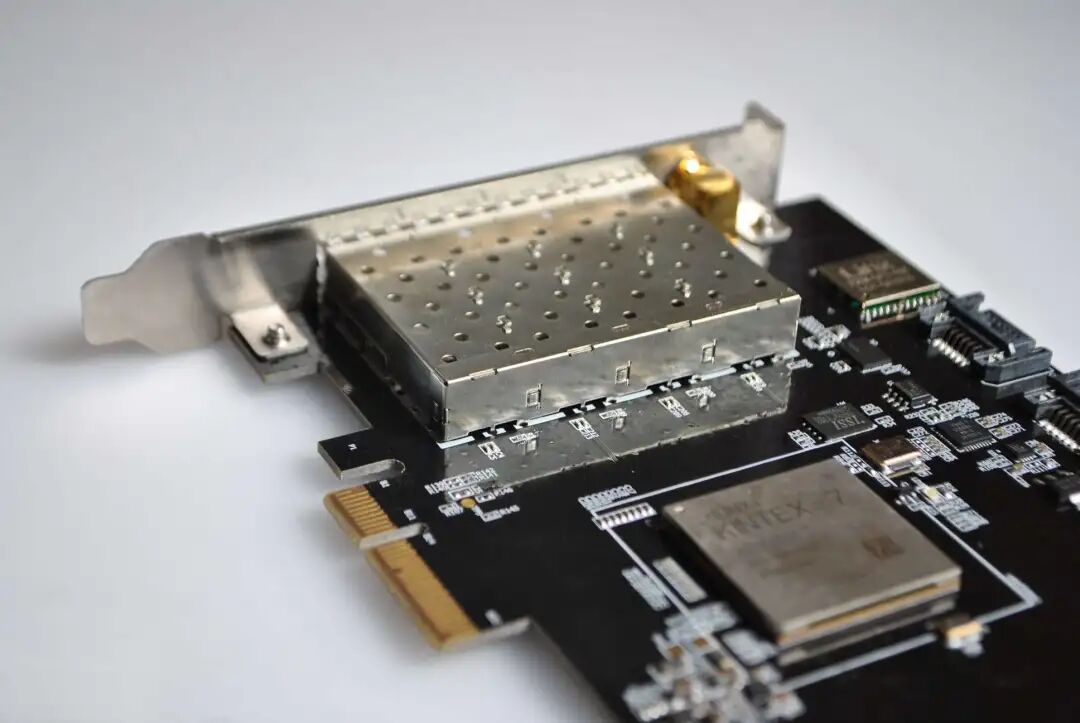

③ FPGA 板卡实拍图(测试板卡)

🌐 工程应用场景

以下几个场景特别适合用 LitePCIe:

-

高速采集卡/存储卡:FPGA 做数据预处理 → 通过 PCIe 发送给主机;

-

数据中心 FPGA 加速卡:例如 DPDK 数据包处理、网络卸载;

-

嵌入式系统中:FPGA 与 CPU 协作,通过 PCIe 实现高速交互;

-

教学与研究平台:用于学生理解 PCIe 协议、实践 FPGA 设计。

-

3G-SDI Capture/Playback board:

- SDR MIMO 2x2 board:

- SDR MIMO 4x4 board:

- SDR CPRI board:

🔍 小结

开源 PCIe 核意味着 不必从零开始设计 TLP/BAR/MSI 逻辑,能大幅降低难度。

支持 Python + Migen 描述,降低传统 HDL 门槛,更符合"软件化+硬件化"融合趋势(国内认可度不高)。

可以借鉴其模块化结构、平台适配方式、工具链迁移经验,助力国产 FPGA 生态建设。

LitePCIe 不仅是一个"开源 PCIe 核",更是一个"FPGA 开发者加速器"。

它让 PCIe 从难题变成可控模块,让你在 FPGA 设计里,把更多精力放在"算法/数据流"而不是"协议细节"。