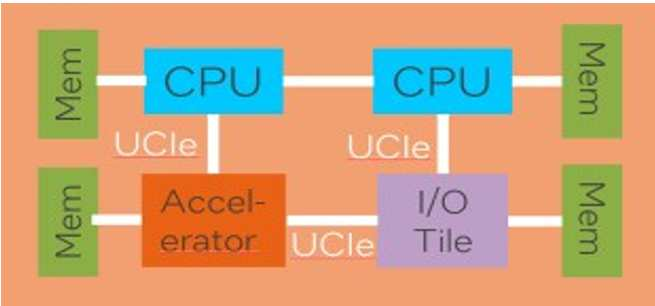

图1展示了由多个CPU裸片、加速器与I/O瓦片裸片通过UCIeA物理层和EMIB通道连接的SoC(片上系统)封装。该封装技术适用于高性能优化应用,因此通道距离短,互连需针对高带宽、低延迟及最佳能效特性进行优化。

图1 通过EMIB连接的多小芯片架构

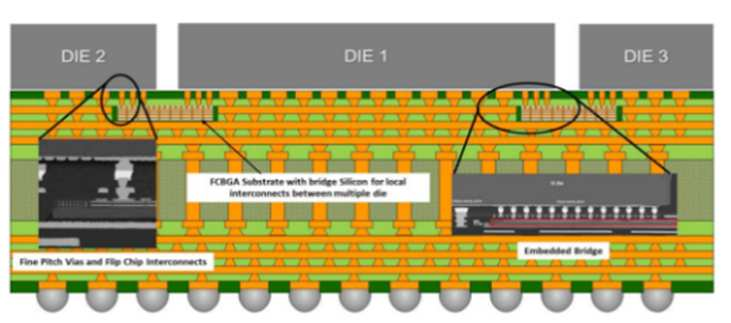

图2 EMIB架构

图2描述了EMIB架构的组成。超薄硅桥嵌入有机封装的上两层,并通过封装基板上的倒装焊盘与封装通孔连接。封装互连的主体仍采用传统有机封装互连技术。

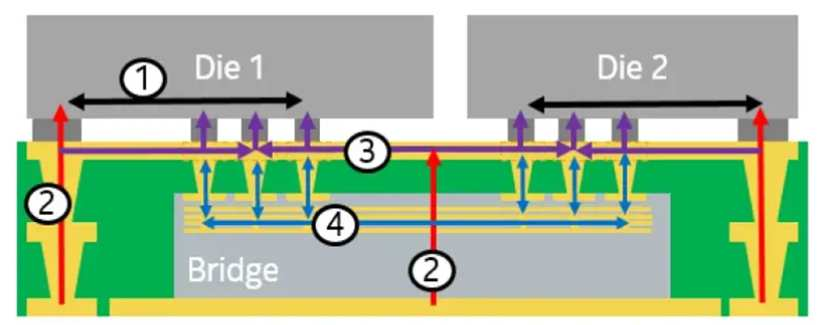

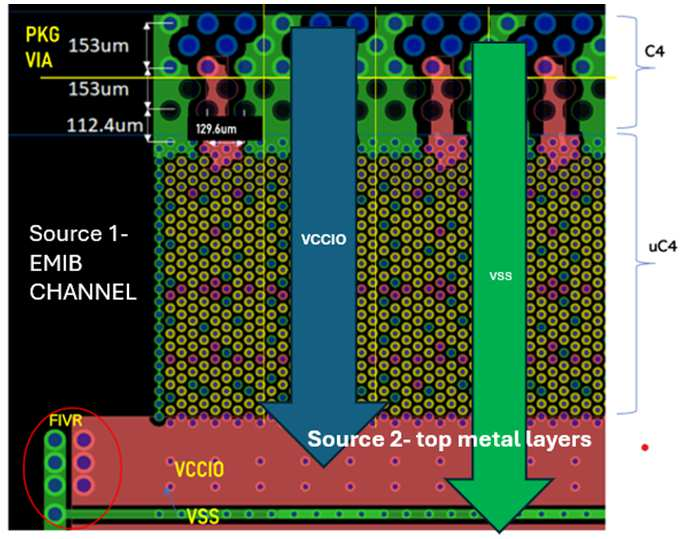

图3 EMIB与封装中的电源分布

图3展示了带有EMIB桥的多芯片封装电源分布,并突出显示了封装内的电源路径。图中可见,EMIB桥遮挡了物理层的直接电源连接,主电源通过路径2提供,地连接则在桥内通过路径4实现,包括封装表层。

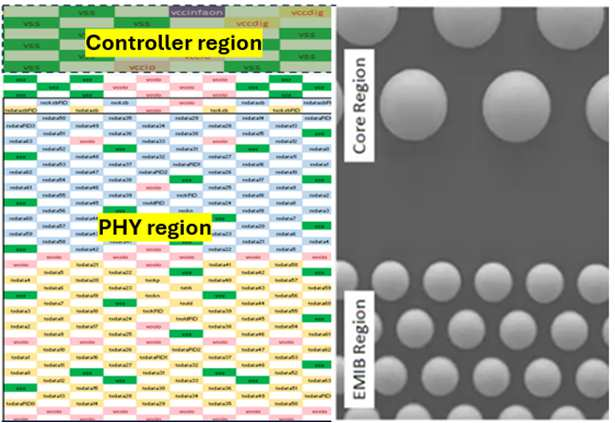

图4 UCIe 物理层凸点分布图

3D IC在电源传输与完整性中的挑战

3DIC的主要优势是高带宽、低延迟与低功耗,但器件密度增加与非对称封装也带来了电源传输的挑战。硅通孔(TSV)技术是3D集成的关键技术,其互连可提升性能与数据带宽,但也会因引入额外电阻与电感路径导致静态IR压升。电流从封装通过TSV流向顶部金属层,再经中层金属层分配到底层金属直至晶体管。TSV还需为顶部裸片供电,这使得静态IR压降成为关键挑战。

A. UCIeA凸点与电源传输路径

对于电源网格,C4凸点数量与间距是决定网格质量的关键因素。C4数量减少会导致电源噪声增加。图4展示了UCIeA物理层凸点分布及封装凸点与微凸点的热成像图。

控制器或核心区域采用松散间距的C4凸点,而物理层或EMIB区域则采用精细间距的uC4凸点。电源通过EMIB平面从核心区域传输至物理层区域。图5展示了封装平面层结构,其中物理层区域为uC4凸点,控制器区域为C4凸点。封装平面的电源仅通过顶部的C4凸点传输。

图5 封装平面至裸片的电源传输路径

电源完整性分析与解决方案空间

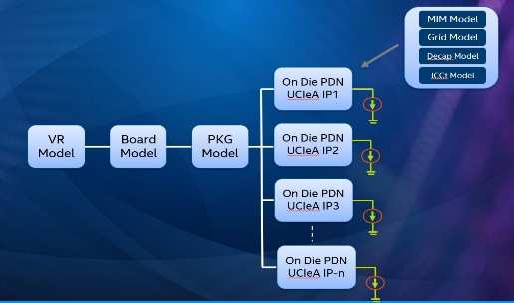

由于IP的严格噪声规范,需采用创新的电源传输网络(PDN)方法。图7展示了完整的PDN仿真设置,整合平台、封装与裸片模型以进行频域与时域分析。板级与封装模型通过2.5D电磁工具提取。裸片PDN建模需涵盖金属-绝缘体-金属(MIM)电容建模、裸片建模、电流分布生成及去耦电容模型。使用Ansys Redhawk生成MIM与片上PDN模型,并通过分布式SPICE模型从C4凸点至底层金属层进行建模。为缓解高密度电路同步开关引起的电源噪声,MIM电容是有效的PI解决方案。相较于非TSV技术,TSV技术因额外电阻与电感路径更难以满足噪声规范。

图7 PDN仿真方法

A. 静态分析

静态分析中,仿真设置需考虑平均电流,其值随时间变化。高速I/O电源轨的电源传输至关重要。对于采用传统数字电源轨的旧工艺节点,片上静态IR分析已足够,但高速I/O轨需评估封装平面电阻层引起的压降。PDN网状结构可建模为分布式RLC网络。连接基裸片与I/O裸片的UCIe物理层通过集成于封装表层的EMIB通道互连。静态仿真中,使用Sigrity等2.5D电磁工具提取封装与EMIB电阻模型。电流源来自封装BGA端口,电流汇点则为底层金属层,通过块电源分配注入平均电流。为提升精度,需针对高功耗区域进行多层次电流分布建模。

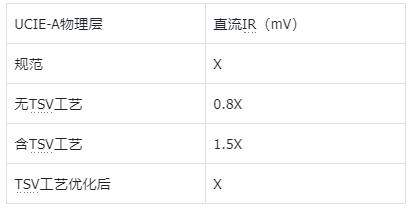

根据UCIeA协议,硅片的直流IR压降预算为X mV。基于最差工艺角、最大电压与温度条件,对含TSV与不含TSV的工艺节点进行静态仿真。无TSV工艺的静态IR压降为0.8X mV,而含TSV工艺的压升为1.5X mV,其中TSV与顶部金属层的累积压降占X mV。为降低TSV区域的静态IR压降,采用更宽的顶部金属层以分流电流,优化TSV映射/矩阵布局,并增加顶部金属层数量。通过多次仿真,累积压降减少至0.5X mV。

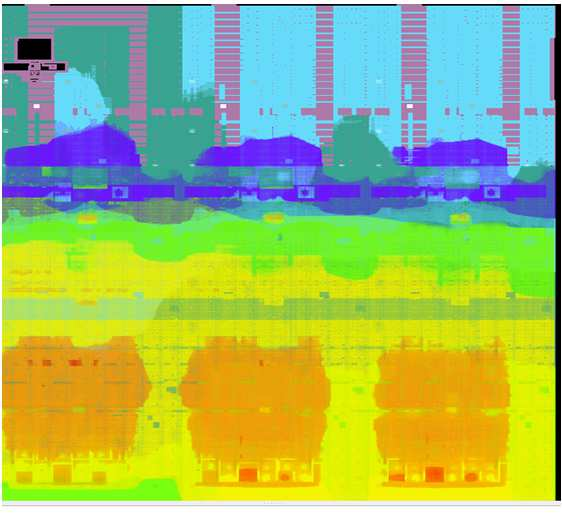

图8 UCIeA X3模块物理层静态IR压降分布图

如表1所示,IR压降分布显示,由于主电源位于通过TSV接收C4电源的控制器区域,电流汇点分布于物理层,压降从顶部至底部边缘逐渐增大。

表1 IR规范与结果

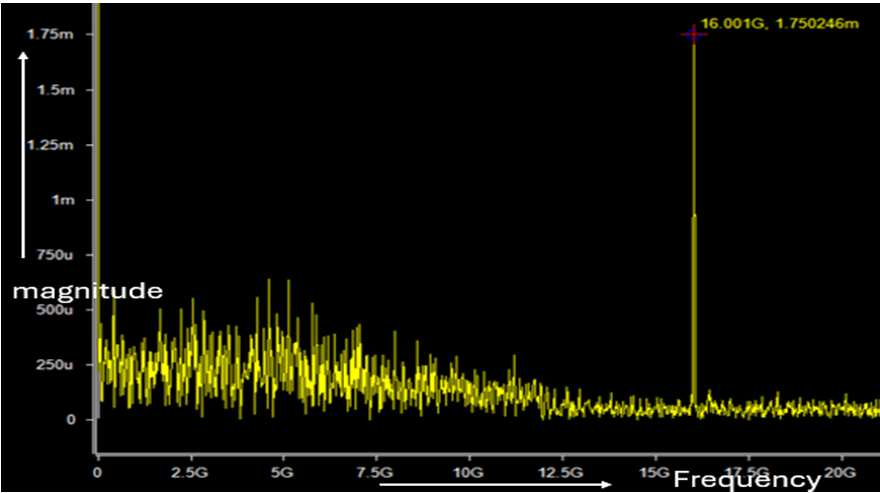

B. 频域分析

为优化系统噪声与源至凸点的电压压降,需在宽频范围内整合裸片、封装与板级模型进行频域分析。高频段(>100 MHz)的PDN响应受片上MIM电容影响。通过分析各模块电流分布的频率响应,确定信号内容的主要频段。图9展示了某发送模块的电流分布频率响应,其主要内容位于16 GHz频段。在此频段,MIM与MOS电容结合PDN路径环路电感的降低可有效抑制噪声。

UCIe 物理层的关键供电噪声目标阻抗为4mΩ。通过调整裸片(物理层、核心)与EMIB内的MIM与MOS电容进行交流分析。交流仿真中施加1A电流,按公式(1)绘制随频率变化的电压曲线。图10显示,通过片上与EMIB增加约10倍MIM电容,目标阻抗4mΩ得以满足。

裸片MIM电容为1X,片上SOC侵占的MIM电容增加至2X,而来自6模块桥电容的MIM电容为10X。

图9 发送模块电流分布频率响应

图10 不同电容组合下的阻抗变化

C. 瞬态分析

对于UCIe等高速I/O,需满足峰峰值噪声(Vnoise pk-pk)、最小电压(Vmin)与最大电压(Vmax)等瞬态规范。公式展示了如何根据图11的电压波形计算Vmin与Vmax:

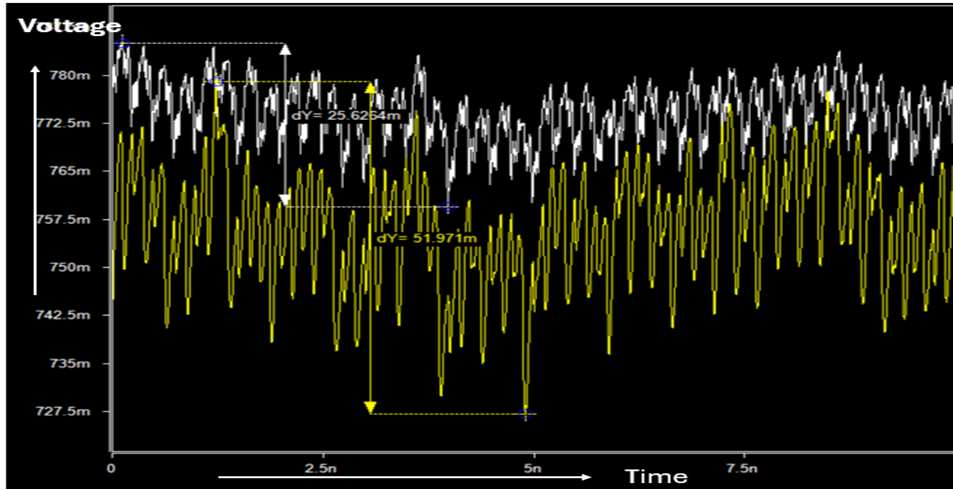

为评估EMIB、裸片与侵占电容对稳态峰峰值噪声的影响,进行瞬态仿真。图7显示,考虑EMIB电容后,下冲与峰峰值噪声显著降低。根据UCIeA标准,峰峰值噪声规范为40mV。通过集成封装、裸片与EMIB的解决方案,峰峰值噪声从51mV降至25mV,降幅达50%。

图11 显示噪声的电压波形

结论

上面探讨了在3D电源传输流程中,TSV布局与裸片间EMIB硅桥对UCIe I/O电源传输与完整性的挑战与解决方案。通过优化电源网格布线及TSV布局,满足了关键IR规范,避免了网格重新设计。通过片上与EMIB的MIM电容优化,改善了供电噪声、目标阻抗与下冲,最终满足IP规范。

往期推荐

高算力芯片中MiM/DTC/ISC几种去耦电容对电源完整性的应用分析

面向HPC平台应用的HBM电源完整性/信号完整性分析与设计方法

在CoWoS平台上采用DTC电容器的Logic-HBM2E电源完整性设计