主线任务:基于赛恩斯FPGA芯片的硬件开发版以及VR的软件的使用及开发流程

一、创建文件

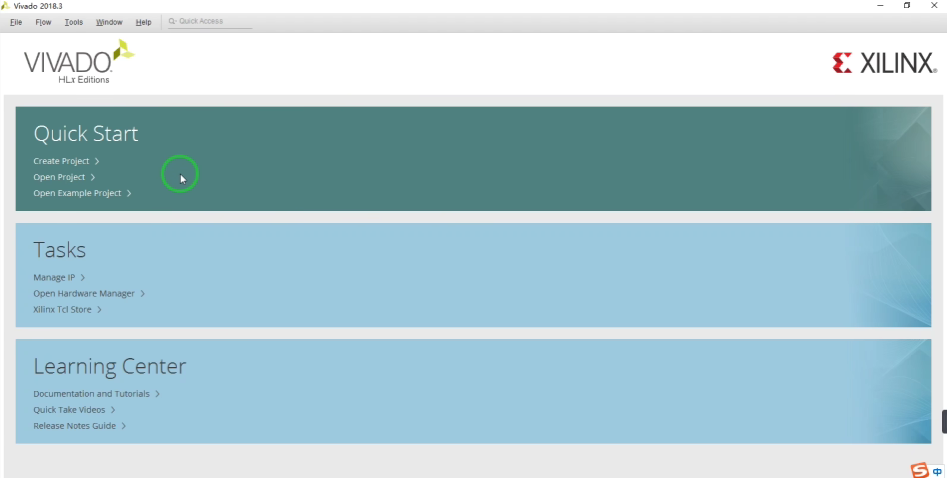

学习和使用赛恩斯的FPGA开发所使用的软件为Vivado 2018.3

第一栏是快速开始目录(第一个是创建新工程,第二个是打开已有工程,第三个是打开示例工程)

第二栏是基本任务

第三栏是学习中心网站,会提供官方的学习资料

点击 Create Project后会弹出一系列选项卡,每个选项卡来完成一个或多个功能的设置与选择

第一页选项卡是对于创建新工程功能的简单介绍,直接点击"Next"进入下一页即可

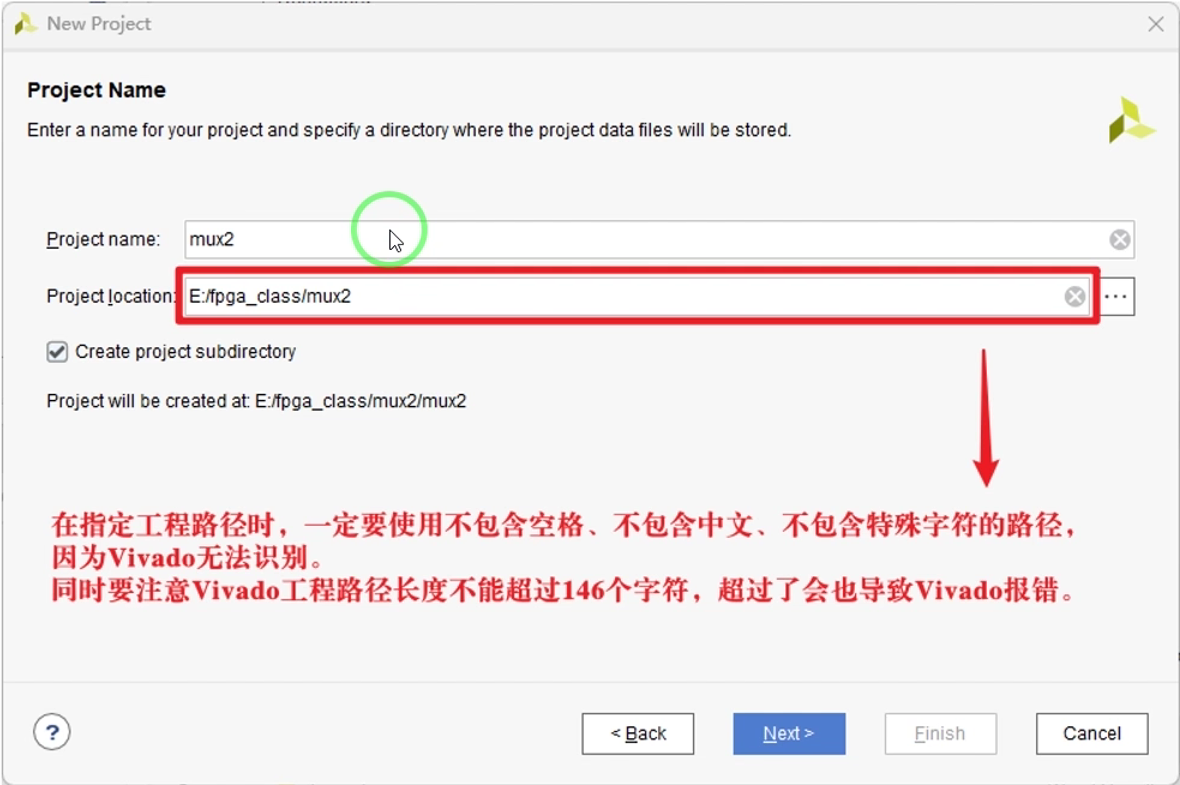

第二页是输入工程名称Project name,取名时最好有一定的实际意义,这里的mux2是二选一多路器,它是FPGA中最简单的电路模型,Project location是存放工程文件的路径,勾选Create project subdirectory选项,软件就会在指定的Project location位置的文件夹下新建一个和Project name一样的文件夹。

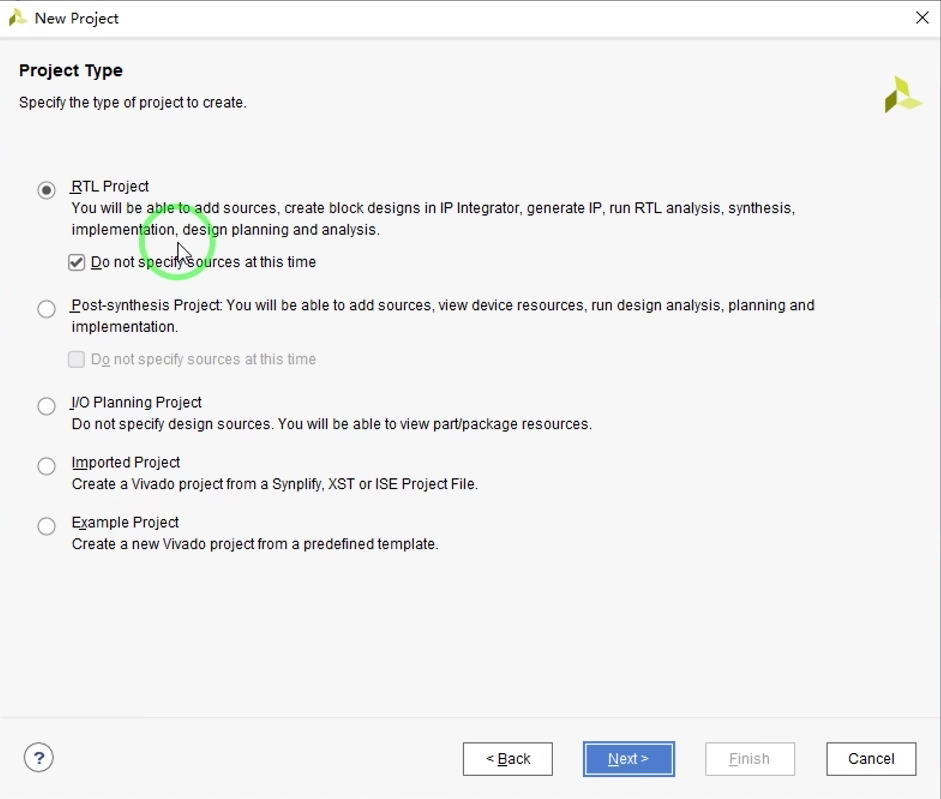

第三页是选择创建的工程类型,选择第一个RTL Project即可。

勾选第一个选项表示不需要添加已有的设计源文件、源代码。

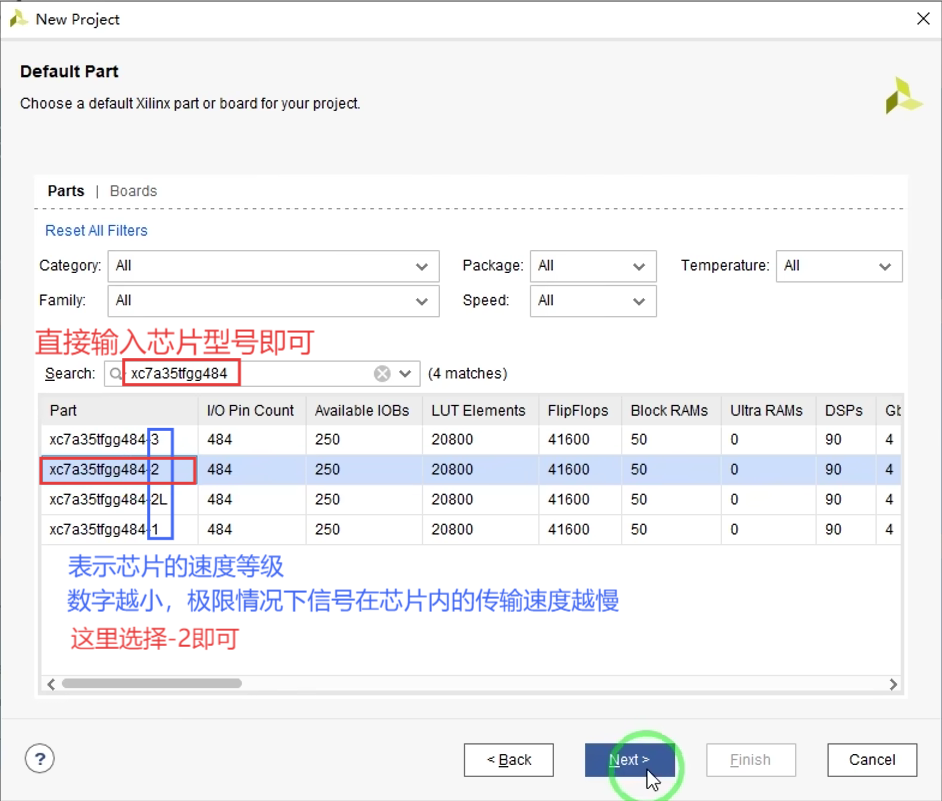

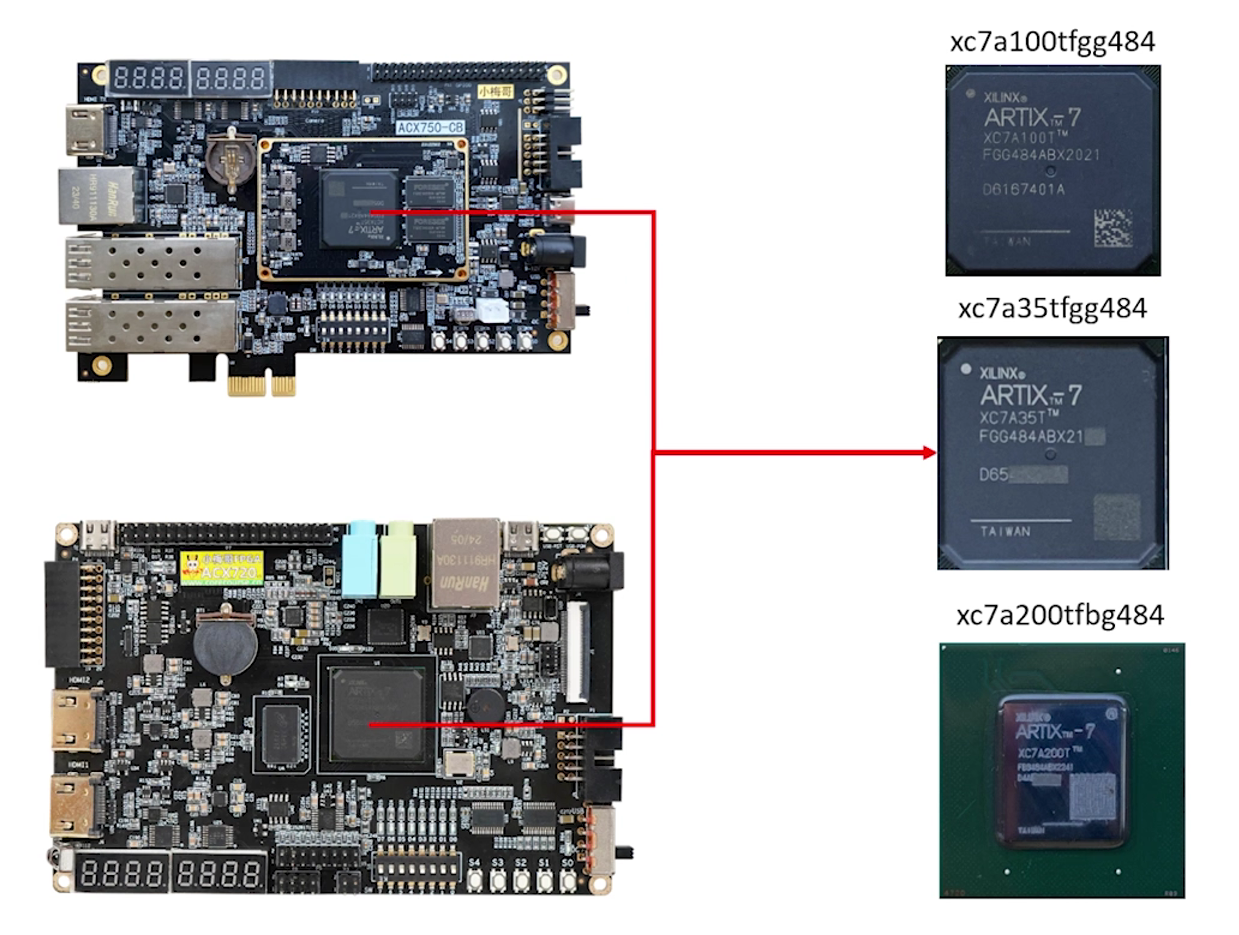

Default Part页面是选择器件型号的,即FPGA开发板上芯片的具体型号

根据购买的开发板选择对应的芯片型号(此处选择xc7a35tfgg484)

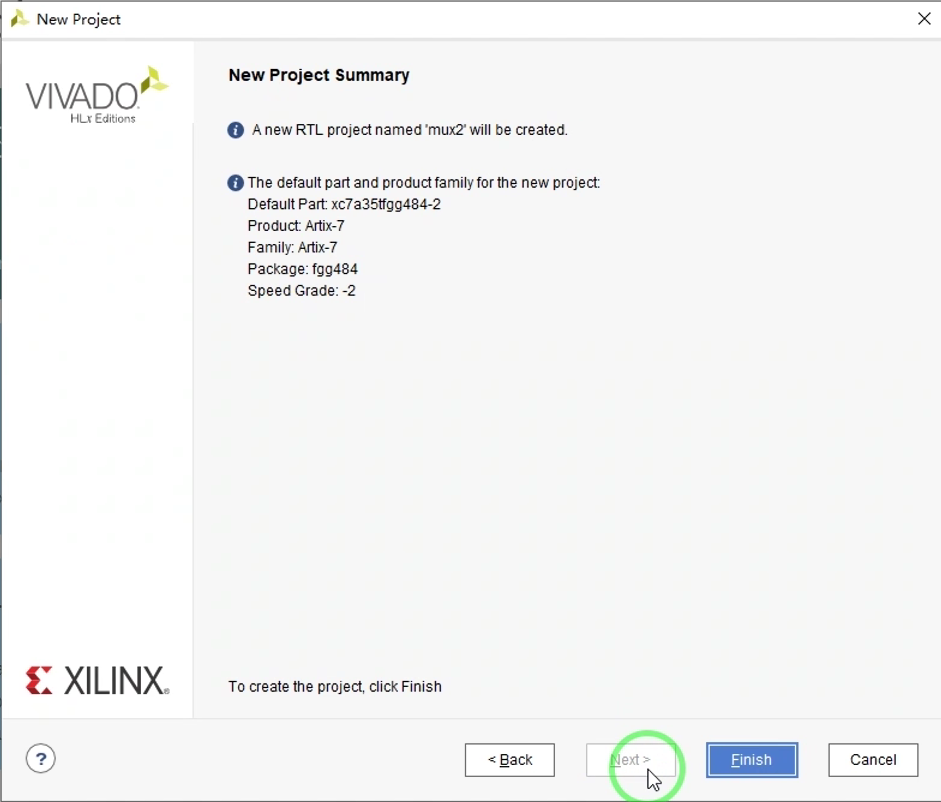

下一页是汇总页面,展示了前面的页面中选择和设置的内容,核对无误后点击Finish即可完成创建

接下来需要根据任务需求进行设计输入,设计输入包括很多方式,比如:硬件描述语言(HDL)、原理图、IP等,这里最适合的设计输入方式是HDL。

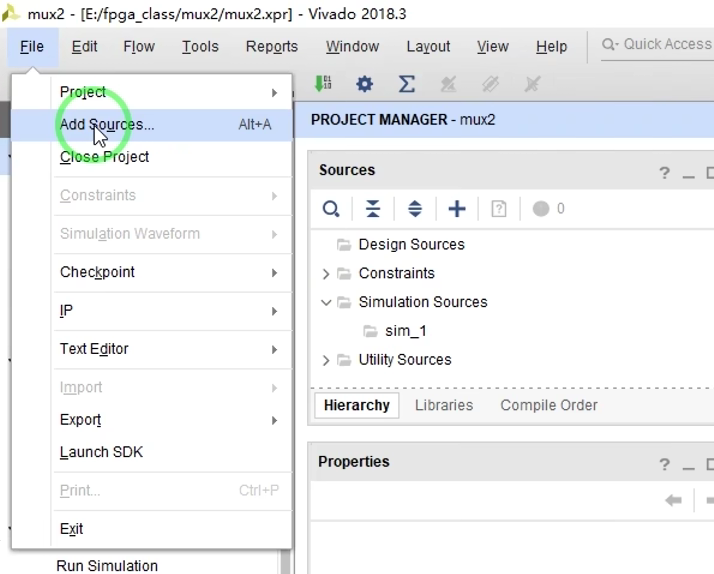

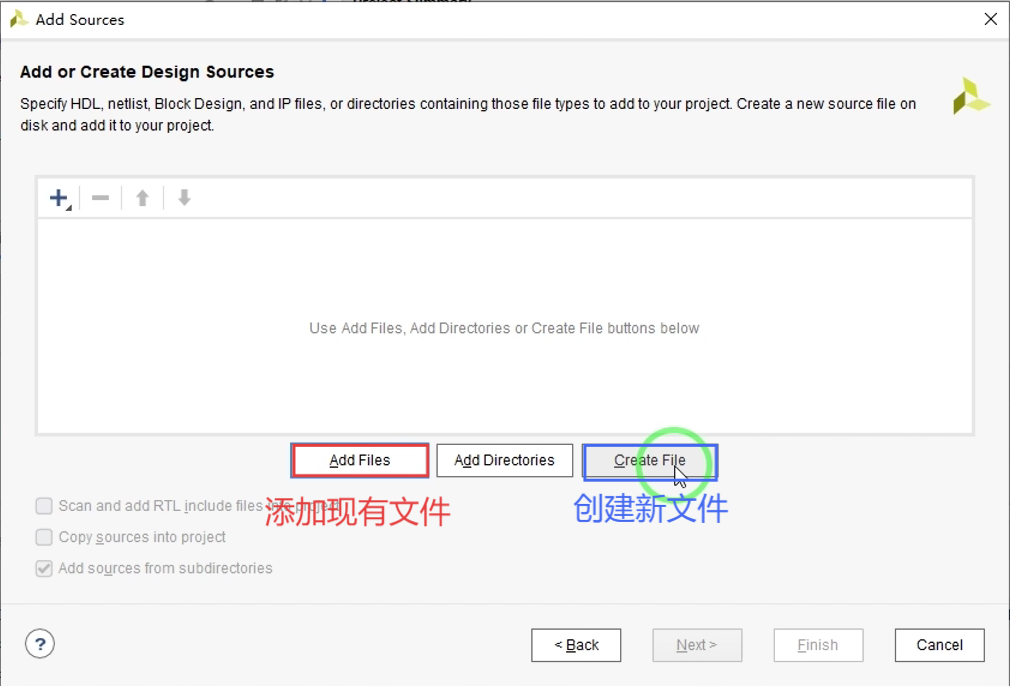

点击File→Add Sources或者直接在主界面使用 Alt+A 的快捷键即可调出创建设计源文件的选项卡。

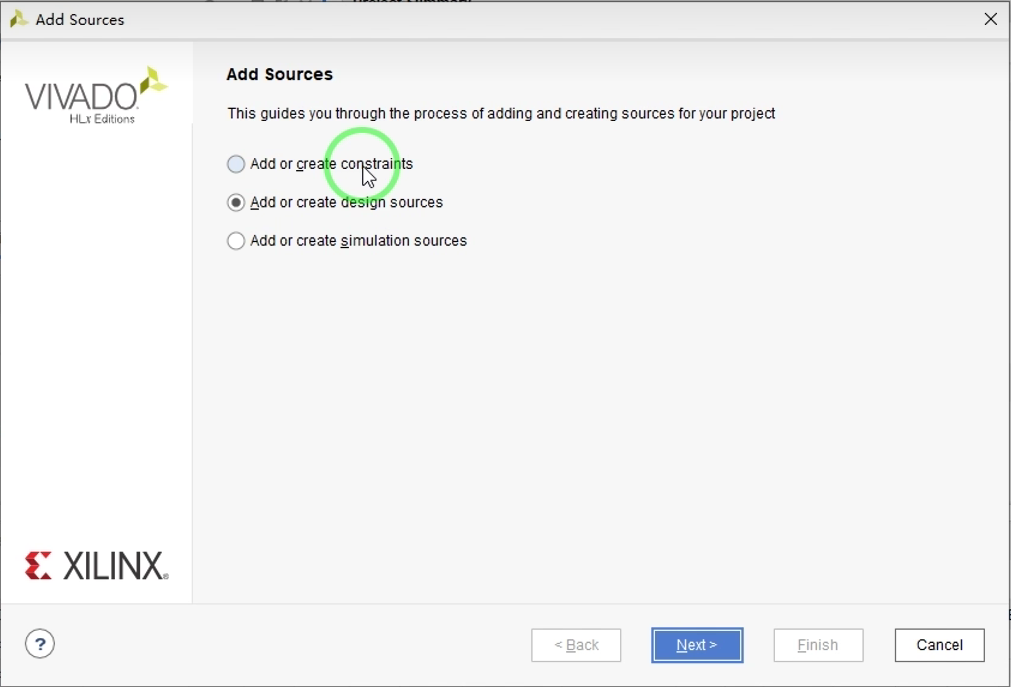

第一个选项是添加一个约束(物理相关的信息),第二个是创建或添加一个设计源文件,第三个是创建一个用于仿真的源文件。这里选择第二个选项即可。

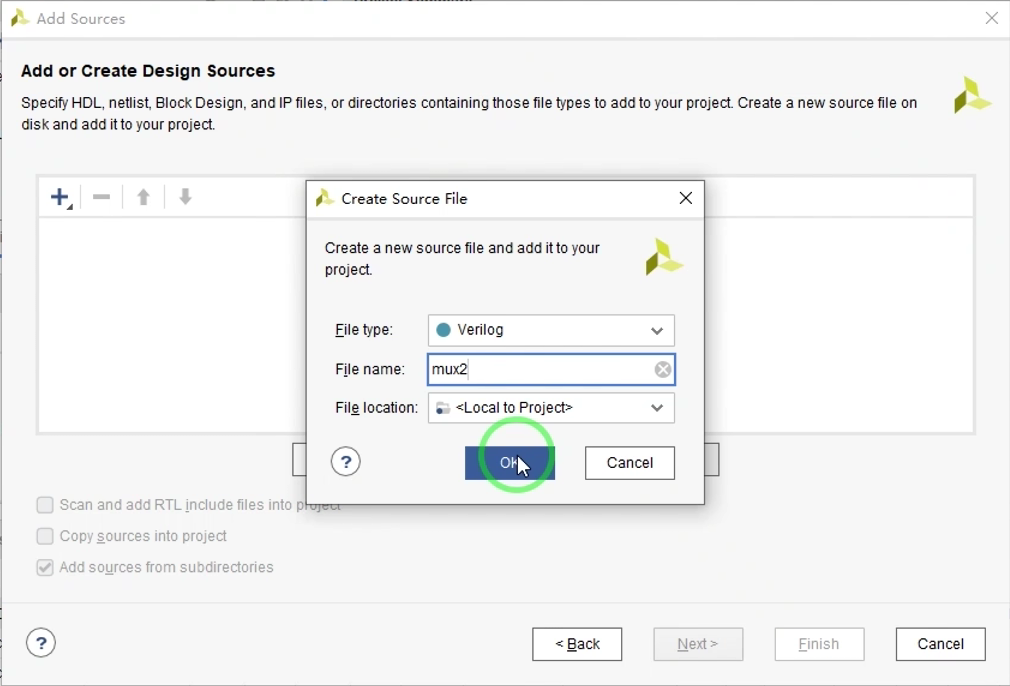

命名是最好与所创建的工程名称保持一致,点击OK→Finish会弹出下一个选项卡。

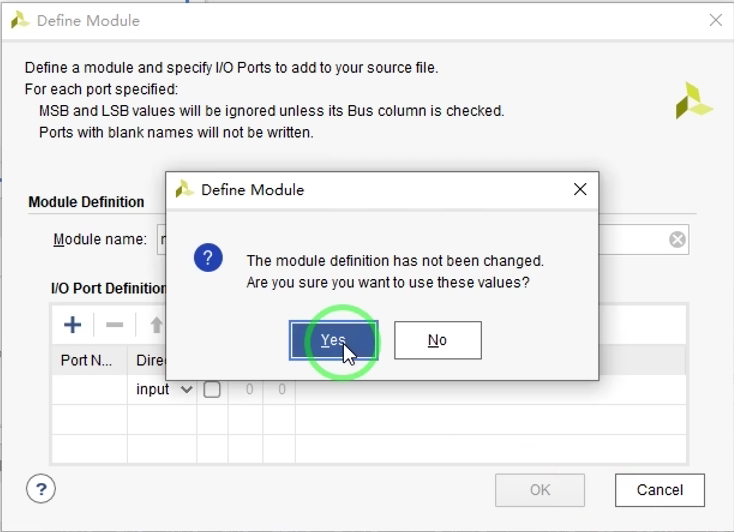

这里需要输入设计的端口信息,但是不常用,直接点击OK→Yes即可。

至此已完成文件的创建。

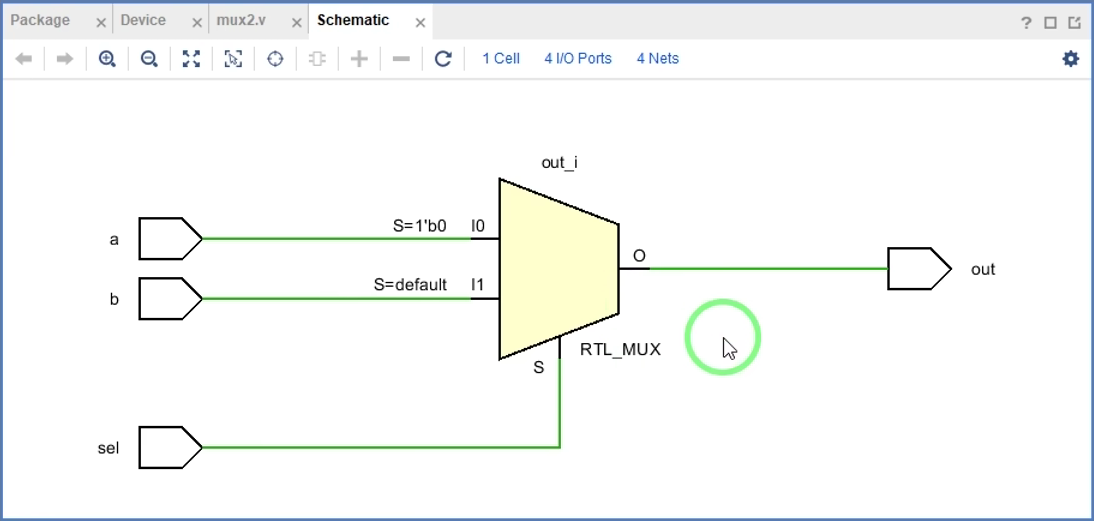

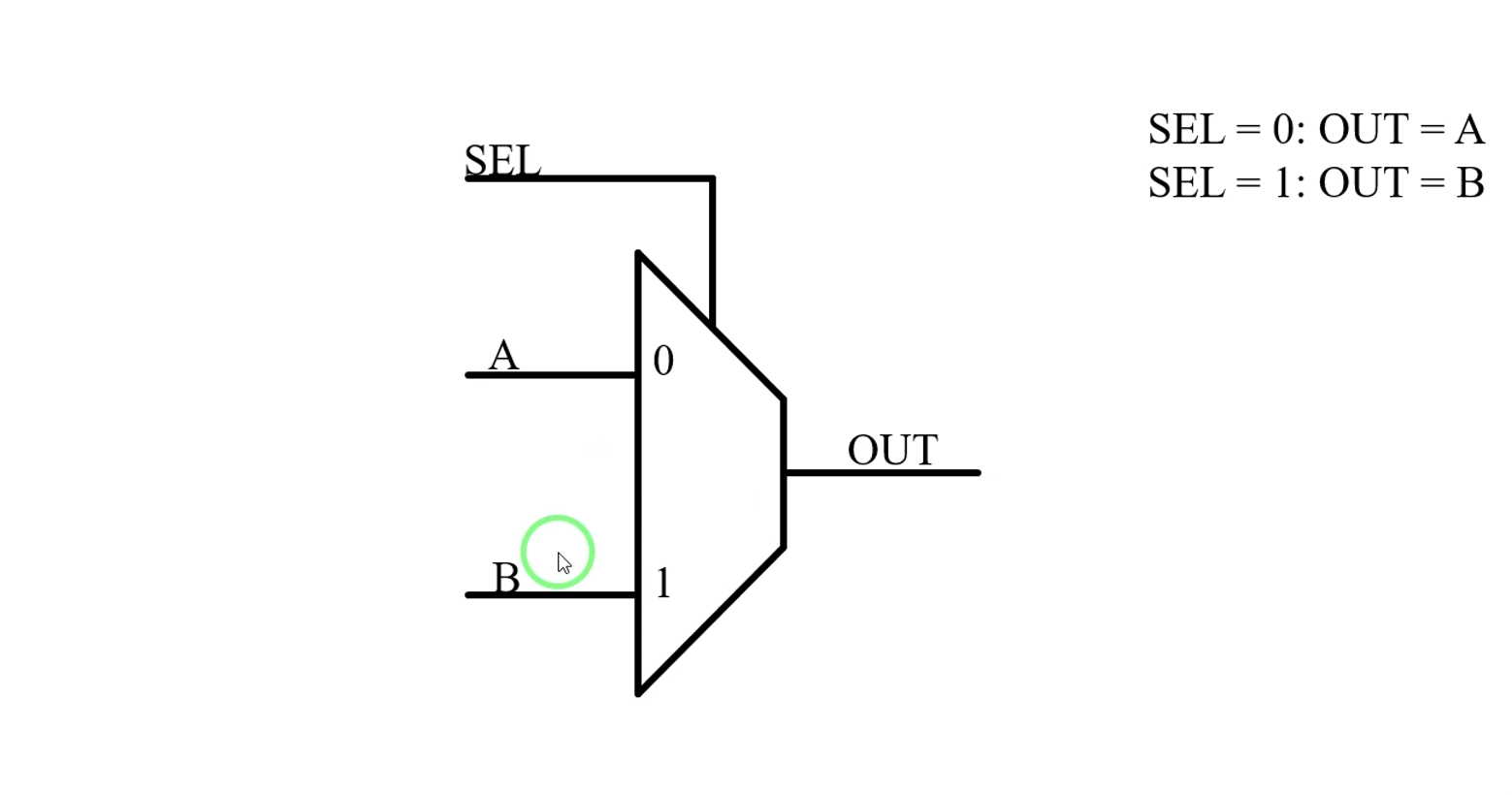

二、二选一多路器

结构如下图,两个输入一个输出和一个选择端口。

功能是当SEL=0时:OUT=A;当SEL=1时:OUT=B

三、 程序编写

1.准备工作

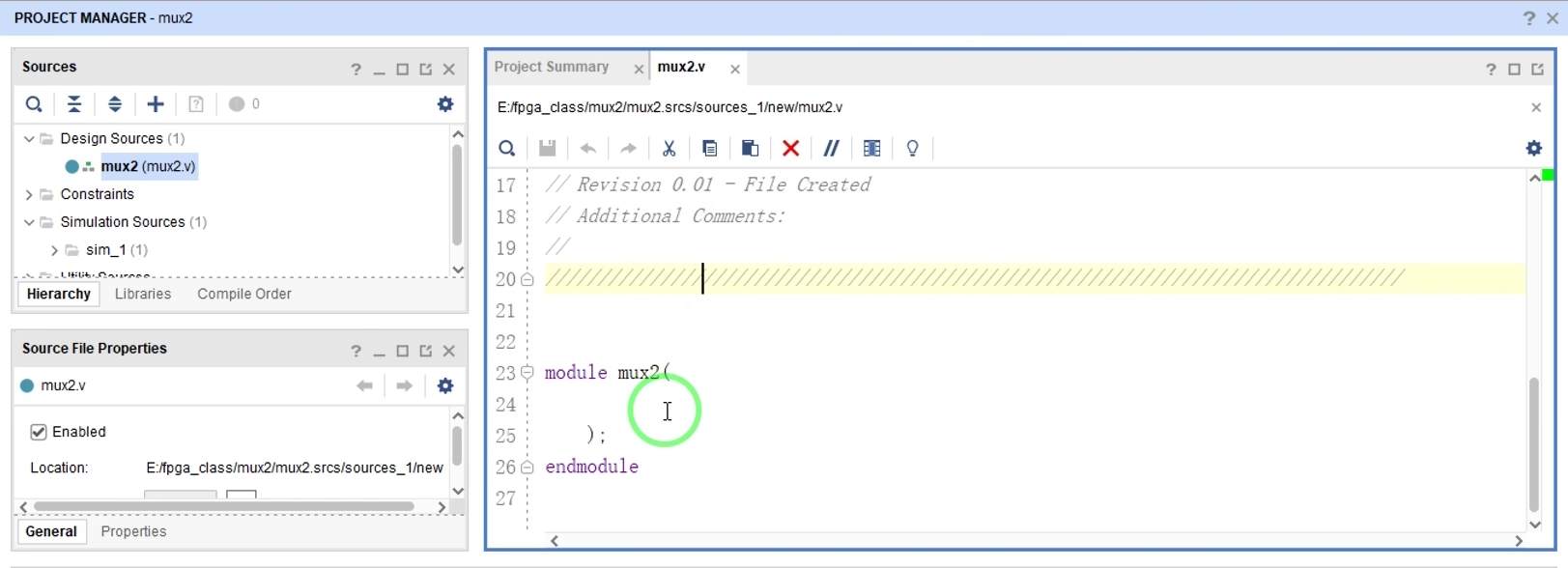

双击文件名打开代码编写的窗口,先将软件自动生成的程序全部删除

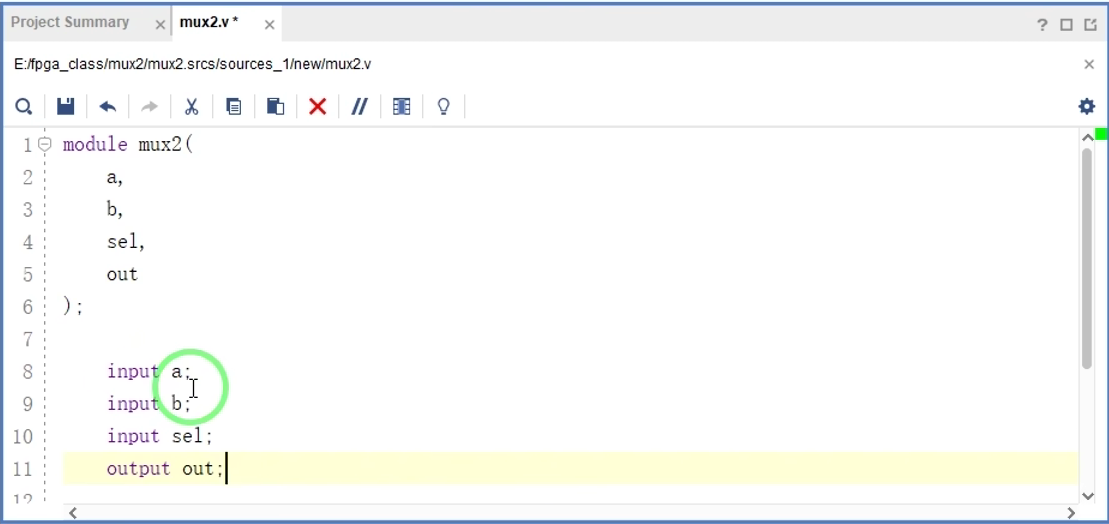

2.创建模块

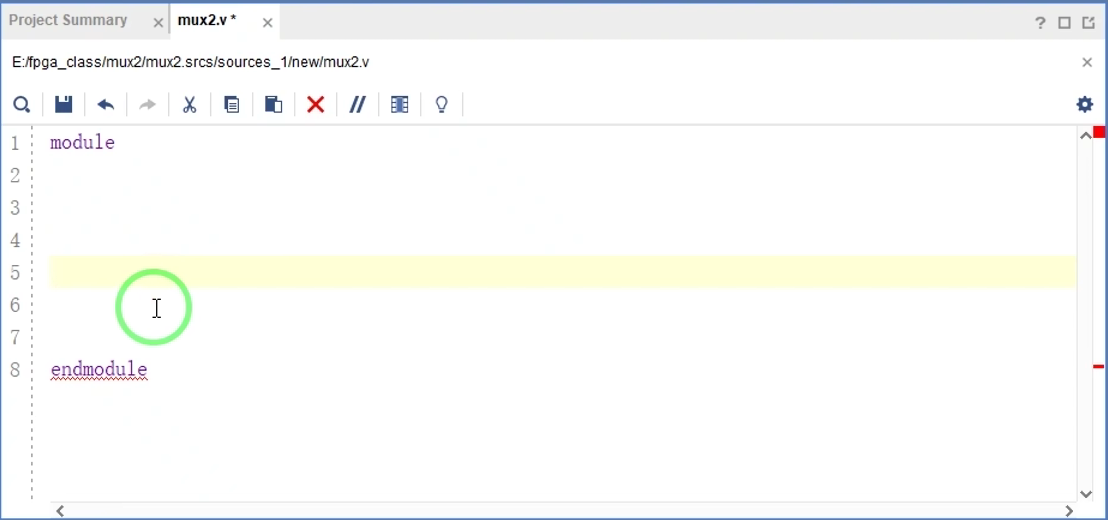

任意一个模块都是由module表示模块开始,endmodule表示模块结束。

3.模块声明

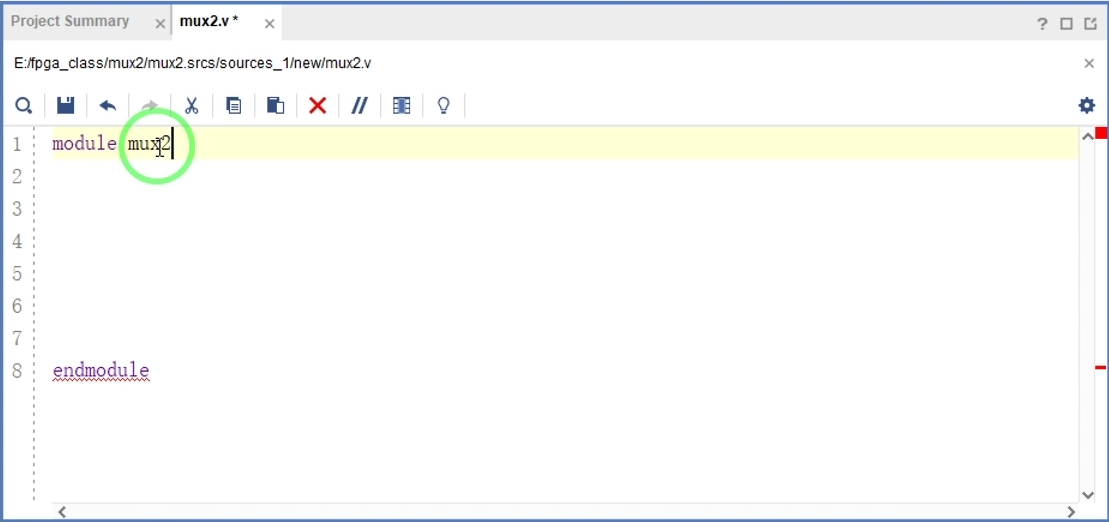

将模块的名称直接写入代码中,进行模块声明

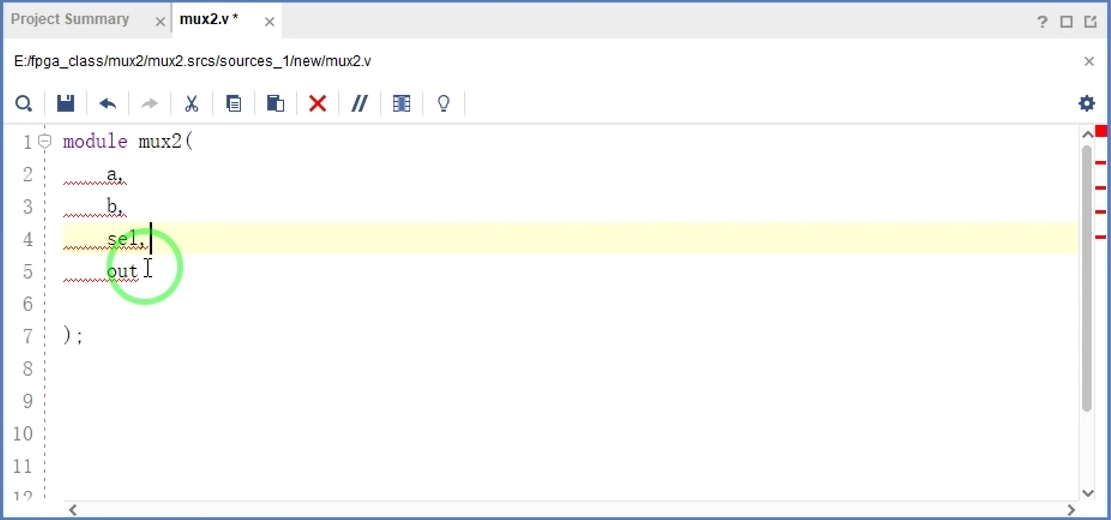

4.端口声明

在模块声明之后进行端口说明,用括号()括起来,里面写端口列表,每个端口写完之后使用一个英文的逗号分开,括号外面加分号;代表端口列表结束。

注意:verilog代码中所有的字母区分大小写,且所有字符均需使用英文字符

5.端口定义

端口列表写完后,需要对端口的类型进行说明,每个端口定义完用分号;结束

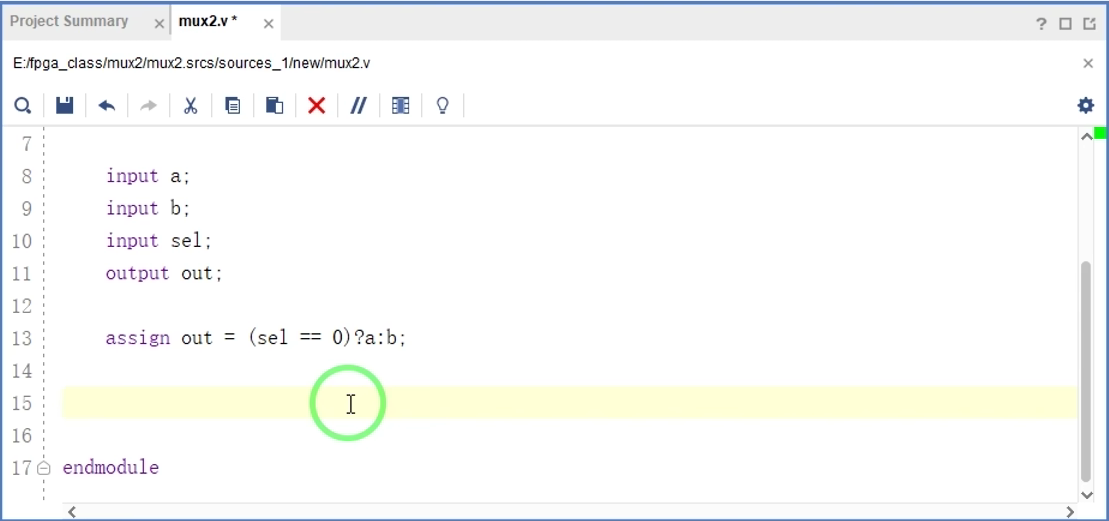

6.描述功能

描述输出端口和输入端口的逻辑关系

assign是连续赋值语句,等号右边的内容对等号左边的内容进行赋值

判断sel是否为0,为0则out=a,不为0则out=b,相当于C语言中的三目运算符

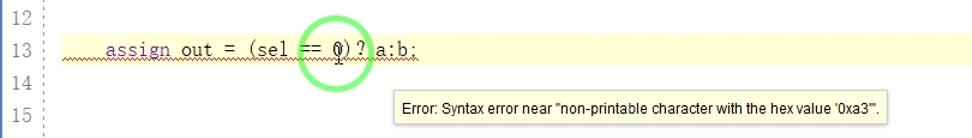

提示:Vivado团建的代码编译器本身的自带有语法检测功能,会用红色波浪线标注出有语法错误的代码,一般出现无法打印的字符就说明代码中含有中文字符

四、代码分析

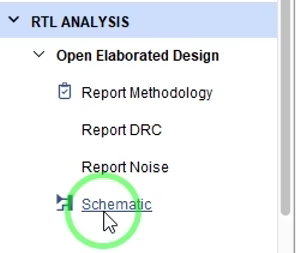

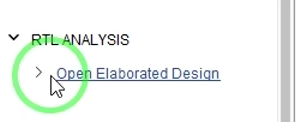

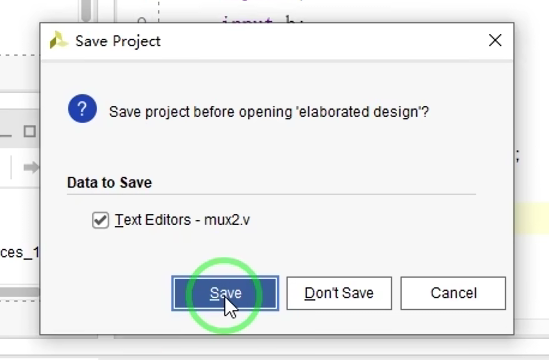

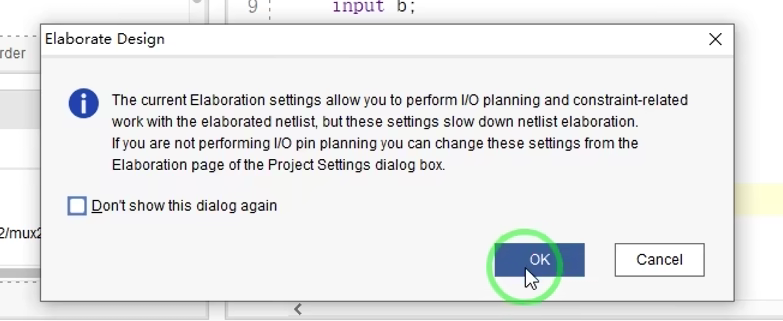

点击RTL中的Open Elaborated Design,保存所写的代码

点击OK进行代码分析

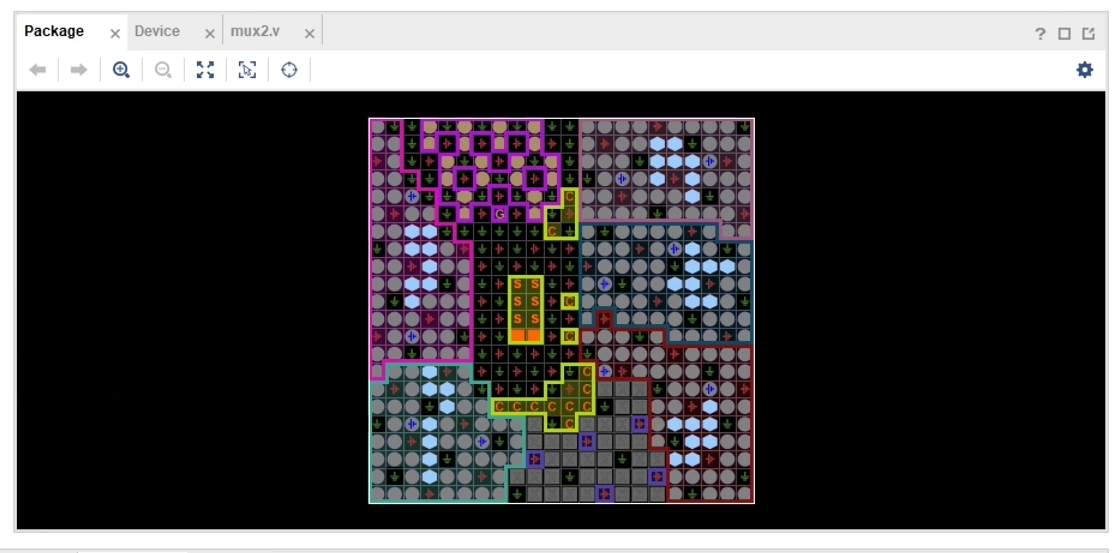

此时显示的是芯片的封装

点击Schematic即可出现符号图