前文回顾:

二选一多路器和三八译码器都是组合逻辑电路

输出只与输入有关,与时间无关

只要输入发生变化,输出就会立即发生变化

时序逻辑电路不仅与输入的信号状态有关,还与时钟信号有关

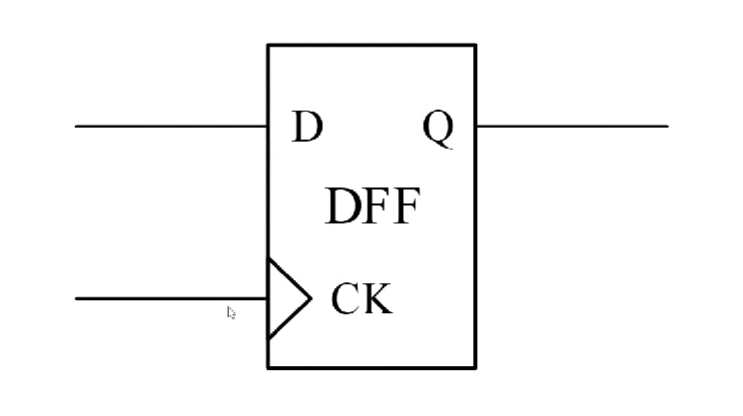

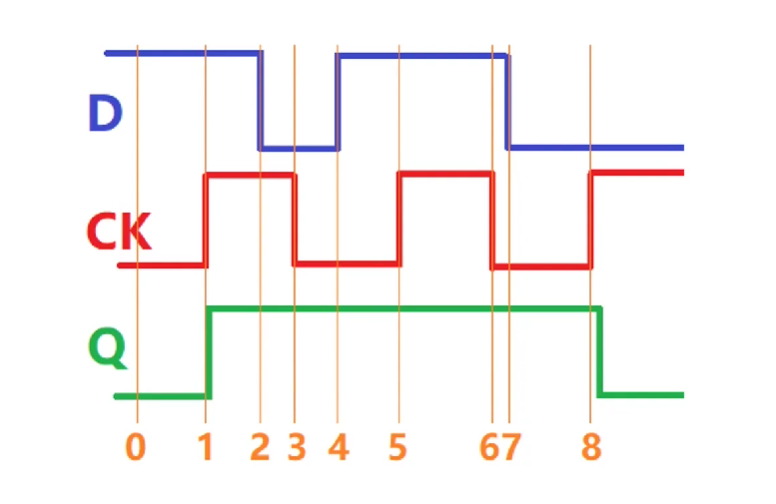

1.D触发器

在数字电路的时序逻辑电路中,最为核心的部件是D触发器 ,也称寄存器

D触发器的典型特征是具有存储能力

即在某时刻D端口的值会被存入D触发器并呈现在Q端口上,过了该时刻,即使D端口上的值发生变化,新的值也不会再被存入D触发器,Q端口会一直保持那个时刻获取到的值不变,直到那个时刻再次出现。这里说的时刻是CK端口的信号从0变为1的情况,或连接在CK端口的信号出现上升沿的时刻。

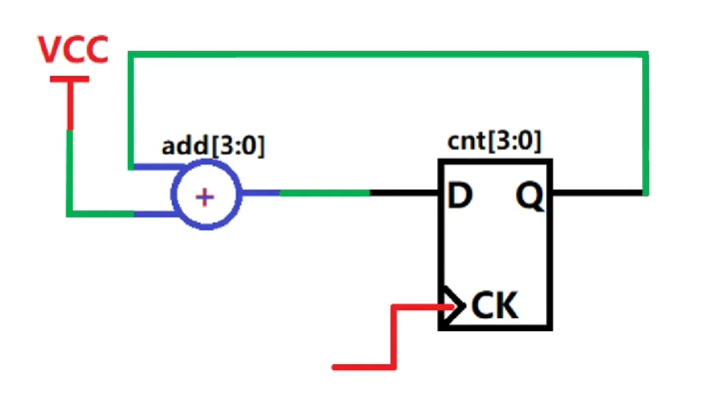

2.计数器