目录

[2.Reg2Reg路径建立时间裕量(Setup Slack)公式](#2.Reg2Reg路径建立时间裕量(Setup Slack)公式)

[建立时间裕量(Setup Slack)公式:](#建立时间裕量(Setup Slack)公式:)

[3.Reg2Reg路径保持时间裕量(Hold Slack)公式](#3.Reg2Reg路径保持时间裕量(Hold Slack)公式)

[保持时间裕量(Hold Slack)公式:](#保持时间裕量(Hold Slack)公式:)

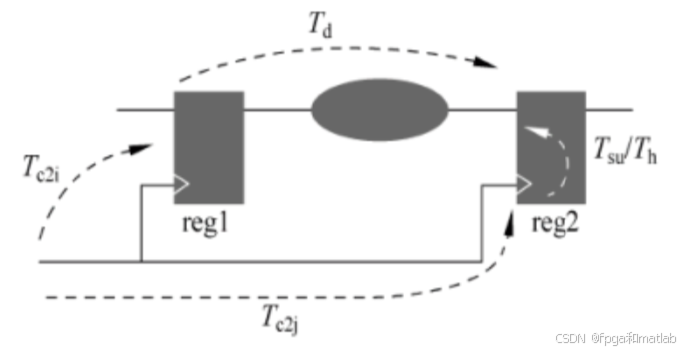

1.Reg2Reg路径时序模型

在数字集成电路设计中,寄存器到寄存器(Reg2Reg)路径是最基础且最重要的时序路径之一,指的是数据从一个寄存器的输出端传输到另一个寄存器的输入端所经过的路径。时序分析的核心目标是确保数据能够在时钟约束下正确传输,避免建立时间(Setup Time)和保持时间(Hold Time)违例。其Reg2Reg路径时序模型如下图所示:

Reg2Reg路径的基本模型包含以下关键组件和时序参数:

1.源寄存器 (Launch Register):数据的发送端寄存器,在时钟边沿触发数据输出。

2.目的寄存器 (Capture Register):数据的接收端寄存器,在时钟边沿锁存输入数据。

3.组合逻辑 (Combinational Logic):源寄存器输出到目的寄存器输入之间的逻辑电路(如逻辑门、多路选择器等),数据在其中传输会产生延迟。

4.时钟信号:驱动源寄存器和目的寄存器的时钟(可能存在时钟偏移,即skew)。

2.Reg2Reg路径建立时间裕量(Setup Slack)公式

建立时间裕量用于衡量数据是否能在目的寄存器时钟边沿到来前稳定,确保正确锁存。其核心约束是:数据到达目的寄存器输入端的时间必须早于目的寄存器时钟边沿减去建立时间。

建立时间约束公式:

数据到达目的寄存器输入端的总时间(源寄存器输出到目的寄存器输入的延迟)必须满足:

T_co + T_logic + T_skew ≤ T_clk_period - T_setup

其中:

左侧:数据到达目的寄存器输入端的总延迟(

T_co为源寄存器输出延迟,T_logic为组合逻辑延迟,T_skew为时钟偏移带来的额外时间)。右侧:目的寄存器允许的数据最晚到达时间(时钟周期减去建立时间)。

建立时间裕量(Setup Slack)公式:

裕量为 "允许的最晚到达时间" 与 "实际到达时间" 的差值:

Setup Slack = (T_clk_period - T_setup) - (T_co + T_logic + T_skew)

若

Setup Slack≥0:满足建立时间约束,数据能正确锁存。若

Setup Slack<0:存在建立时间违例,可能导致数据锁存错误。

3.Reg2Reg路径保持时间裕量(Hold Slack)公式

保持时间裕量用于衡量数据在目的寄存器时钟边沿到来后是否能保持稳定,确保锁存的是正确数据。核心约束是数据到达目的寄存器输入端的时间必须晚于目的寄存器时钟边沿加上保持时间。

保持时间约束公式:

数据到达目的寄存器输入端的总时间必须满足:

T_co + T_logic + T_skew ≥ T_hold

其中:

左侧:数据到达目的寄存器输入端的总延迟(同建立时间分析)。

右侧:目的寄存器要求的数据最早到达时间(时钟边沿加上保持时间)。

保持时间裕量(Hold Slack)公式:

裕量为 "实际到达时间" 与 "要求的最早到达时间" 的差值:

Hold Slack = (T_co + T_logic + T_skew) - T_hold

若

Hold Slack ≥ 0:满足保持时间约束,数据能稳定保持。若

Hold Slack < 0:存在保持时间违例,可能导致锁存错误数据。

在实际设计中,时钟偏移(T_skew)、组合逻辑延迟(T_logic)和寄存器固有延迟(T_co、T_setup、T_hold)都会影响裕量,需通过时序优化(如调整逻辑结构、插入缓冲器、优化时钟树等)确保裕量非负。