ARM 总线系列文章:

ARM 总线技术 ------ AMBA 入门

ARM 总线技术 ------ AHB

本文的参考资料为官方文档 AMBA™3 APB Protocol specification

1、APB

APB 总线特点:

- 低速总线、低功耗,时钟频率通常不会超过 100MHz

- 接口简单、适应性更强

- 单主-多从设备,其主设备就是 APB 桥,不具有仲裁机制

APB 一般可以分为 2 个组成部分:

- AHB2APB Bridge

- 可以锁存所有的地址、数据和控制信号

- 进行二级译码来产生APB从设备选择信号

- APB 总线上的所有其他模块都是 APB 从设备,APB 总线上没有主设备!

本质上来说,不存在只有 APB 的 SOC,AHB 是基础,APB 是 AHB 的延申

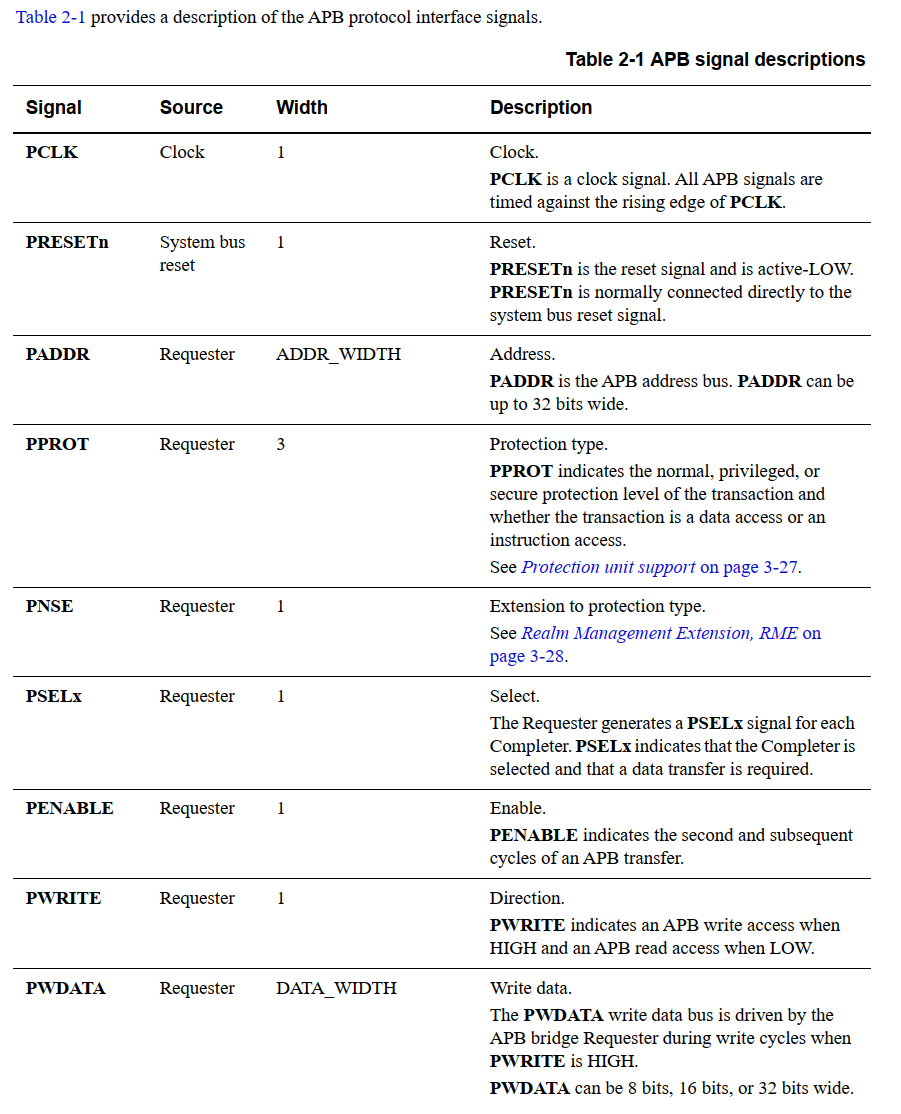

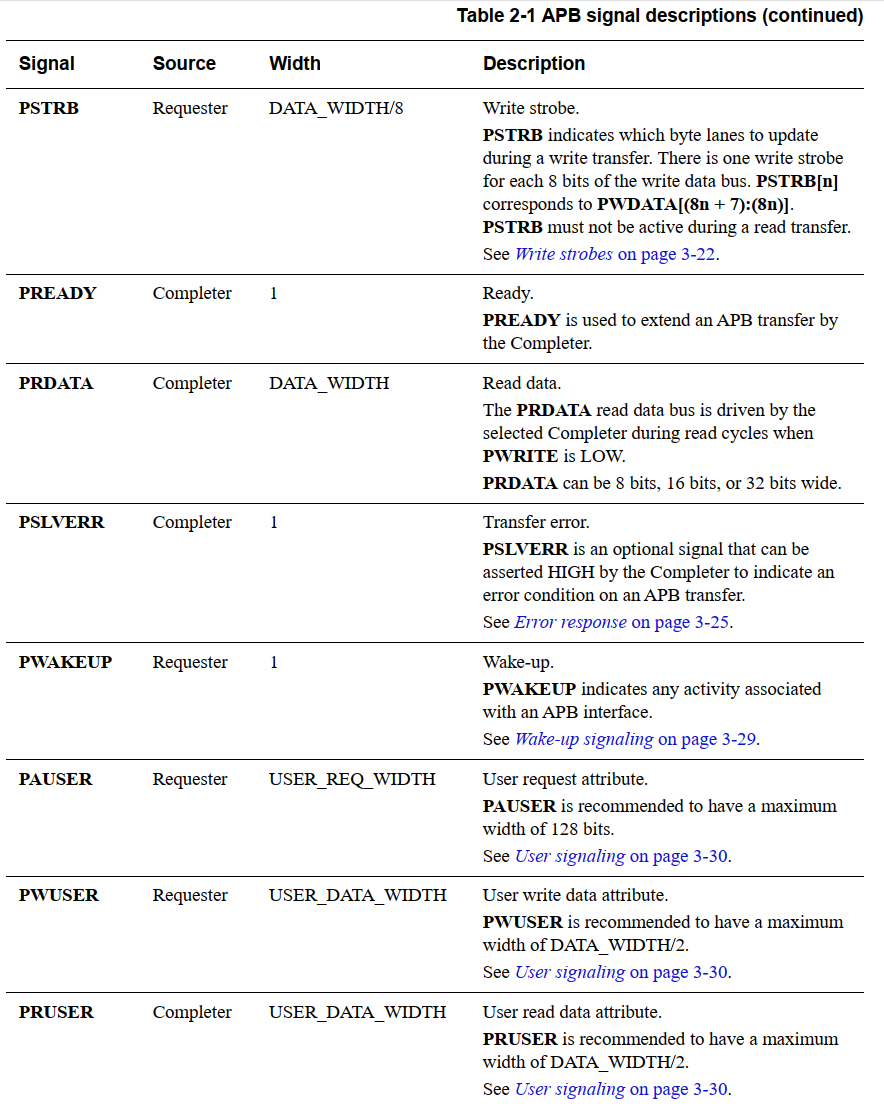

2、APB 常见的信号

- PCLK:时钟信号(上升沿有效)

- PRESETn:复位信号(低电平有效)

- PADDR:地址信号(位宽最高可达 32 位)

- PPROT:保护类型选择信号(APB4 中新加入的信号)

- 该信号主要用作安全事务标识,即 ARM 架构的 secure 和 non-secure 访问

- PSELx:从机选择信号(每个从机单独拥有)

- PENABLE:使能信号,在 PSELx 拉高一个周期后拉高

- PWRITE:读写类型信号(高电平:写,低电平:读)

- PWDATA:写数据信号(PWRITE 为高时驱动,位宽最高可达 32 位)

- PSTRB:写选通信号(APB4 中新加入的信号,告知写传输时哪个字节的信号有效)

- PREADY:准备完成信号

- PRDATA:读数据信号(PWRITE 为低时驱动,位宽最高可达 32 位)

- PSLVERR:传输失败信号(外设可在不支持此信号时置低)

3、传输(Transfers)

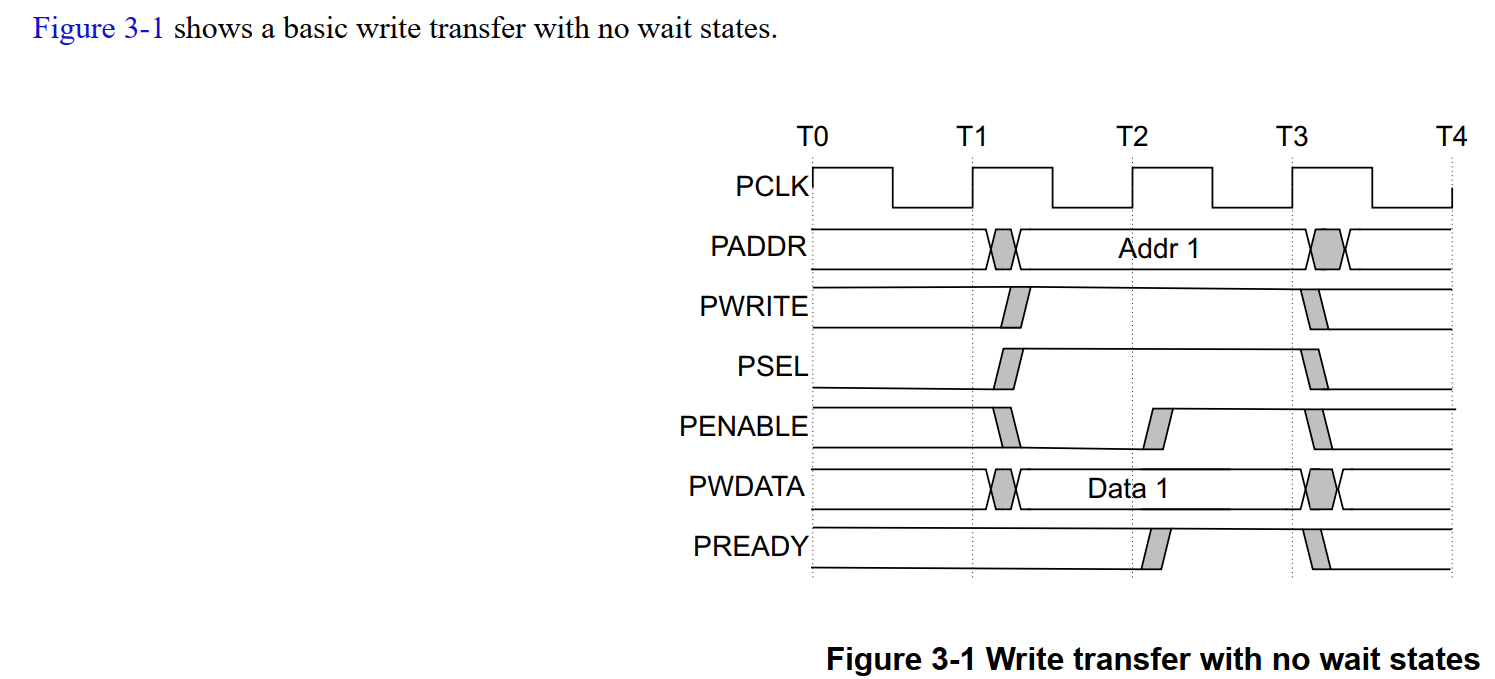

3.1 无等待的写传输

APB 和 AHB 最大的不同就是 APB 不采用 pipeline 形式的写读方式,因此对于 APB 协议来说,最快的写入或者读出一个数据的周期是两周期。先给地址,再写数据;或者先给地址,再读数据。

APB 协议文档中,将上述这种传输方式分为两个阶段(phase),给地址的阶段称为 Set up phase;紧接着下一周期PENABLE 信号拉高,标志着进入写/读数据的阶段,该阶段称为 Access phase。

- T1 时刻(写传输的建立阶段),首先变化的是 PADDR(告知写的地址)、PWDATA(所需写的数据)、PWRITE(置高,代表为写传输模式)、PSEL(等待写入的设备被选中)

- T2 时刻,PENABLE(置高,代表写操作的访问阶段),PREADY(置高,代表从机可以在下一个上升沿完成输出传输,如果为低则说明数据没有准备好)

- T3 时刻,数据完成传输之前 PADDR 和 PWDATA 都需保持有效状态,在传输结束之后 PENABLE 和 PSEL(除非该设备立即有传输请求,则无需恢复)恢复低电平

和 AHB 一样,采样的时机,都是在每个时钟周期的上升沿

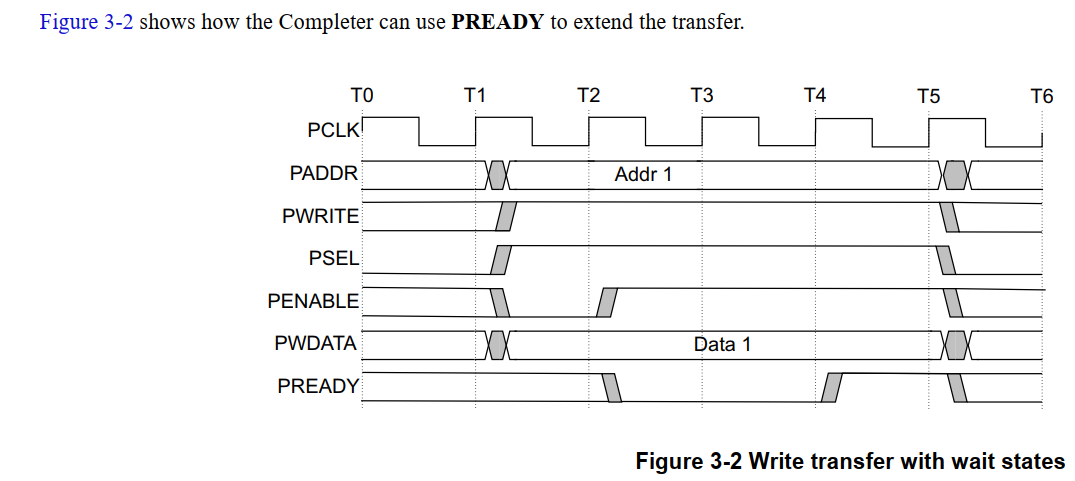

3.2 有等待的写传输

- 当 PENABLE 置为高要完成写传输时,通过将 PREADY 置为低,其他信号(PADDR、PWRITE、PSEL、PENABLE、PWDATA、PSTRB和PPROT)保持不变实现等待。当 PENABLE 和 PREADY 均为高时,在下一个上升沿即完成写数据操作

- 保持地址和写信号不变的目的是降低功耗

3.3 读传输

和写传输类似,读传输这里不再详细讲解。