I2C通信

I2C基本电路结构

串口的缺点

串口通信(UART/USART 为代表)虽因简单、低成本、硬件要求低 成为嵌入式开发的 "标配",但受限于物理层设计和通信协议,存在不少固有缺点 ------ 尤其在高速、大容量、高可靠性场景下。下面指出串口通信的一些缺点:

- 核心缺点:速率低,传输效率有限

- 抗干扰能力弱,可靠性依赖布线

- 无硬件流控时,易出现数据溢出(ORE 错误)

- 点对点通信,扩展能力差

串口的缺点本质是 "为简单和低成本牺牲了速率、抗干扰、扩展性",因此它的核心适用场景是:

- 短距离、低速率、低干扰

- 数据量小(如指令、状态上报)

- 点对点通信(如开发板调试、STM32 与蓝牙模块通信

I2C简介

I2C(Inter-Integrated Circuit,集成电路间总线)是由 Philips(现 NXP)开发的 短距离、同步串行通信总线,核心特点是 仅需 2 根线(SDA 数据线 + SCL 时钟线) 即可实现多设备间通信,广泛应用于嵌入式系统(如 STM32 与传感器、EEPROM、LCD 模块的连接

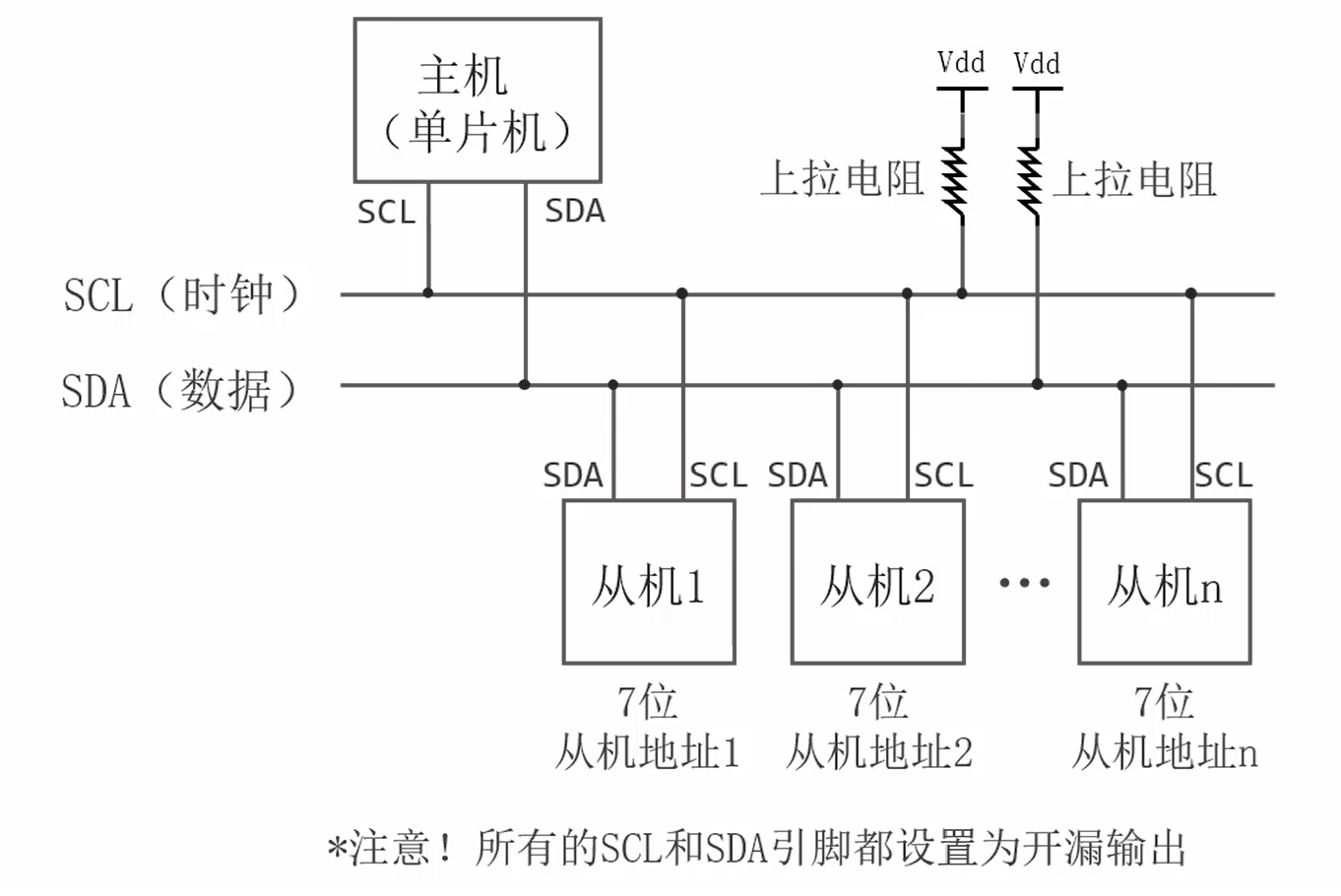

I2C总线的电路结构

时钟线与数据线

I2C 通信的核心是 "时钟同步",而 SCL(Serial Clock,串行时钟线)就是实现同步的关键 ------ 它由主机(如 STM32)完全控制,从机(如传感器、EEPROM)必须严格跟随 SCL 的时钟节拍收发数据,因此 SCL 也被称为 I2C 总线的 "节拍器"

SCL 线的唯一作用是提供同步时钟信号,所有数据传输都必须在时钟的 "指挥" 下进行,具体职责:

- 同步数据传输:主机通过 SCL 产生固定频率的时钟脉冲,从机根据时钟的高低电平变化,同步采样 / 发送 SDA 线上的数据(避免数据传输错位)

- 划分数据位:每一个时钟脉冲对应 SDA 线上的 1 位数据(0 或 1),8 个时钟脉冲完成 1 字节数据传输

- 控制通信节奏:主机可通过拉伸 SCL(拉低并保持)暂停通信(如主机处理数据时),从机完成准备后释放 SCL,通信继续

- 区分总线状态:SCL 的电平变化配合 SDA,定义 I2C 的关键状态(启动、停止、数据有效)

简单说:SCL 决定了 I2C 通信的 "速度" 和 "节拍",没有 SCL 的同步,SDA 线上的数据流就是 "无意义的电平跳变",从机无法识别

I2C 总线的 SCL 和 SDA 线电气特性完全一致,核心是 "开漏输出(OD)+ 上拉电阻",这是 SCL 稳定工作的基础:

开漏输出(OD)

- 所有设备(主机 + 从机)的 SCL 引脚都配置为开漏输出:

- 设备要输出 "低电平" 时:主动拉低 SCL 线(接地)

- 设备要输出 "高电平" 时:不驱动总线(释放 SCL 线),由上拉电阻将总线拉为高电平

- 优势:避免总线冲突 ------ 多个设备同时驱动 SCL 时,最多只有一个设备拉低(低电平主导),释放后总线自动恢复高电平,不会出现 "高电平 vs 低电平" 的短路冲突

上拉电阻的作用

SCL 线必须在总线两端(靠近主机和最远从机)接 4.7KΩ~10KΩ 的上拉电阻(电源匹配设备电平,如 3.3V/5V),核心作用:

- 提供高电平:开漏输出无法主动输出高电平,上拉电阻将总线默认拉为高电平;

- 限制电流:避免设备拉低总线时电流过大(保护芯片引脚);

- 稳定信号:抑制 SCL 线的电平抖动,提升抗干扰能力

SDA(Serial Data,串行数据线)是 I2C 总线中 唯一传输实际数据的通道 ,与 SCL(时钟线)配合实现 "同步数据收发"------SCL 提供 "节拍",SDA 承载 "信息",两者缺一不可。SDA 的核心特点是 双向传输 + 开漏输出 + 应答机制,这是它能在一根线上实现主机与从机双向通信的关键

SDA 线的唯一职责是 传输二进制数据和应答信号,所有 I2C 通信的核心信息(从机地址、寄存器地址、数据、应答)都通过 SDA 传输,具体包括:

- 地址传输:主机发送从机地址(7 位 / 10 位)+ 读写方向位(第 8 位),从机通过地址匹配判断是否需要响应

- 数据传输:双向传输字节数据(主机→从机的 "写数据"、从机→主机的 "读数据"),每帧数据为 8 位

- 应答传输:每传输 1 字节后,接收方通过 SDA 发送 ACK(应答)或 NACK(非应答),告知发送方 "数据是否接收成功"

- 总线状态标识:配合 SCL 的电平变化,通过 SDA 的跳变定义 I2C 的启动(Start)、停止(Stop)条件

简单说:SDA 是 I2C 总线的 "信息高速公路",所有需要交互的内容都在这根线上传输,而 SCL 是 "交通信号灯",确保数据传输有序不冲突

开漏输出(OD):双向通信的基础

所有设备(主机 + 从机)的 SDA 引脚都必须配置为开漏输出:

- 输出低电平:设备主动拉低 SDA 线(接地),此时总线电平为低

- 输出高电平:设备不驱动总线(释放 SDA),由上拉电阻将总线拉为高电平

- 双向性原理:开漏输出无 "发送 / 接收" 方向限制 ------ 主机可驱动 SDA 发送数据,释放后从机可驱动 SDA 回复数据,实现双向通信

- 总线冲突避免:多个设备同时驱动 SDA 时,低电平主导(只要一个设备拉低,总线就是低),不会出现 "高电平 vs 低电平" 的短路冲突

上拉电阻:SDA 稳定的关键

SDA 线必须与 SCL 线共用或单独接 4.7KΩ~10KΩ 的上拉电阻(电源匹配设备电平,如 3.3V/5V),核心作用:

- 提供默认高电平:开漏输出无法主动输出高电平,上拉电阻确保 "无设备驱动时" SDA 为高电平(I2C 总线的空闲状态)

- 稳定数据信号:抑制 SDA 线的电平抖动(尤其是数据跳变时),提升抗干扰能力

- 限制驱动电流:避免设备拉低 SDA 时电流过大,保护芯片引脚

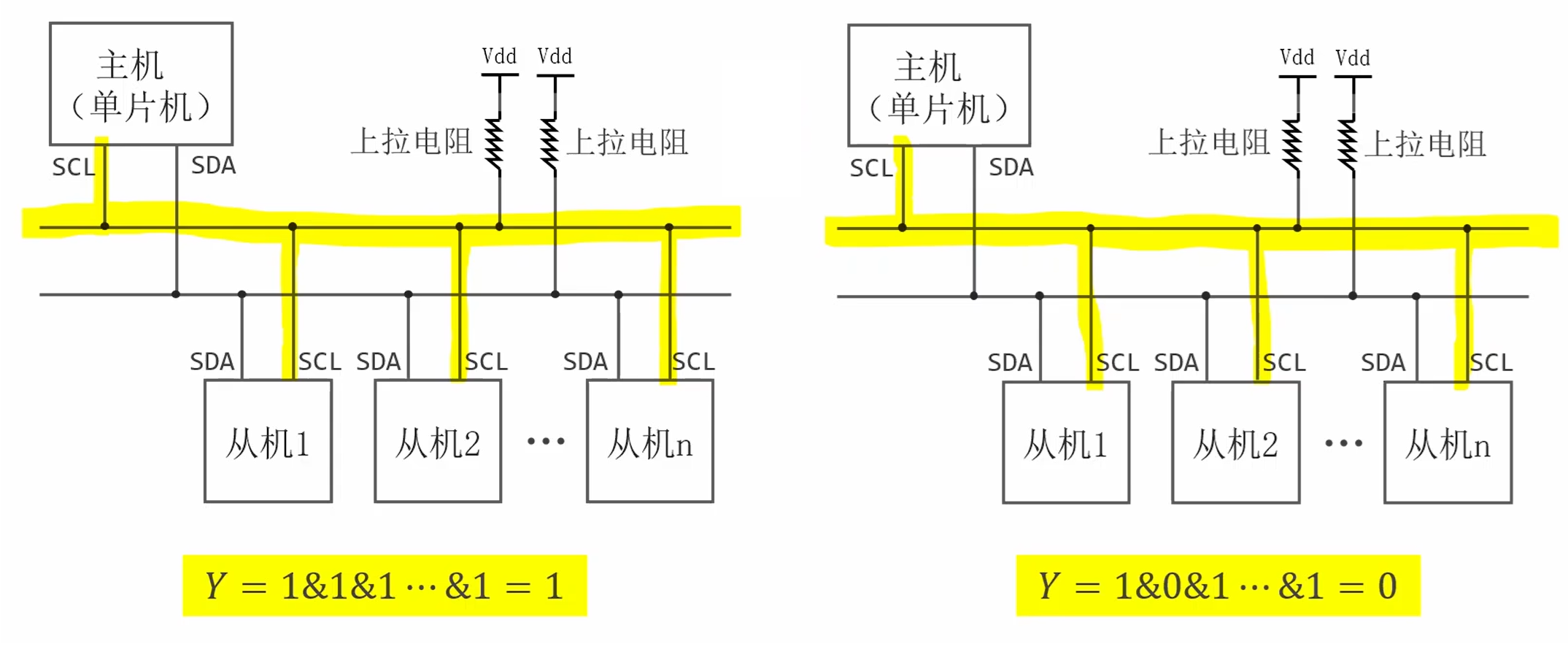

逻辑线与

在 I2C 通信中,"逻辑线与"(Logical AND)是 SDA 和 SCL 总线电气特性的核心底层逻辑------ 正是因为 I2C 总线(SDA/SCL)本质是 "线与" 结构,才实现了 "开漏输出 + 上拉电阻" 的设计,进而支持多设备共享总线、避免冲突、双向通信等核心功能

什么是 "逻辑线与"?

"逻辑线与" 是指 多根信号线通过硬件连接到同一条总线时,总线的最终电平由 "所有设备的输出电平" 通过 "与逻辑" 决定------ 对应数字电路中的 "与门" 逻辑:

- 逻辑与规则:只要有一个设备输出低电平(0),总线最终电平就是低电平(0)

- 只有当 所有设备都不输出低电平(即释放总线,由上拉电阻拉为高电平 1) 时,总线最终电平才是高电平(1)

为什么要采用 "逻辑线与" ?

"逻辑线与" 是 I2C 实现 "极简硬件 + 多设备共享" 的根本,解决了 3 个关键问题:

1.避免总线冲突(多设备驱动同一总线)

UART 是点对点通信,若多设备同时驱动 TX 线,会出现 "高电平 vs 低电平" 的短路冲突(可能烧毁引脚);而 I2C 总线因 "线与" 逻辑:

- 多个设备同时拉低 SDA/SCL:总线仍是低电平,无冲突

- 一个设备拉低、其他释放:总线被拉低,无冲突

- 本质:I2C 设备的开漏输出(只能拉低,不能主动拉高),配合 "线与" 逻辑,从硬件层面杜绝了总线冲突

2. 支持多设备共享总线(一主多从)

所有从机和主机共用 SDA/SCL 两根线,通过 "线与" 逻辑实现 "谁需要谁驱动":

- 主机发起通信时:拉低 SDA 产生启动条件,所有从机检测到总线电平变化,开始接收地址

- 从机地址匹配时:仅该从机拉低 SDA 发送 ACK,其他从机继续释放总线,不干扰

- 通信过程中:只有当前通信的设备(主机 / 从机)驱动总线,其他设备释放,避免干扰

3. 实现双向通信(SDA 线的核心需求)

SDA 线需要在 "主机发送→从机发送" 之间切换,"线与" 逻辑让切换无需额外控制信号:

- 主机发送时:驱动 SDA 拉低 / 释放(对应数据 0/1),从机释放 SDA,总线电平由主机决定

- 从机发送时:主机释放 SDA,从机驱动 SDA 拉低 / 释放(对应数据 0/1),总线电平由从机决定

- 切换时机:SCL 低电平时切换,此时总线电平不影响数据有效性,避免误读

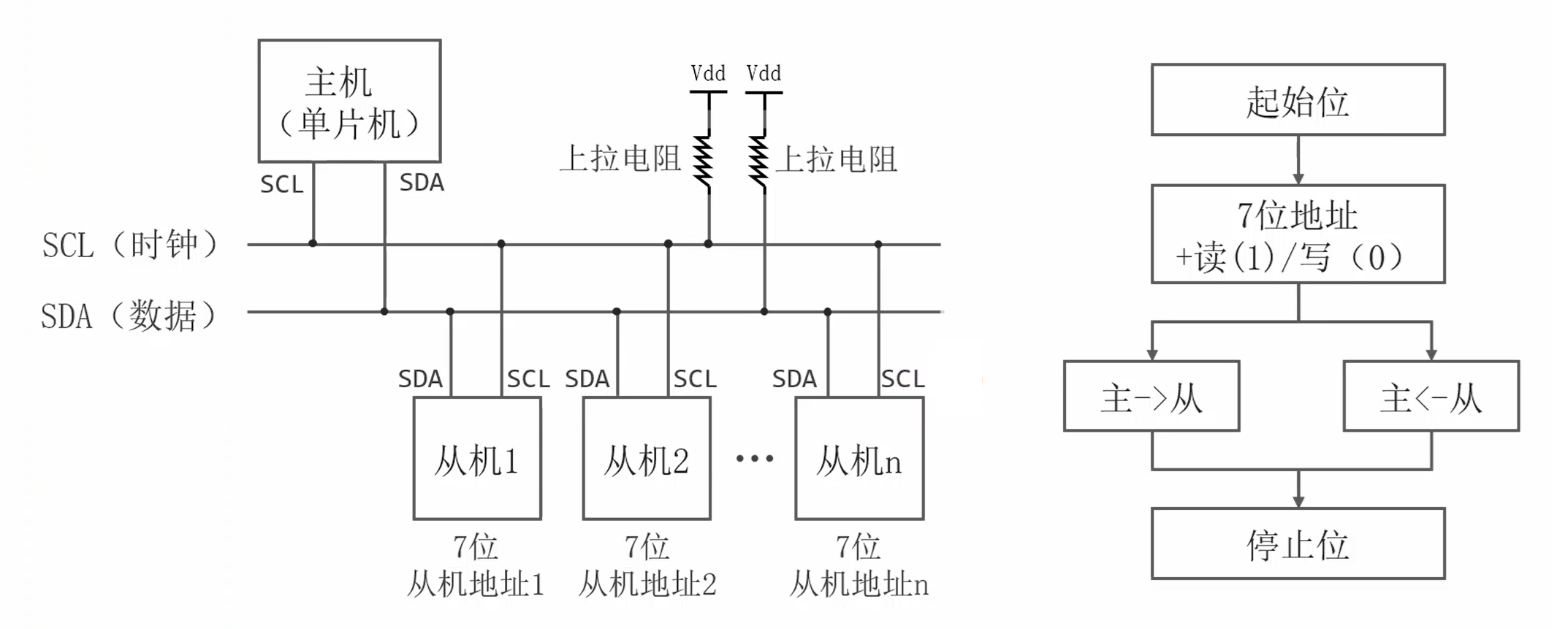

I2C通信协议

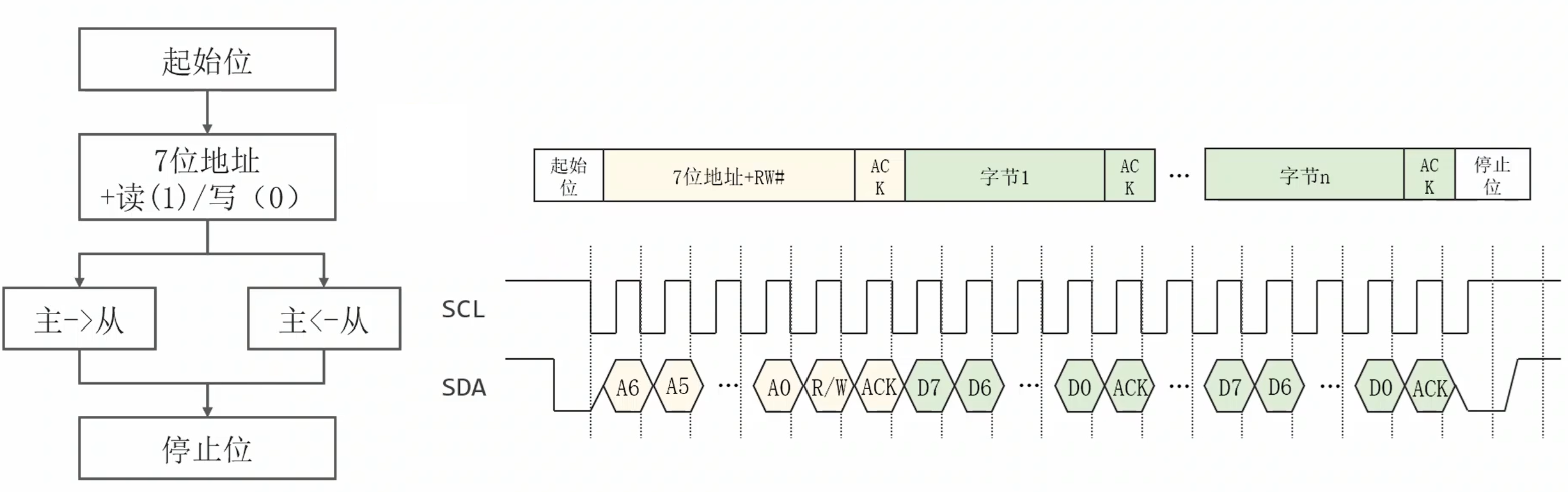

I2C通信的基本流程

- 准备:SDA、SCL 线接好上拉电阻,主机和从机通电就绪,总线空闲时两线均为高电平

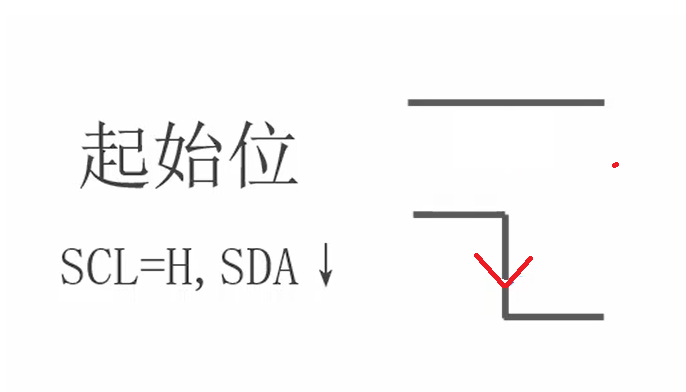

- 启动:主机发起启动条件(SCL 高电平时,SDA 从高变低),告知从机通信开始

- 寻址:主机发送 7 位从机地址 + 1 位读写方向(0 = 写、1 = 读),等待从机应答

- 应答:从机地址匹配则拉低 SDA 发应答(ACK),不匹配则无应答,主机需终止通信

- 传数据:

- 写操作:主机逐字节发数据,每字节后等从机应答

- 读操作:从机逐字节发数据,主机前 N-1 字节发应答(让从机继续发),最后 1 字节发非应答(NACK)

- 先写后读(常用):主机先写指令 / 寄存器地址,再发重复启动(不停止),切换读方向收数据

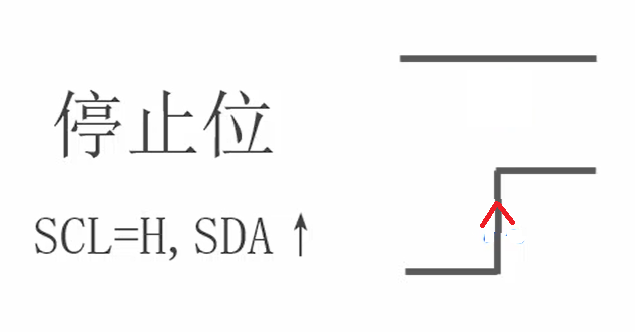

- 停止:主机发起停止条件(SCL 高电平时,SDA 从低变高),通信结束,总线回归空闲

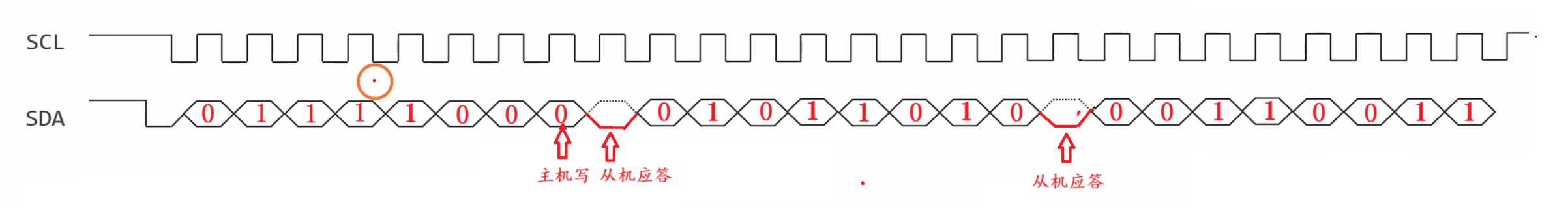

I2C协议的数据格式

- 启动条件:SCL 高电平时,SDA 从高→低(标志数据传输开始)

-

地址帧(8 位,必选)

- 前 7 位:从机地址(I2C 设备的唯一标识)

- 第 8 位:读写方向位(0 = 主机写从机,1 = 主机读从机)

- 作用:主机指定通信对象和数据传输方向

-

数据帧(8 位 / 字节,可多字节)

- 单字节:8 位二进制数据(高位先传)

- 多字节:连续传输多个 8 位字节,每字节独立对应应答位

- 内容:可是寄存器地址、控制指令、实际业务数据(如传感器数值、存储数据)

-

应答位(ACK/NACK,1 位,每帧后必带)

- 应答(ACK):接收方(写操作 = 从机,读操作 = 主机)拉低 SDA 表示 "数据已接收";

- 非应答(NACK):接收方保持 SDA 高电平,表示 "数据接收失败" 或 "无需继续传输"(读操作最后 1 字节必用);

- 时序:紧跟地址帧 / 数据帧后,由主机生成 1 个时钟脉冲采样

-

停止条件:SCL 高电平时,SDA 从低→高(标志数据传输结束)

例子

假设从机地址时0x78,现在使用主机向从机写数据0x5a与0x33,SCL与SDA的时序图如下: