一、什么是Virtual Clock

我们通常说的create_clock和create_generated_clock创建的都是实际时钟(real clock),而虚拟时钟(virtual clock)不连接任何端口或引脚,仅作为虚拟创建的对象存在。

虚拟时钟与实际时钟的关键区别在于时钟源的定义:

-

实际时钟具有明确的时钟源引脚/端口,可以追踪到时钟接收端,并能进行时钟树综合(CTS)

-

虚拟时钟则没有定义时钟源,因此无法完成上述操作定义语法如下:

real clock, with source pin/port

create_clock -name "CLK" -period 10 -waveform [0 5] [get_ports clk]

virtual clock

create_clock -name "CLK_V" -period 10 -waveform [0 5]

二、virtual clock 作用

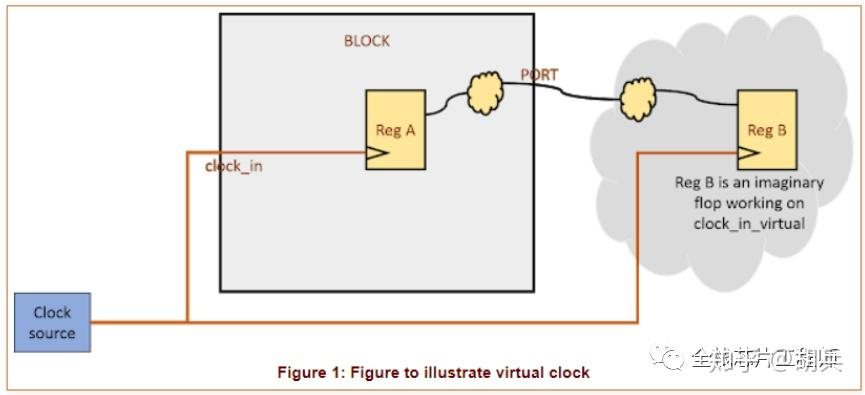

如图所示regA和regB由同一时钟驱动。由于我们只能观察到从regA/Q到Port端口的路径,因此设计中会对port端口设置set_output_delay约束。由此可见时钟路径延迟对时序有着重要影响。

时钟延迟包括时钟源延迟(clock_source_latency)和时钟网络延迟(clock_network_latency)。在CTS时钟树综合完成前,时钟网络延迟被视为理想值(延迟为0)。CTS完成后,时钟树生成,此时clock_network_delay具有实际值。由于regB是假设存在的寄存器,其clock_network_delay仍保持为0,这导致regA/Q到regB/D路径的时序分析对setup要求更为严格。

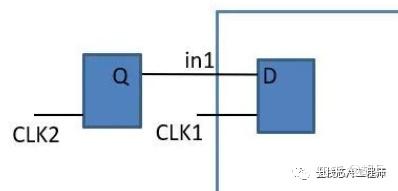

因此,在set_propagated_clock命令后,下图右边寄存器(regB)的CLK1端就不带clock propagation time,而CLK2(与CLK1同频同相)就带insertion delay, 拥有时钟latency,这样输入IO的setup违例就可能发生,hold反而更容易满足。同理,在set_propagated_clock命令后,输入IO的setup违例就可能发生,hold反而更容易满足。

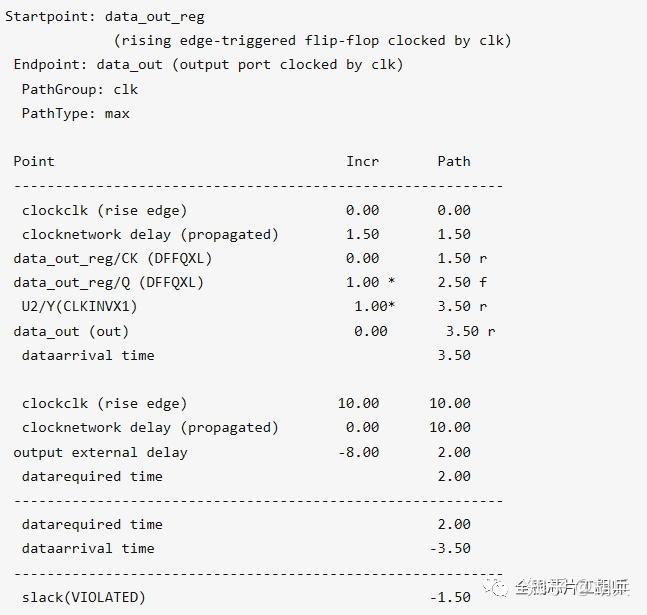

以输出IO的register的setup建立时间为例,launch clock的data path上由于存在1.5ns的propagation time/clock latency,发生了时序违例。这是因为外部假定的register是没有propagation time/clock latency。而保持时间则反而容易满足。

虚拟时钟应运而生,那么创建虚拟时间有什么好处呢?create_clock -name vclk -period 10,不用指定clk pin/port

set_input_delay 8 -clock vclk [get_ports data_in]

set_output_delay 8 -clock vclk [get_ports data_out]

EDA工具会基于虚拟时钟,根据芯片/模块内部时钟的实际insertion delay评估IO外部假定寄存器的propagation time,这样时序分析就可以规避不必要的"假"违例,当然也可以不指定virtual clock,只是每次分析时序时都需要检查并排除这种"假"违例,影响了工作效率。