本文用于自我学习,也用于讨论,聚焦于个人认为的重点框架和重点内容,由于每个人的知识盲点不一样,可能会忽略了您认为的其他重点,若如此,也欢迎提出探讨,如果本人确实已知,会尽量解答。尽量不太涉及具体的寄存器。

3.8 PCIe RAS

主要包含了四个基本组成部分:

为了能够理解后面的内容,需要解释以下几个名词:

LCRC是链路CRC,它在数据链路层为通过链路传输的每一个TLP(事务层协议数据包)生成和校验。其目的是检测链路上的传输错误。

ECRC(端到端CRC),它由发送方在事务层生成,并在数据包最终目标的接收端的事务层进行校验。

Flit FEC是前向纠错(Forward Error Correction)技术在Flit层面的应用,核心作用是主动纠正传输过程中的误码。

DES是Debug, Error Injection, and Statistic gathering的首字母组合。

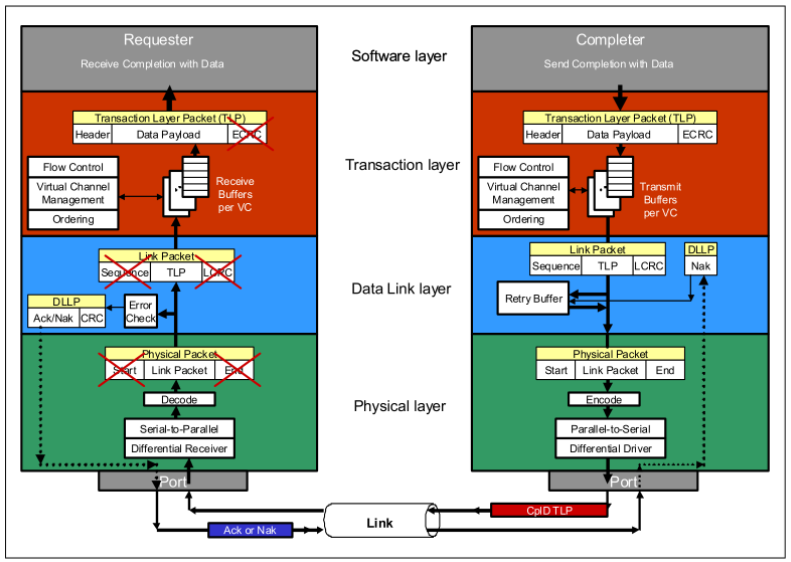

***讨论:*到这里,会有些同学好奇,在AER的机制中,已经有了LCRC,ECRC,如下图所示,LCRC发生在数据链路层,ECRC发生在传输层,那么RAS是不是冗余了这些保护操作呢?这里需要理解RAS和AER的关系,随着PCIe技术迭代(如PCIe 6.0),RAS架构在AER基础上进一步扩展:新增链路保护(如ECRC、FEC)、数据路径保护(RAM/控制信号保护)、调试统计(Error Injection/State Logging)等功能,形成更完整的系统级容错体系。而 AER(Advanced Error Reporting) 是PCIe设备的"高级错误报告"机制。AER是RAS架构中"错误报告"的核心子模块,RAS则是基于AER信息,整合多维度技术(链路保护、数据路径保护、调试统计等)实现系统级容错的完整架构。所以AER的手段在介绍RAS的时候,当然也会涉及。

3.8.1 RAS Data Protection(RAS DP)

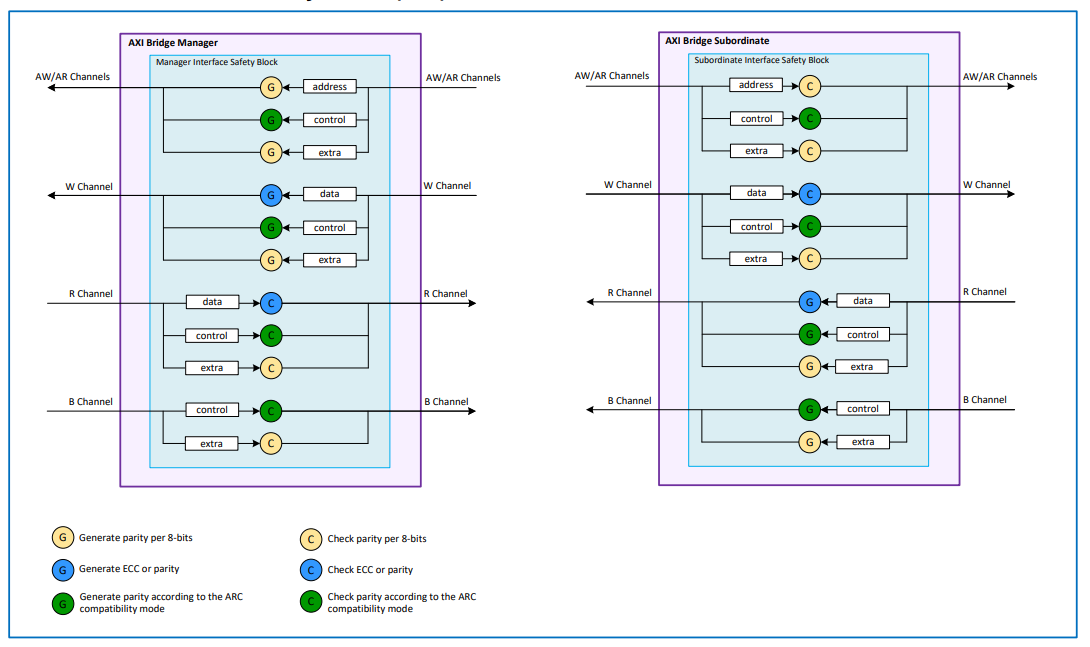

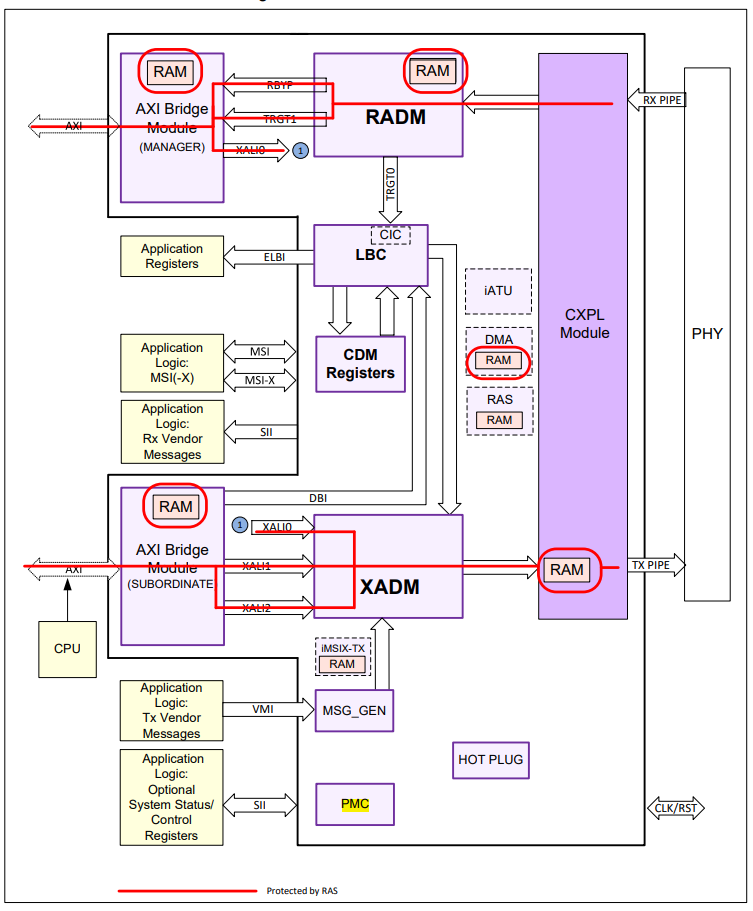

主要包括RAM Protection和DataPath Protection,其中RAM Protection的保护手段就是ECC和Parity,所指的RAM也是控制器里的RAM,其中不包括DES部分。而DataPath Protection的保护手段也是ECC和Parity,所指的数据路径包括本地PCIe 控制器和AXI接口,可参考下面的图基本理解其原理。

从上面的图中,可以看出,每个AXI通道的出口会自动产生校验码,入口会自动check校验码。

上图中,基本也能看出RAS所保护的RAM和数据通路。

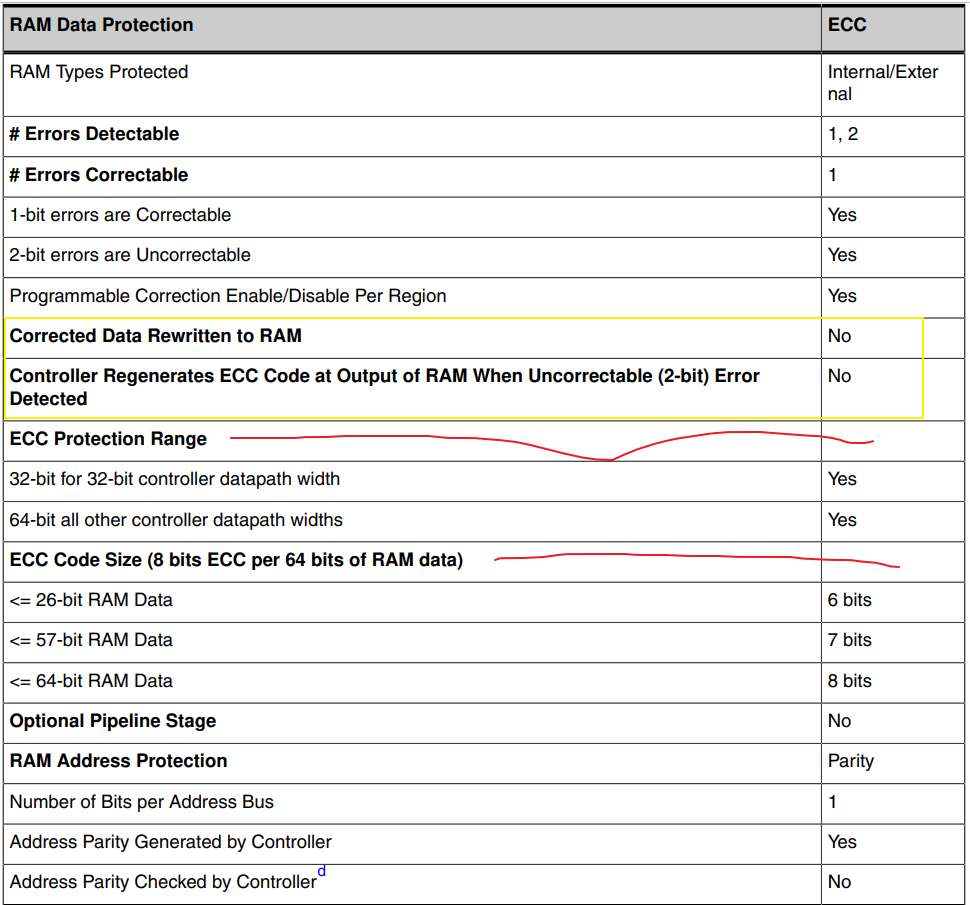

同时也有些表格说明RAS的保护属性,主要是介绍具体的保护方法,如ECC的范围,多少个bit等,什么时候用ECC,什么时候用Parity,ECC的保护有什么特性之类的,为了帮助更形象地快速理解,又不占用太多篇幅,下面简单贴了一张表供参考,详细请查看spec。

注意:表中划红线的条目是包括下面内容的条目,表格上容易混淆,以为它就是配置项但有没有ECC。

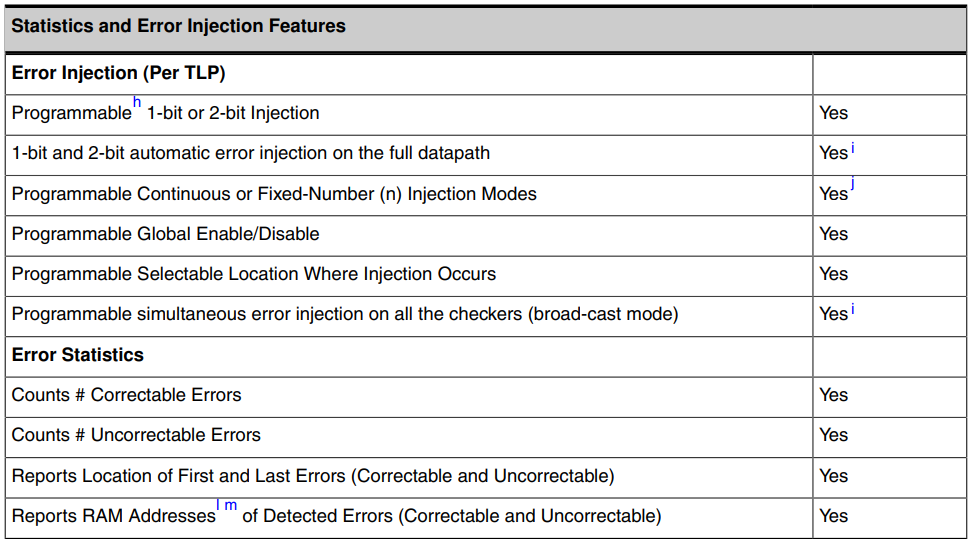

也介绍些这个阶段的错误注入功能,如下表所示,表中列出了支持的错误注入功能和错误统计的功能,也包含在后面的章节中。

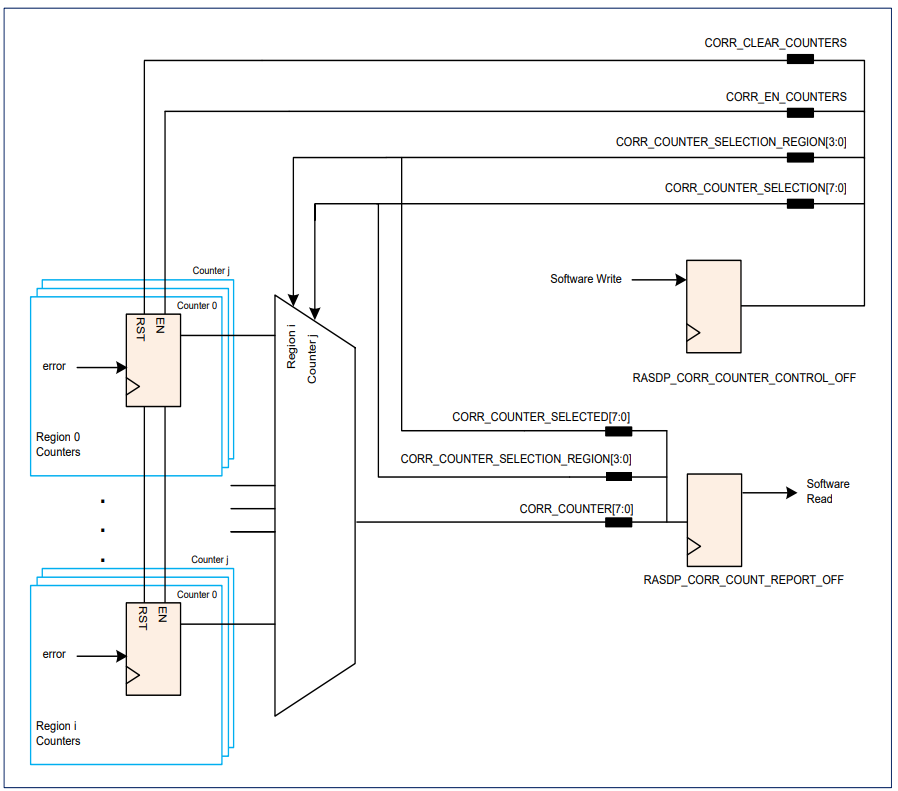

下图解释了软件是操作RAS模块去获取事件计数的流程图。软件可以通过写操作去控制counter寄存器的清/使能/选择区域/选择编号。可以通过读操作配合前面的写操作,可以读到想要的counter。

Uncorrectable Error Handling

处理就是要么PCIe link down

要么就是另一种就是RAS DP Error Mode的处理流程了

如果是

TX TLP Handling

RX Errored TLPs 需要转发到应用层。

后续接收到的TLP不保证正确性,必须丢弃。

TX TLP Handling(32-bit, 64-bit)

Bad TLP 会被清楚并传输

后续的TLP被清楚并传输

正在进行的重放被清除并传输

后续的重放被静默丢弃

TX TLP Handling(128-bits, 256-bit and 512-bit)

Bad TLP被静默丢弃

后续TLP被静默丢弃

正在进行的重放被清除并传输

后续重放被静默丢弃

讨论:

这些策略的差异,本质是平衡"错误隔离"与"链路效率":

- 32/64位配置下,系统更倾向于"主动传输错误信息"以快速触发处理;

- 128/256/512位配置下,系统优先"丢弃错误数据"以减少链路负担,但保留Replay的"错误标记传输"以保障重传机制的完整性。

触发错误处理流程:错误TLP到达接收端后,触发RAS机制的错误处理流程(如错误日志记录、错误上报、链路隔离等);

隔离错误影响:通过"传输错误TLP"而非直接丢弃,系统能精准定位错误源(如哪个设备、哪个链路段),避免错误扩散到其他链路或设备;

障链路稳定性:若直接丢弃错误TLP,链路可能因"数据包缺失"触发更严重的错误(如超时、链路复位);而"清除并传输"能维持链路的连续性,为后续错误处理争取时间。

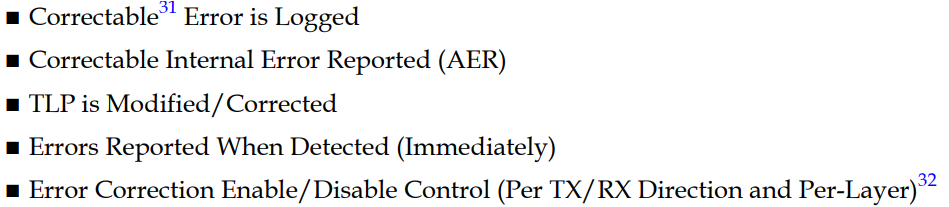

Correctable error handling:

3.8.2 RAS Debug, Error Injection, and Statistics

Debug

一般诊断(传统内部探针点):IP提供相应的引脚信号去诊断控制总线和每个控制模块的重要状态信号

硅片调试支持(PIPE、去偏、Ack/Nak、反转、FC、EQ、LTSSM、重放的控制和状态):

IP提供些引脚信号和寄存器表征调试状态和信息

LTSSM监控支持:LTSSM Monitor,通过IP提供的监控器能够监控到更多LTSSM的细节。

Error Injection

IP提供了一系列寄存器去设置错误注入,这些错误注入覆盖上述内容。

Statistics

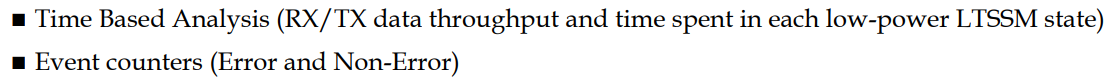

第一个功能是我们可以获取有关控制器在各低功耗LTSSM状态下的RX/TX数据吞吐量和花费时间的信息。下图描述了基于时间的分析寄存器访问框架,从图中可以看出,软件通过配置寄存器选择了监控开启和停止,选择信号,选择报告等等,然后再通过软件读的操作,把结果读出来。

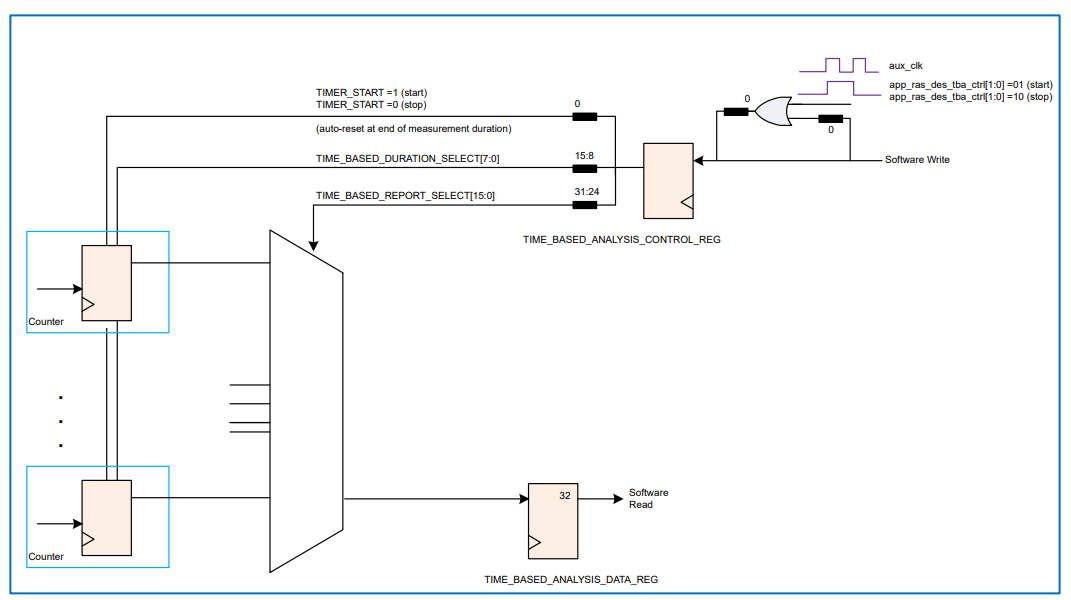

Event counters:

事件计数寄存器访问,软件通过写操作去执行事件计数模块的 清除/使能/事件选择/lane选择等操作,通过读操作区执行结果读回。

事件主要包括Decode Error, sync header error, ebuf overflow等等