协议配置寄存器中配置:

EoTp默认使能,设置为0:

PixelFormat像素格式为RGB888,读出应为0x3E;

BLLP Mode在该模式中未使用,设置为0;

Blanking Packet type未使用,设置为0:

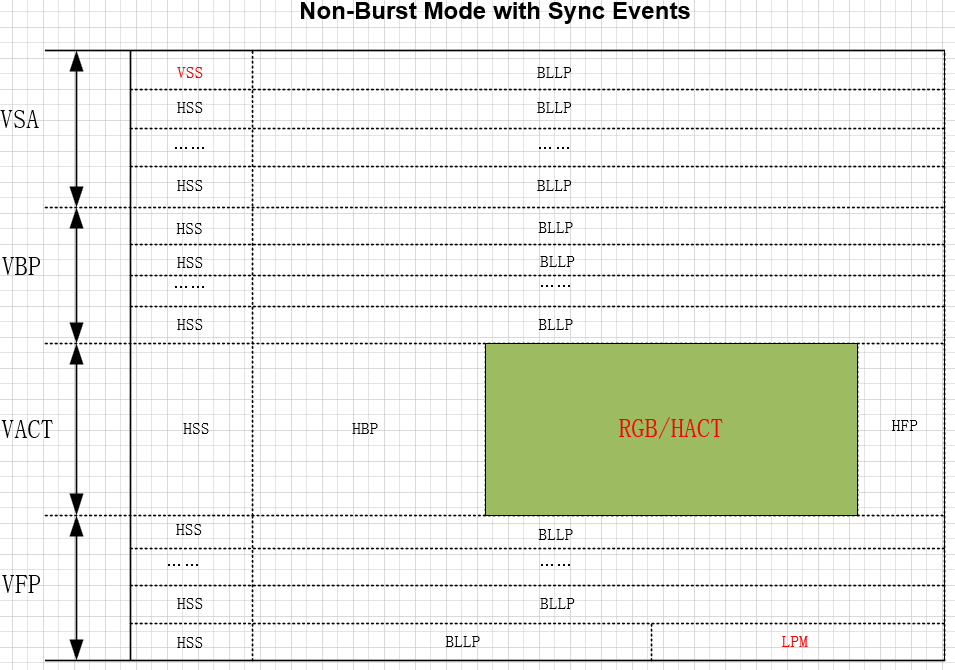

Video Mode使用Non-burst mode with Sync Events模式,设置为0x1;

Active Laness使用2lane,读出应为0x1;

此寄存器应配置为32'h3F09。

DSI时序寄存器配置:

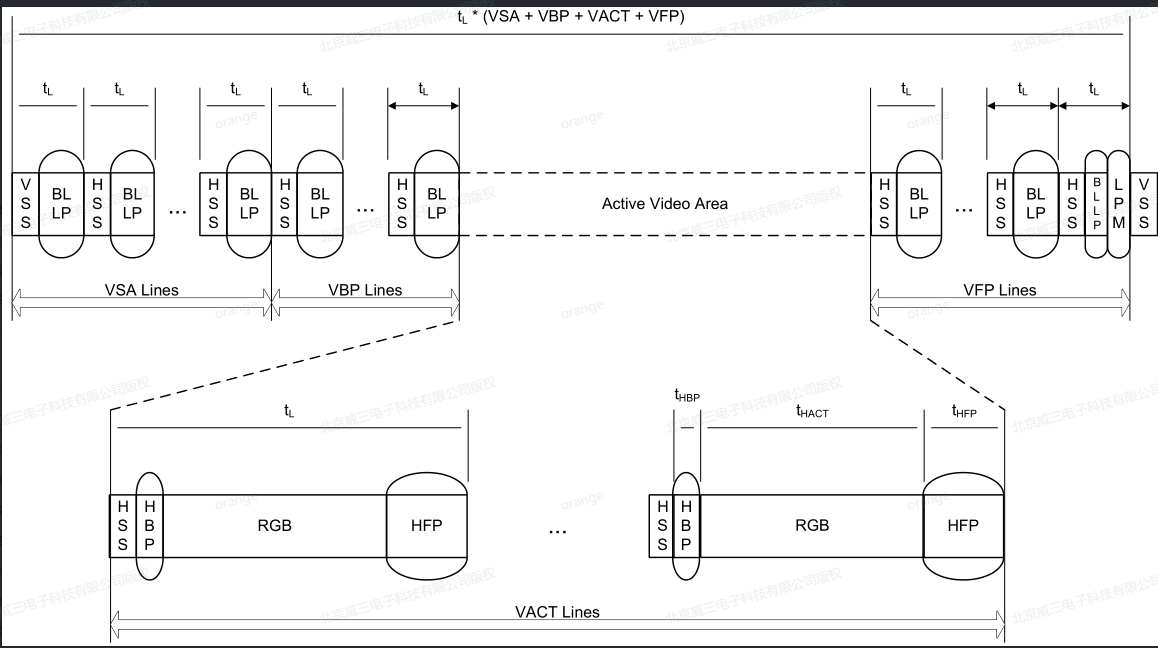

本文选择的图像模式为syncevents模式,从下图结构可以看出:

本文需要配置的行有关的寄存器:HBP、HACT(RGB)、HFP,以字节为单位,HSS为固定的包,不需要在寄存器中配置;

列有关的寄存器:VSA、VBP、VFP、VACT,以行为单位;其他寄存器配置为0即可;

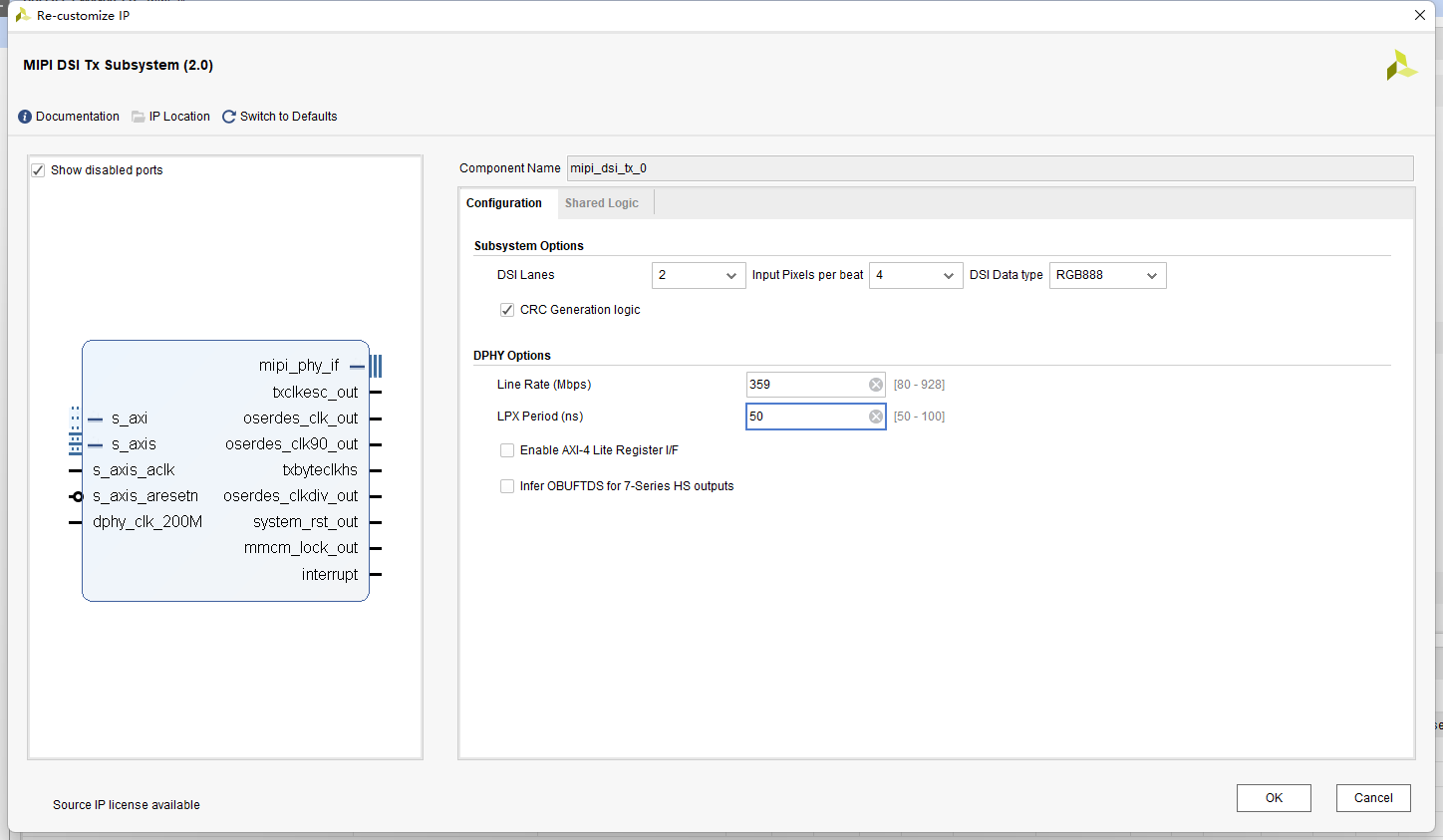

首先确定的参数:计算开始前先确定的参数:MIPI参数:

DataType :RGB888,3 byte or 24 bitsVideo Mode : Sync Events

Lanes :2

时序参数:

Horizontol Active : 480 pixels

Horizontol Blanking : 120 pixels

Vertical Active :800 lines

Vertical Blanking : 30 lines

Frame Rate : 60 fps

Clock Frequency:50Mhz(axistream的时钟)

获取HACT 和VACT:

一行有效的像素是HorizontolActive为480pixels,且像素是RGB888格式,每个像素点占3个字节:

HACT=480*24/8=1440=0x5A0

每帧的有效行是800行:

VACT=800=0x320

获取每行包结构的几余字节数量:Video模式是:Sync Events该模式下一行由:HSS+HBP+HACT+HFP 这几部分组成:

水平同步开始标志HSS:使用短包,占用4字节

HBP、HFP、HACT:使用长包,长包的组成是4字节头部+N字节数据+2字节检验码

每行花费在头尾部的字节数=4+(4+2)*3=22字节

计算HBP、HFP:XilinxIP使用手册中说明可按照HBP:HFP,以5:1的比率进行分配:

一行中空白部分的字节数量为:120pixels*3=360

除包结构几余后的空白部分字节数量为:360-22=338

HFP=338/6=56=0x38

HBP=338-56=282=0x11A

这里为了计算方便,将前置条件的120pixels的行空白设置为由一行的包结构冗余和发送的行空白字节组成,也就是行空白由22个字节的冗余,和HBP和HFP组成的338个空白字节组成共360字节,按RGB888格式就是120pixels;

计算VSA、VBP、VFP:XilinxP使用手册中说明可以1:1:1的比率进行分配:行空白共30行:

VSA=10=0xA

VBP=10=0xA

VFP=10=0xA

时序参数总结:HACT=1440=0x5A0

HFP=56=0x38

HBP=282=0x11A

VACT=800=0x320

VSA=10=0xA

VBP =10=0xA

VFP=10=0xA

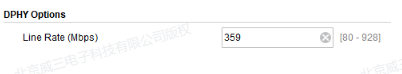

计算线速率:

使用以下公式计算线速率:

Line Rate= 行总字节数量*总行数*每字节比特数*帧率/ane数量/(10^6)Mbps=(HACT+HFP+HBP+22)*(VACT+VSA+VBP+VFP)*8*60/2/1000000 Mbps

=1800*830*8*60/2/1000000 Mbps

=358.56 Mbps

在IP配置时,向上取整为359Mbps即可。

DCS显示屏初始化参数:

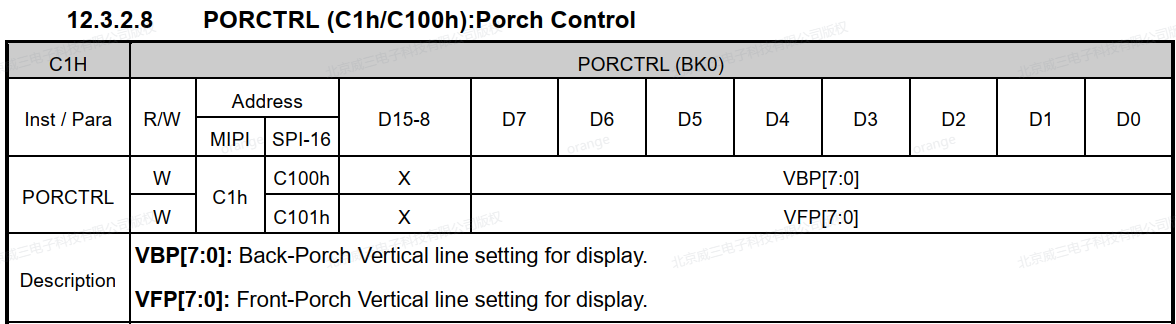

关注参数:PORCTRL(C1H)参数:

从上图可以看出,该参数的MIPICMD命令为C1h,且需要写两个字节的数据,所以需要使用长包进行发送:

CMD=0xC1 DATA=0x0A0A

该参数用于配置VBP和VFP时序参数;

参数中VBP和VFP的值在之前时序参数处计算得出。

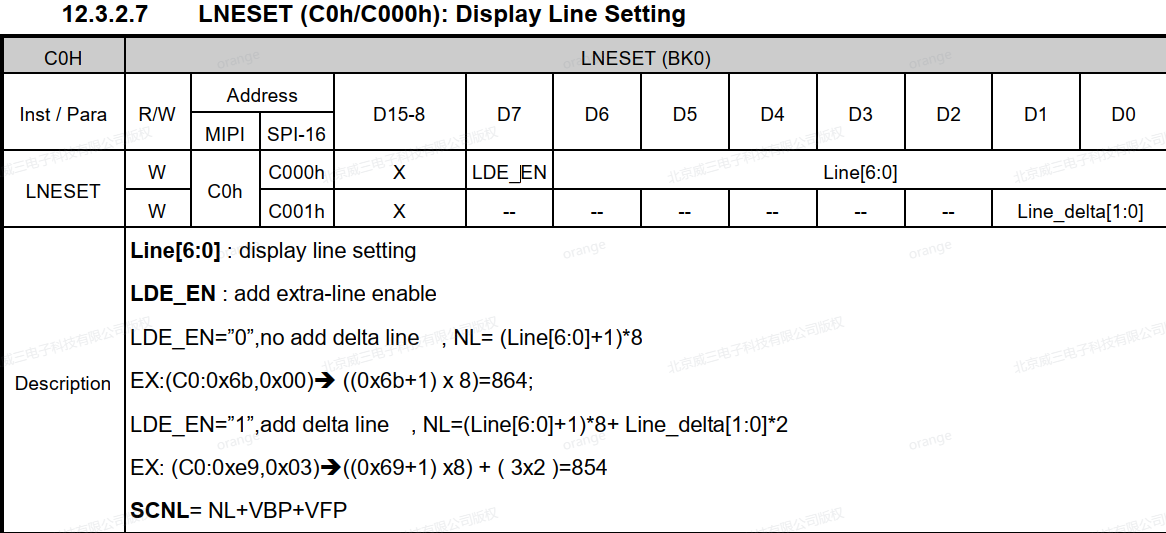

LINESET(C0H)参数

该参数用于配置显示屏有效显示的行数量:本次实验LCD屏幕分辨率为480*800,VACT为800行,VSA设置为10行,此处SCNL=NL+VBP+VFP ,所以NL=VSA+VACT=810;

此处,将Line[6:0]设置为7'h64,LDE EN和Line delta设置为1即可,NL=(Line[6:0]+1)*8+LDE EN*Line delta*2=(7'h64+1)*8+1*1*2=101*8 +2=810:

发送参数为:

CMD=0XC0 DATA =0X01E4

AXI4 Lite读写模块实现:

主机小写,从机大写

用户初始化DSITXIP和发送DCS命令初始化显示屏驱动芯片都是通过AXI4Lite接口读写IP内部的寄存器实现的。所以在读写寄存器之前需要先学会AXI4Lite的读写时序。

1.AXI4 Lite介绍:

AXl表示Advanced eXtensible Interface(高级可扩展接口),由ARM制定,包含在高级微控制器总线架构AMBA标准中。

AXI4接口分为3种类型:

AXI4-FULL:用于高性能存储器映射需求,例如后续要使用的DMA操作就要使用AXI4-FULL;

AXI4-Lite:用于简单的低吞吐量存储器映射通信,例如本次对IP的寄存器读写;

AXI4-Stream:用于高速流传输数据,例如本次对IP发送像素流数据就使用AXI4-Stream。

AX14-Lite特性:

传输的突发长度为1;

每次只能传输1个数据;

AX14-Lite通道:

AXI4-Lite分为5个通道:

读事务相关:读数据通道(read data)、读地址通道(read address)写事务相关:写数据通道(write data)、写地址通道(writeaddress)、写响应通道(writeresponse)

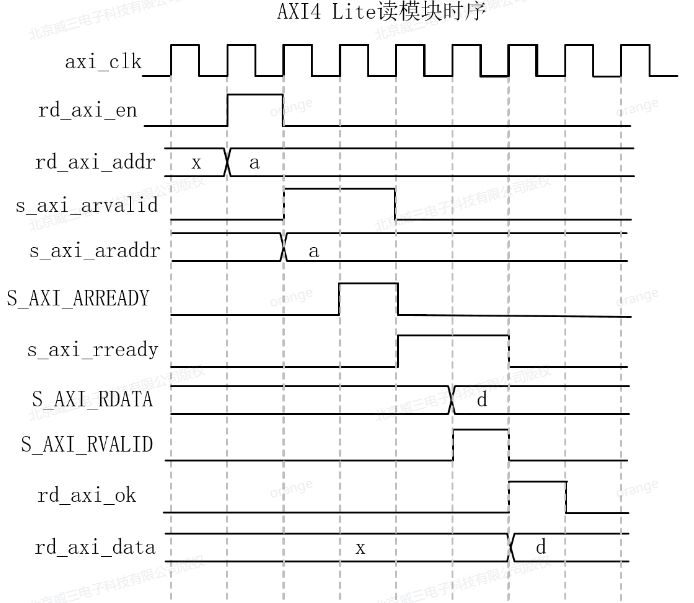

AX14-Lite读模块

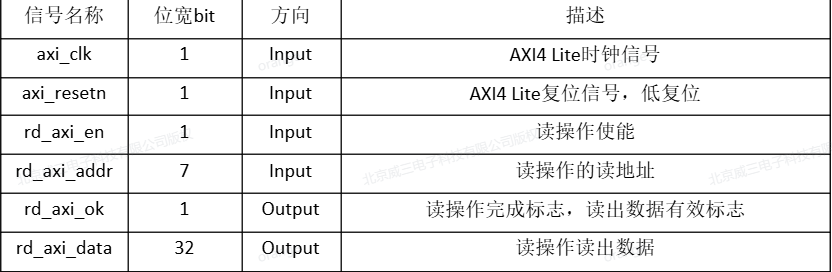

读事务接口信号:

本次实验中,用户是主机,IP是从机。

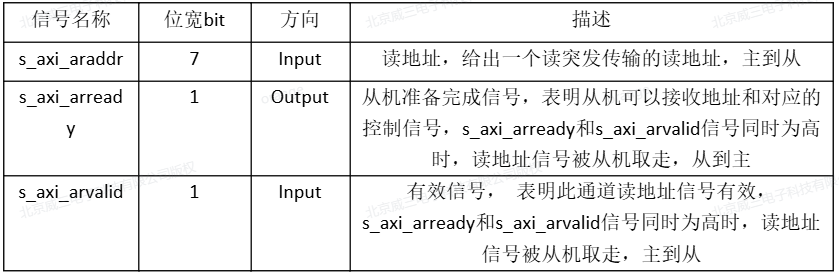

读地址通道信号:

读数据通道信号:

用户信号和时钟复位:

读模块,只需要给出读使能rd_axien和读地址rd axi addr,就可以根据读数据有效标志rd axi ok来获取读取出的数据rd axi data。

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2025 All rights reserved

// -----------------------------------------------------------------------------

// Author : lvjitao lvjitao_o@163.com

// File : axi_lite_rd.v

// Create : 2025-11-10 09:00:48

// Revise : 2025-11-10 09:29:02

// Editor : sublime text3, tab size (4)

// -----------------------------------------------------------------------------

`timescale 1ns/1ps

module axi_lite_rd(

input wire axi_clk,

input wire axi_resetn,

//axi lite read data chn1

output reg s_axi_arvalid,

output reg [6:0] s_axi_araddr,

input wire S_AXI_ARREADY,

//AXI lite READ DATA CHNL

input wire S_AXI_RVALID,

input wire S_AXI_RDATA,

output reg s_axi_rready,

input wire [31:0] S_AXI_RRESP,

//user

input wire rd_axi_en,

input wire [6:0] rd_axi_addr,

output reg rd_axi_ok,

output reg [31:0] rd_axi_data

);

//read addr channel

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

s_axi_arvalid <= 1'b0;

end

else if (S_AXI_ARREADY == 1'b1 && s_axi_arvalid == 1'b1) begin

end

else if (rd_axi_en == 1'b1) begin

s_axi_arvalid <= 1'b1;

end

end

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

s_axi_araddr <= 'd0;

end

else if (s_axi_arvalid == 1'b1) begin

s_axi_araddr <= rd_axi_addr;

end

end

//read data channel

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

s_axi_rready <= 1'b0;

end

else if (S_AXI_RVALID == 1'b1 && s_axi_rready == 1'b1) begin

s_axi_rready <= 1'b0;

end

else if (s_axi_arvalid == 1'b1 && S_AXI_ARREADY == 1'b1) begin

s_axi_rready <= 1'b1;

end

end

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

rd_axi_ok <= 1'b0;

end

else if (S_AXI_RVALID == 1'b1 && s_axi_rready == 1'b1) begin

rd_axi_ok <= 1'b1;

end

else begin

rd_axi_ok <= 1'b0;

end

end

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

rd_axi_data <= 'd0;

end

else if (S_AXI_RVALID == 1'b1 && s_axi_rready == 1'b1) begin

rd_axi_ok <= S_AXI_RDATA;

end

end

endmoduleAXI4 Lite写模块:

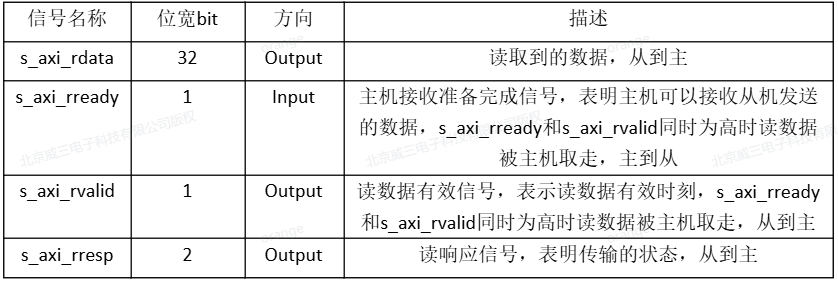

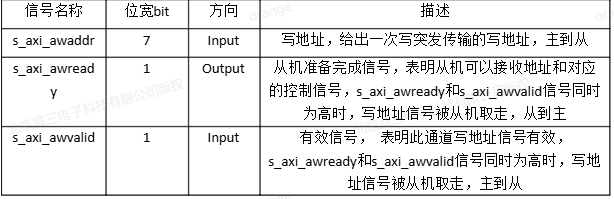

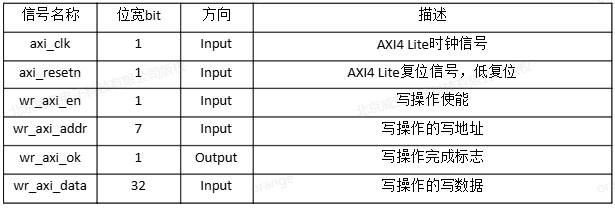

写事务接口信号:

(1)写地址通道信号:

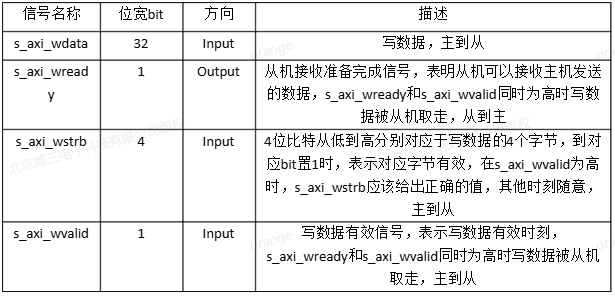

写数据通道信号:

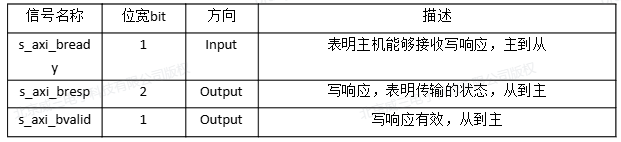

写响应通道:

用户信号和时钟复位:

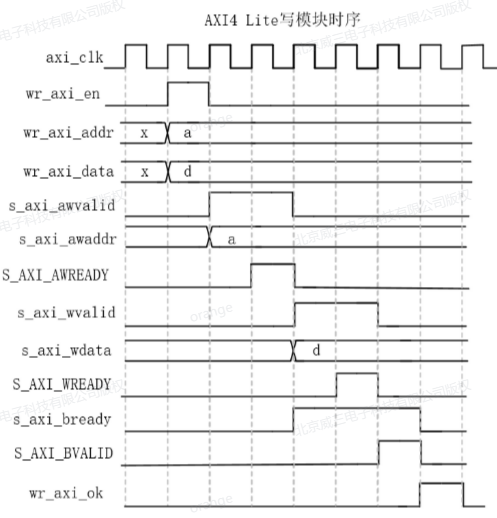

写事务时序:

写模块,只需要将写使能wr axi en、写地址wr axi addr和写地址wr axi data写入模块中,当写完成标志wr axi ok拉高,表示写操作完成。

谁提供数据,谁就要提供valid

// -----------------------------------------------------------------------------

// Copyright (c) 2014-2025 All rights reserved

// -----------------------------------------------------------------------------

// Author : lvjitao lvjitao_o@163.com

// File : axi_lite_wr.v

// Create : 2025-11-10 09:46:06

// Revise : 2025-11-10 10:42:54

// Editor : sublime text3, tab size (4)

// -----------------------------------------------------------------------------

`timescale 1ns/1ps

module axi_lite_wr(

input wire axi_clk,

input wire axi_resetn,

//axi addr

output reg s_axi_awvalid,

output reg [6:0] s_axi_awaddr,

input wire S_AXI_AWREADY,

//axi data

output reg s_axi_wvalid,

output reg [31:0] s_axi_wdata,

output reg [3:0] s_axi_wstrb,

input wire S_AXI_WREADY,

//axi rsp

output reg s_axi_bready,

input wire S_AXI_BVAILD,

input wire [1:0] S_AXI_BRESP,

//user

input wire wr_axi_en,

input wire [6:0] wr_axi_addr,

input wire [31:0] wr_axi_data,

output reg wr_axi_ok

);

//write addr channel

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

s_axi_awvalid <= 1'b0;

end

else if (s_axi_awvalid == 1'b1 && S_AXI_AWREADY == 1'b1) begin

s_axi_awvalid <= 1'b0;

end

else if (wr_axi_en == 1'b1) begin

s_axi_awvalid <= 1'b1;

end

end

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

s_axi_awaddr <= 'd0;

end

else if (wr_axi_en == 1'b1) begin

s_axi_awaddr <= wr_axi_addr;

end

end

//write data channel

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

s_axi_wvalid <= 'd0;

end

else if (s_axi_wvalid == 1'b1 && S_AXI_WREADY == 1'b1) begin

s_axi_wvalid <= 'b0;

end

else if (s_axi_awvalid == 'b1 && S_AXI_AWREADY == 1'b1) begin

s_axi_wvalid <= 'b1;

end

end

always @(posedge axi_clk) begin

if (axi_resetn == 1'b0) begin

// reset

s_axi_wdata <= 1'b0;

end

else if (wr_axi_en == 1'b1) begin

s_axi_wdata <= wr_axi_data;

end

end

//write response channel

always @(posedge axi_clk ) begin

if (axi_resetn == 'b0) begin

// reset

s_axi_bready <= 0;

end

else if (s_axi_bready == 1'b1 && S_AXI_BVAILD == 1'b1) begin

s_axi_bready <= 0;

end

else if (s_axi_awvalid == 'b1 && S_AXI_AWREADY == 1'b1) begin

s_axi_bready <= 1'b1;

end

end

always @(posedge axi_clk ) begin

if (axi_resetn == 'b0) begin

// reset

wr_axi_ok <= 'b0;

end

else if (s_axi_bready == 1'b1 && S_AXI_BVAILD == 1'b1) begin

wr_axi_ok <= 1'b1;

end

else begin

wr_axi_ok <= 1'b0;

end

end

endmodule