FPGA教程系列-Vivado中FIFO的简单仿真分析

本着看十遍不如操作一遍的原则,对FIFO进行一个简单的仿真,加深一下印象。

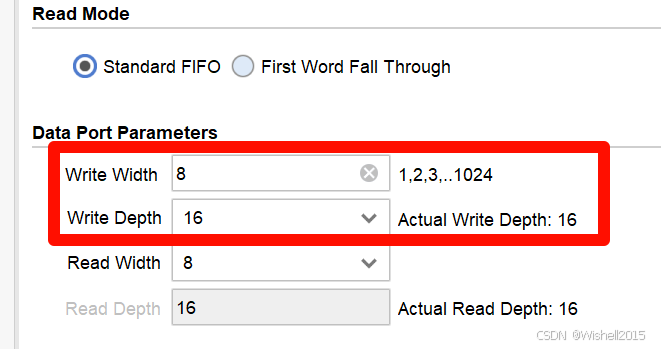

生成一个IP核:(8位,16深度,其他默认)

编写top文件:

verilog

`timescale 1ns / 1ps

module fifo_top(

input i_clk,

input i_rst,

input[7:0] i_din,

input i_wr_en,

input i_rd_en,

output o_full,

output o_empty,

output[7:0] o_dout

);

fifo_generator_0 fifo_generator_u (

.clk (i_clk), // input wire clk

.srst (i_rst), // input wire srst

.din (i_din), // input wire [7 : 0] din

.wr_en (i_wr_en), // input wire wr_en

.rd_en (i_rd_en), // input wire rd_en

.dout (o_dout), // output wire [7 : 0] dout

.full (o_full), // output wire full

.empty (o_empty) // output wire empty

);

endmodule 编写testbench:

verilog

`timescale 1ns / 1ps

module tb_fifo_top;

/* ---------------- 接口 ---------------- */

logic clk;

logic rst;

logic [7:0] din;

logic wr_en;

logic rd_en;

logic full;

logic empty;

logic [7:0] dout;

/* ---------------- 时钟 ---------------- */

initial begin

clk = 0;

forever #10 clk = ~clk;

end

/* ---------------- 激励 ---------------- */

initial begin

rst = 1;

wr_en = 0;

rd_en = 0;

din = '0;

repeat(5) @(posedge clk);

rst = 0;

@(posedge clk);

// 1. 写满 16 字节

$display("\n[%.2f ns] Write 16 bytes", $time);

for (int i = 0; i < 16; i++) begin

@(posedge clk);

wr_en = 1;

din = i;

end

wr_en = 0;

@(posedge clk);

$display("[%.2f ns] full = %b", $time, full);

// 2. 读出 16 字节

$display("\n[%.2f ns] Read 16 bytes", $time);

for (int i = 0; i < 16; i++) begin

@(posedge clk);

rd_en = 1;

end

rd_en = 0;

@(posedge clk);

$display("[%.2f ns] empty = %b", $time, empty);

// 3. 交替写读 3 次

$display("\n[%.2f ns] Alternating write/read", $time);

repeat(3) begin

@(posedge clk);

wr_en = 1; din = $random; rd_en = 0;

@(posedge clk);

wr_en = 0; rd_en = 1;

end

rd_en = 0;

@(posedge clk);

#200;

$display("\n[%.2f ns] Done", $time);

$finish;

end

/* ---------------- 打印读出数据 ---------------- */

always @(posedge clk) begin

if (rd_en & ~empty)

$display("[%.2f ns] dout = %0d", $time, dout);

end

/* ---------------- 例化 DUT ---------------- */

fifo_top dut (

.i_clk (clk),

.i_rst (rst),

.i_din (din),

.i_wr_en (wr_en),

.i_rd_en (rd_en),

.o_full (full),

.o_empty (empty),

.o_dout (dout)

);

endmodule仿真分析:

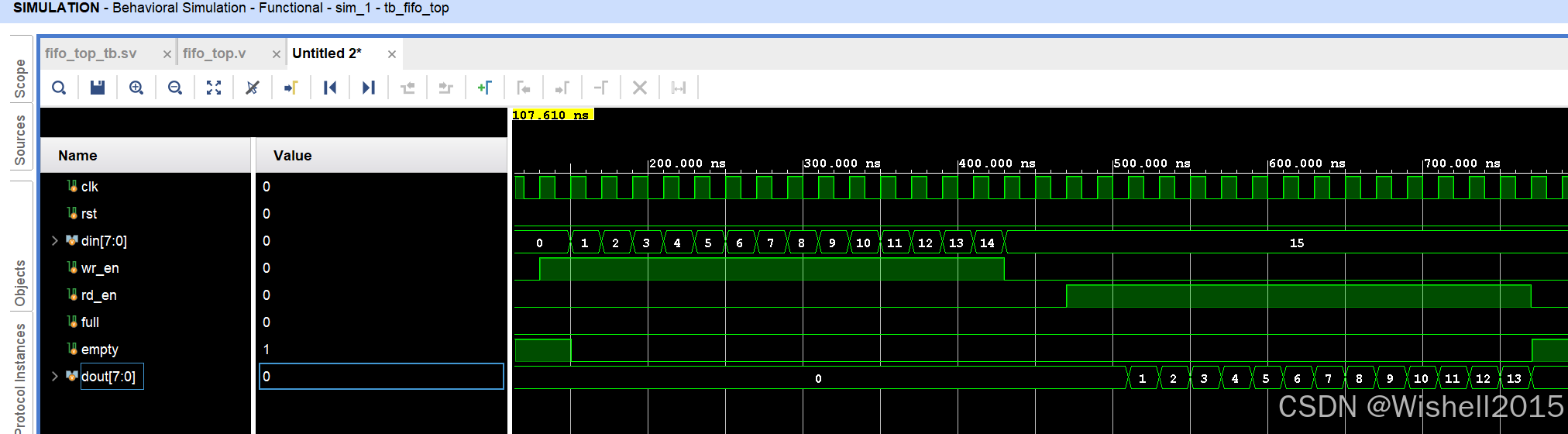

写入0-14数据,读出0-14.

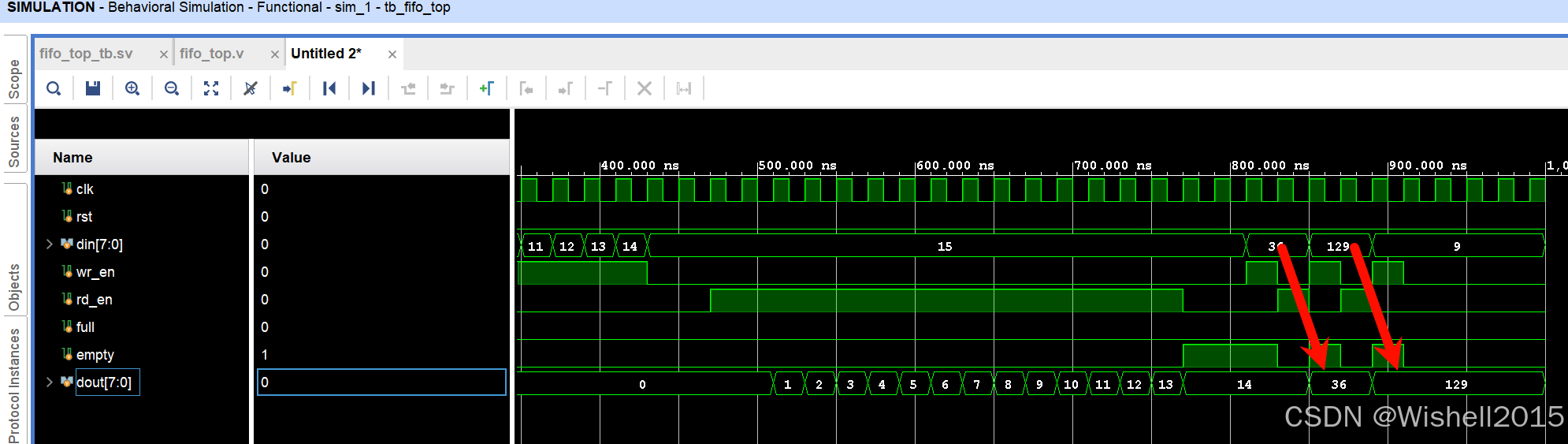

分别写入36,129并读出。

有心力的可以试试异步的fifo等等。。

工程文件:https://download.csdn.net/download/fantasygwh2015/92276755