牛头马面:你才是牛马成精,我们只是长得像而已

探查原因:测量18位分辨率ADC(f=2.5KHz时 ENOB有效位只有11位)

过程中发现ADC电源域LDO设计引发的相关问题以及ADC参数学习

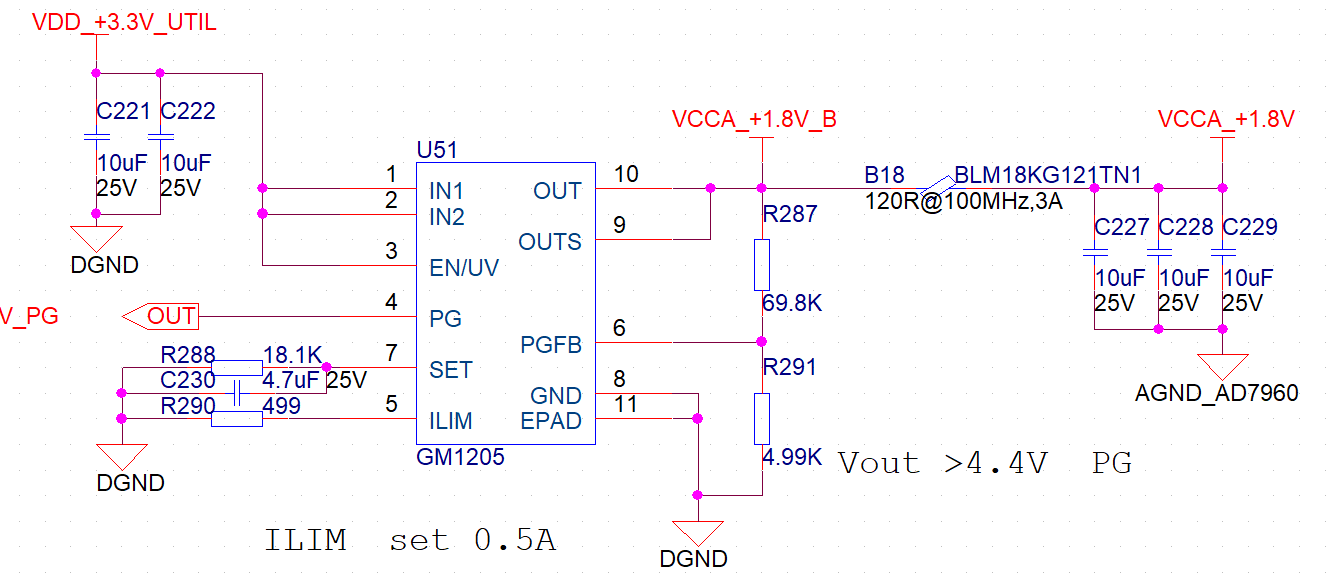

LDO设计以及测试波形

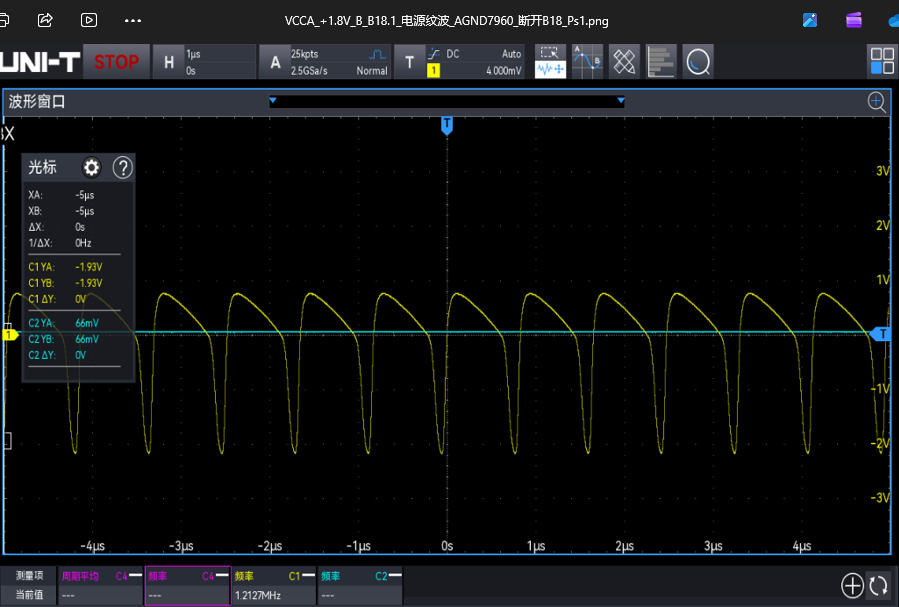

图1

图1

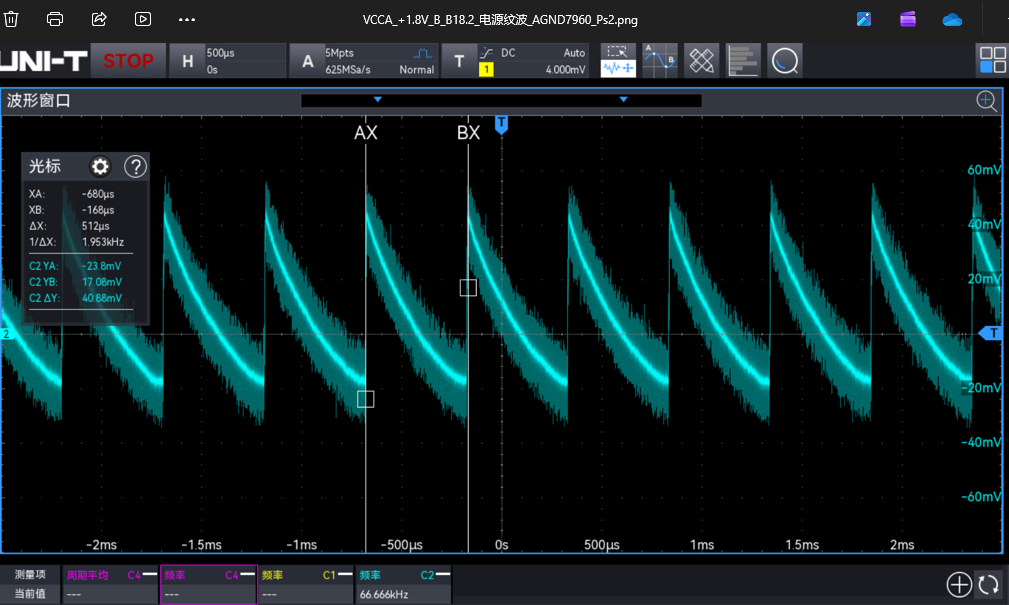

在B18磁珠右侧测得电源纹波

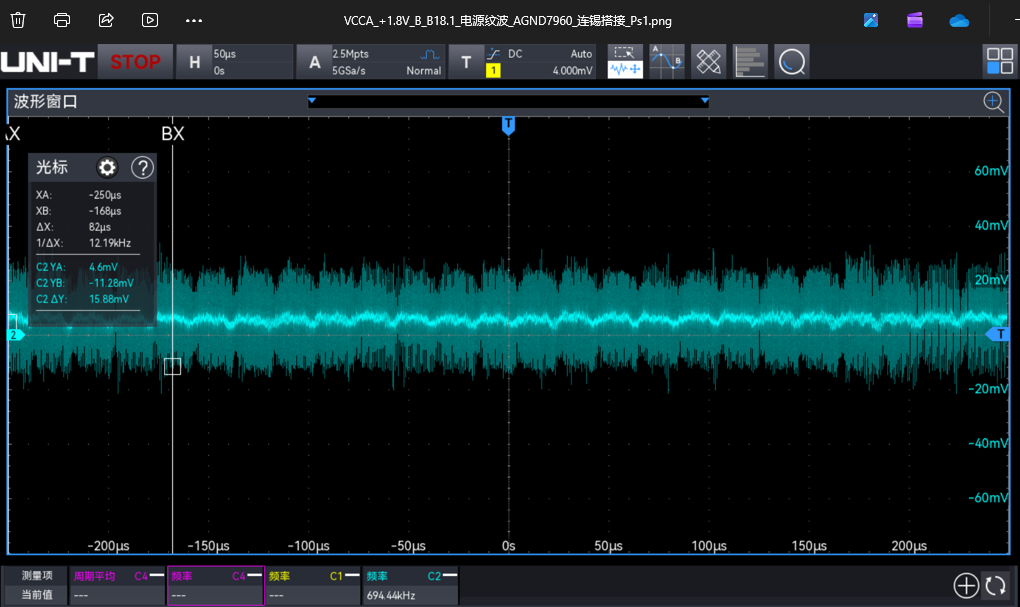

图2

图2

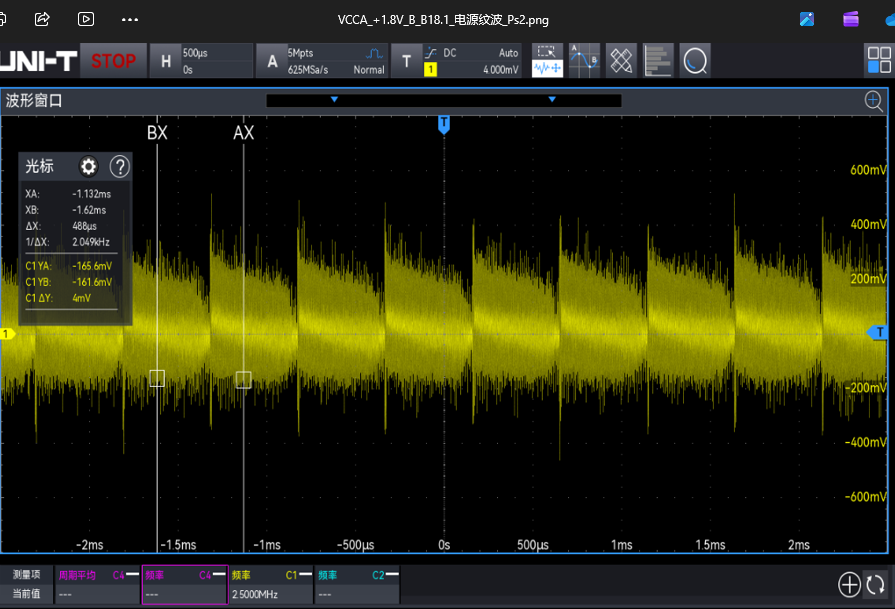

在B18磁珠左侧测得电源纹波

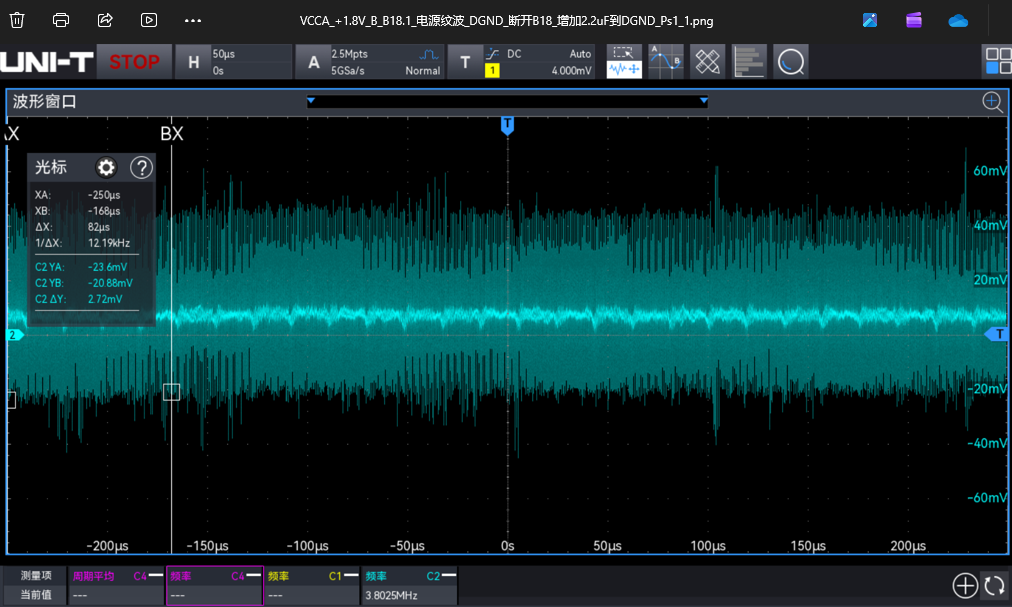

图3

图3

原因:LDO在设计时未在磁珠左侧放置输出电容

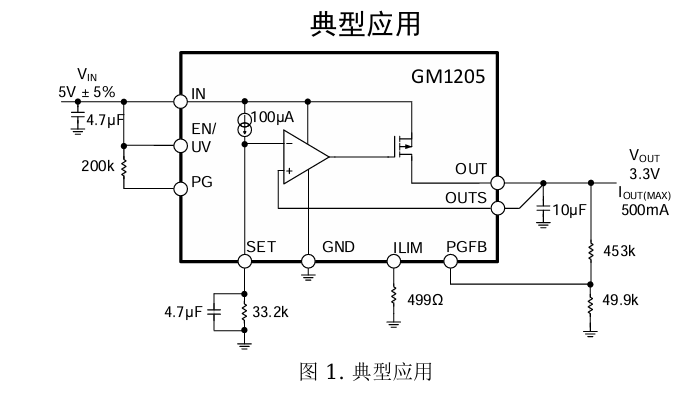

图4

图4

将磁珠B18断开后测试波形

图5

图5

将磁珠B18短接后测试波形

图6

图6

将磁珠断开后增加2.2uF电容对地

图7

图7

以上:

1、断开磁珠,没有输出电容,LDO无法正常工作,如图5。猜测,环路无法稳定,发生震荡;也有可能是测量时接地弹簧未接触好,不想测了,到时再说。

2、磁珠两端信号如图2和图3,设计中因为输出电容在磁珠之后,磁珠成为LDO环路的一部分,类似小感量电感,纹波通过时形成图2锯齿纹波

3、短接后类似设计上将输出电容靠近放置,对于输出电容是否必要,如链接仿真,LDO厂家一般推荐输出电容靠近LDO管脚放置,就是为了系统的性能考虑。在特殊情况下,这个电容是可以删除的,例如后端耗能器件很近,直接用后端输入电容作为LDO的输出电容。对于输出电容的容值,厂家会根据自身LDO进行优化,有的在不同PSRR要求或不同负载电流要求下的推荐容值也有差异,设计时要注意。

https://cloud.tencent.com/developer/article/2028299

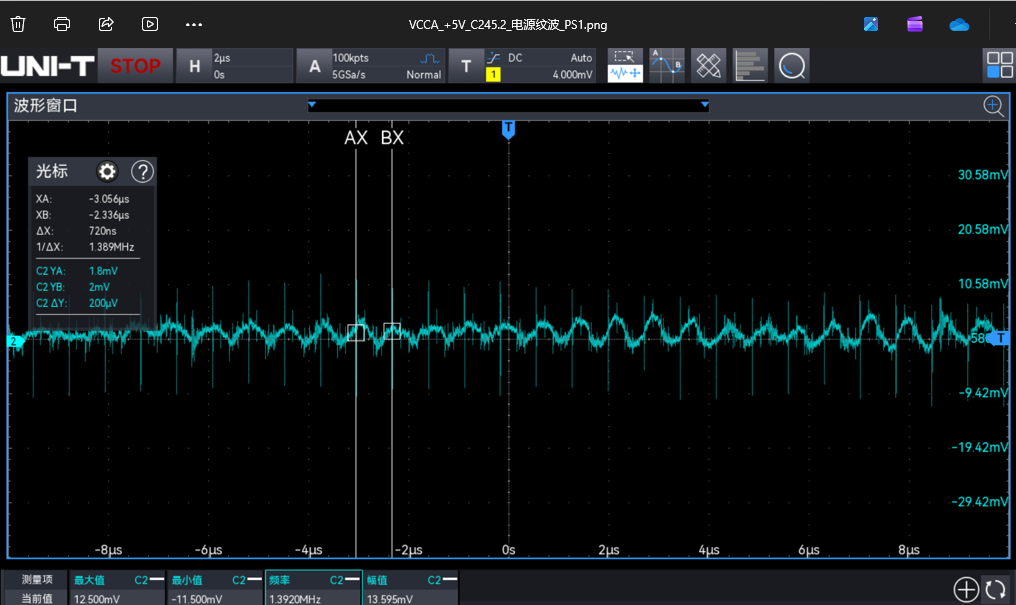

4、测量其他电源域时,发现均有1.4MHz纹波和毛刺噪声,如图8所示。但是在所有寻求FAE帮助测量时,频率变为了1MHz左右,难搞,未发现频率变化原因和纹波源头。猜测,1.4MHz来自同厂家的Buck电源GM6403,1MHz来自TI-Buck电源TPSM63606,均为开关噪声。未解决问题有两点,一是为什么同一块板子纹波频率在不同地方测量会改变,是因为两种纹波均存在吗?二是为什么所有电源域均存在,均存在可能导致TI那颗猜测的可能性更大一些,因为PCB布局上紧贴12V电源域(为隔离输入电源)。

图8

图8

ADC有效位反推LDO电源影响

在改变电路依旧没法找到纹波干扰源的情况下,FAE转换方式,决定根据ADC的有效位来观察是否是电源影响。依据有两点,一是查看改善电路设计后是否有效位发生变化(纹波有降低成10mV级别,原来的纹波可能未100mV级别),二是有效位计算公式中会将所有噪声积分包括基频谐波分量以及底噪,观察底噪查看电源纹波是否影响到噪声的dBm进而影响有效位。

几个缩写含义以及计算公式

Fund Amplitude 基波振幅

基波振幅描述了一个周期信号中,其最基本、最主要频率成分的强度大小

单位dBFS 相对于满量程的分贝值 dBFS = 20 * log10(当前采样值 / 满量程采样值)

-6dBFS =0.5

SNR Signal-to-Noise Ratio 信噪比

期望信号的功率与背景噪声功率的比值

SNR (dB) = 10 × log₁₀( P_signal / P_noise )

SFDR Spurious-Free Dynamic Range 无杂散动态范围

期望信号的功率与最严重的杂散分量的功率之比

SFDR (dB) = 10 × log₁₀( P_signal / P_spurious_max )

THD Total Harmonic Distortion 总谐波失真

THD衡量的是一个系统(如放大器、ADC)由于非线性特性,在输出信号中产生了多少不必要的谐波成分

THD (%) = [ √(V₂² + V₃² + ... + Vₙ²) / V₁ ] × 100%

THD (dB) = 20 × log₁₀( √(V₂² + V₃² + ... + Vₙ²) / V₁ )

SINAD Signal-to-Noise-and-Distortion Ratio 信号对噪声和失真比

SINAD是衡量系统性能的综合性指标。它表示有用信号的功率与所有其他不想要的成分的总功率(包括噪声和失真) 的比值

SINAD (dB) = 10 × log₁₀( P_signal / (P_noise + P_distortion) )

ENOB Effective Number of Bits 有效位数

ENOB将一个实际的数据转换器(ADC)的实际性能与一个理想的ADC进行比较。它表示,在实际的噪声和失真影响下,这个ADC的性能相当于一个多少位的理想ADC

ENOB = (SINAD (dB) - 1.76) / 6

Integrated Noise 总积分噪声

的是在一个特定的频率范围(带宽) 内,将所有噪声功率(或噪声电压/电流的平方)进行累加(积分)后得到的总噪声值

Average noise 平均噪声

一个描述噪声典型强度的术语。在绝大多数工程语境下,它指的就是噪声的均方根值,通过对噪声功率在特定带宽内进行积分再开方得到

ENOB计算

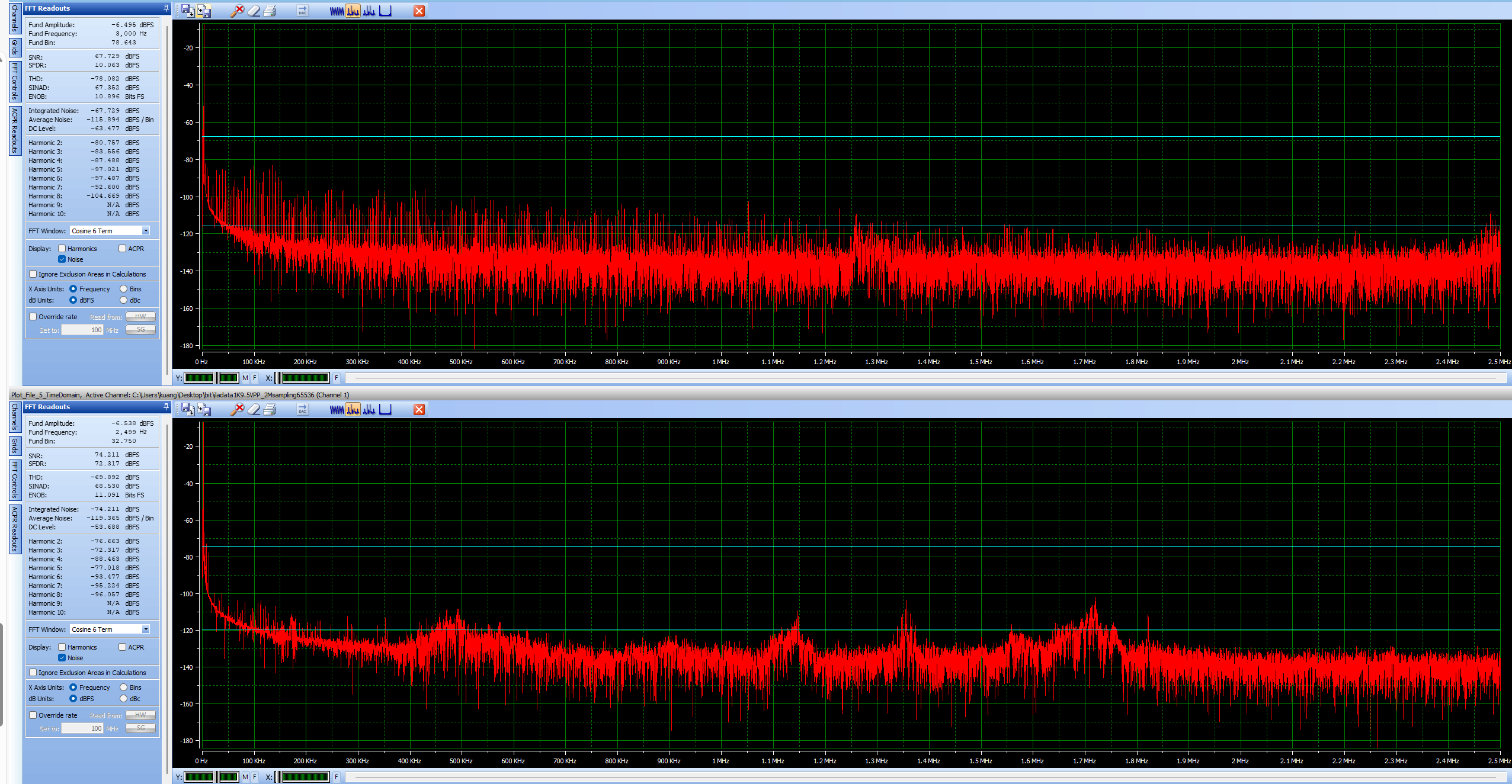

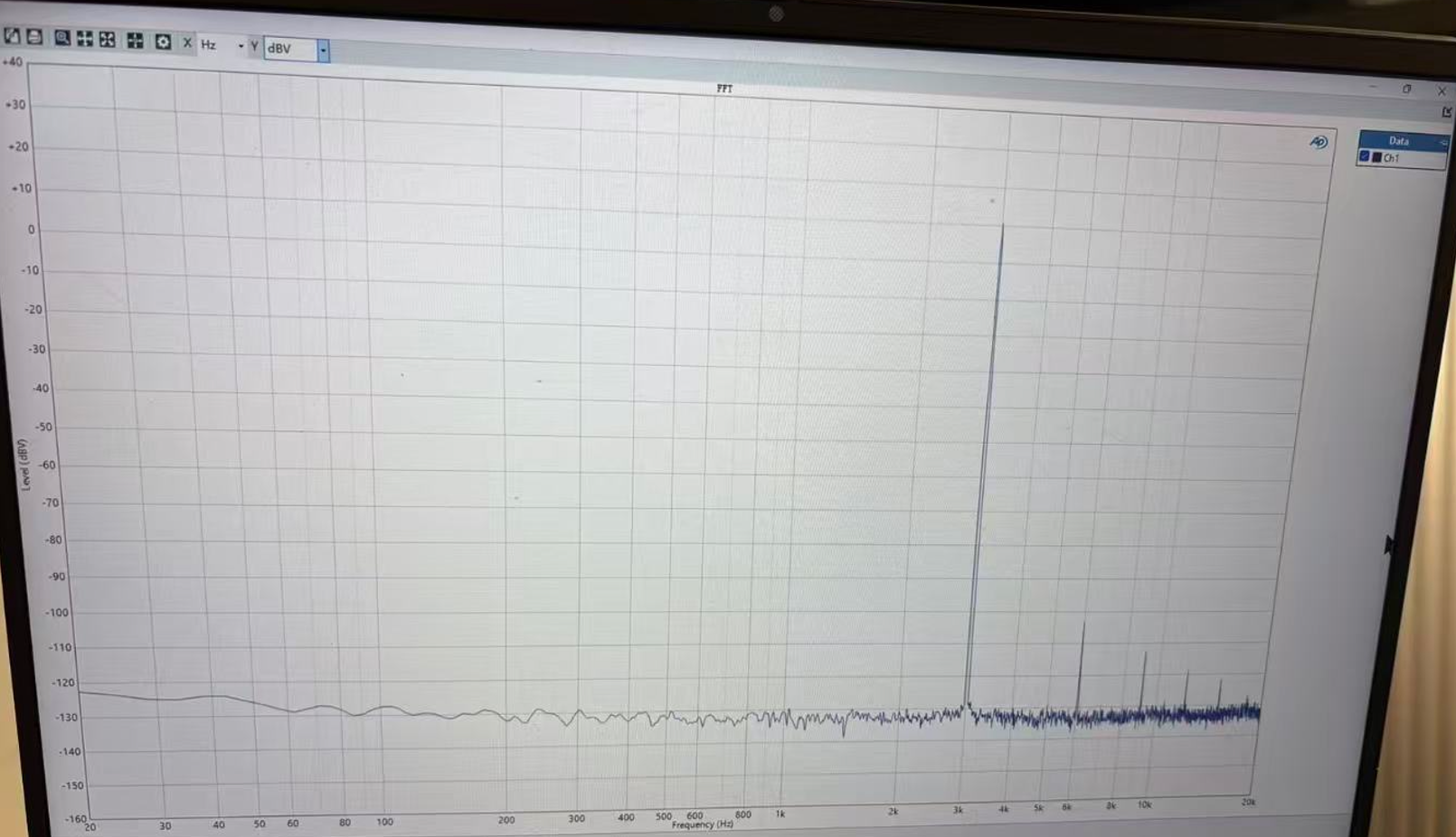

使用高精度信号发生器生成信号源输入板子,信号源如图10,具体多高精度不知道,谐波抑制看上去很好。ADC采集后FPGA收集后输出到Wavevision后FFT如图9

图9

图9

图10

图10

图9中上半图为改良设计后频谱,具体措施一是所有设计磁珠短接,二是将LDO的SET脚GND连接到输出的GND,三是将输入的低通滤波去除。

下半图为普通信号源的最初测试问题版本,也就是最初测试出11位有效位的版本

这块ADC采集1KHz信号的有效位在规格书为15.7

FAE看完后解释时谐波分量导致的。。。不是电源问题。。。可是THD反而是更优的

疑惑:

1、信号源谐波抑制不错,为什么FFT频谱上谐波分量较为明显?ADC引入的吗?

2、为什么纹波更大的初始测量SNR反而更好呢,平均噪声也更低?该电路时焊接导致还是环境改变导致的?

以上:

ENOB的计算公式上看,参考电源纹波会直接增加系统总噪声的底噪,从而降低整体的 SNR 和 SINAD,所以一定是有影响的,mV级别的纹波不能满足18位ADC的测量,但是谐波分量异常可能也是ADC中未设置正确