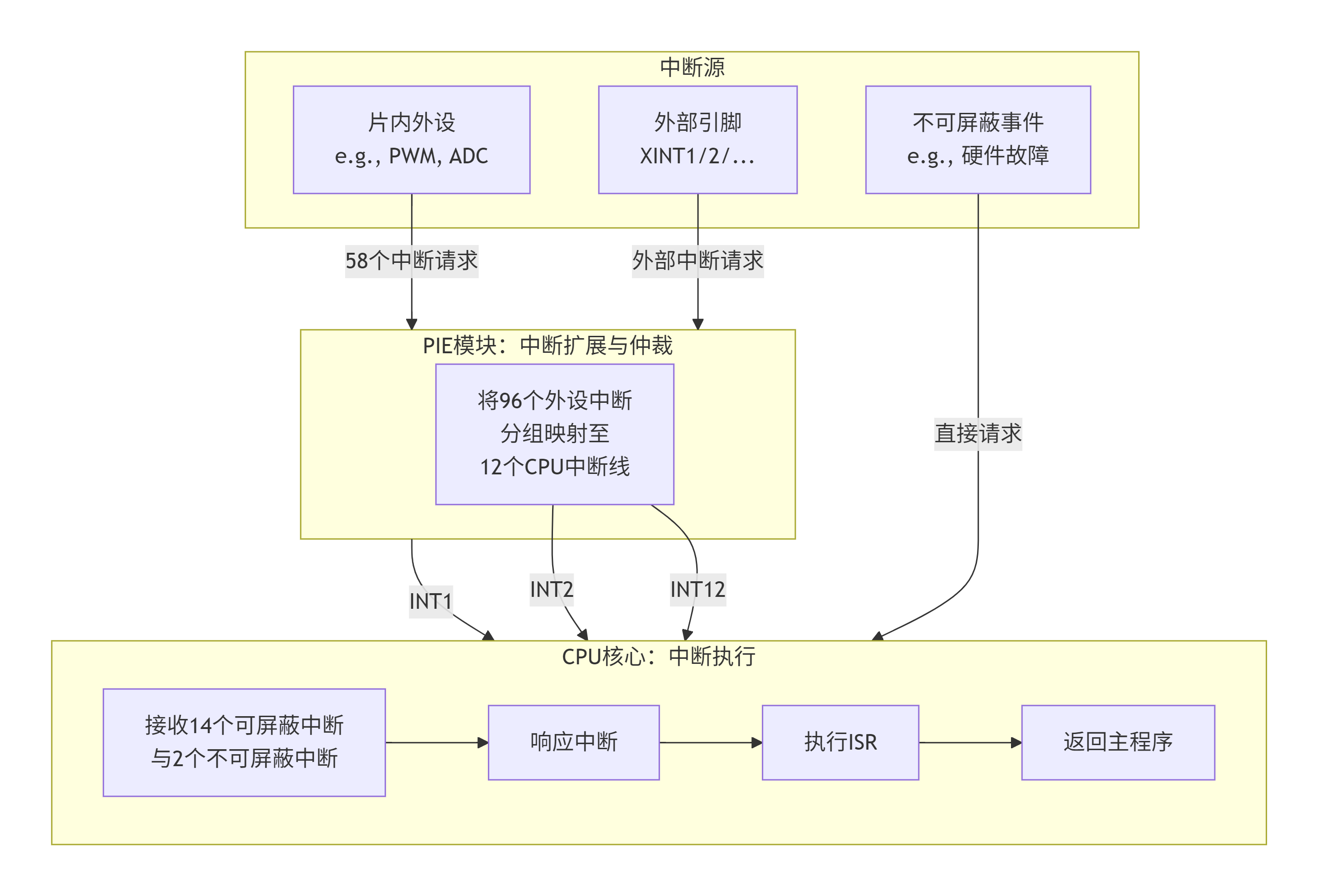

DSP F28335 中断系统详解

中断是由硬件或软件驱动的事件,它会使CPU暂停当前正在执行的主程序,转而去执行一个特定的中断服务子程序;当中断服务子程序执行完毕后,CPU会返回到主程序中原本暂停的位置,恢复现场并继续执行。这一机制使得CPU能够及时响应外部事件或处理内部紧急任务,大大提高了程序的执行效率。

一个通俗的比喻是:一位工程师正在编写代码(相当于CPU 执行主程序 ),此时电话铃声响起(相当于中断请求 ),他暂停手头的工作,去接听电话(相当于执行中断服务子程序 );通话结束后,他回到电脑前,从他刚才停顿的代码行继续编写(相当于返回主程序继续执行)。这个过程形象地模拟了CPU处理中断的完整流程。

F28335 的中断源分类

F28335的中断源丰富,可分为两大类:

- 片内外设中断源:由芯片内部集成的外设模块产生,如PWM、CAP(捕获)、QEP(正交编码脉冲)、ADC、SPI、SCI等。当这些外设完成特定操作(如PWM周期匹配、ADC转换完成、接收到串口数据)时,会向CPU发出中断请求。

- 片外中断源 :由芯片外部信号通过特定的外部中断输入引脚引入,主要是XINT1~XINT7等引脚。这些引脚可以直接连接按键、限位开关等外部数字信号,用于检测上升沿或下降沿事件。

F28335 的 CPU 级中断结构

在CPU级别,F28335设计了16个中断线(INT1~INT14,加上RESET和NMI),其结构如下图所示:

F28335的中断线可分为两种基本类型:

- 不可屏蔽中断( NMI )

- 特点 :拥有最高的优先级,用于处理系统中最紧急、最严重的故障事件(如系统复位RESET、看门狗超时、严重的硬件故障等)。CPU无法通过任何软件指令(如配置中断使能寄存器)来禁止或忽略这类中断的响应。一旦触发,CPU必须立即暂停当前任务进行处理。

- 例子:RESET(复位)和NMI(不可屏蔽中断)本身。

- 可屏蔽中断( INT1~INT14 )

- 特点 :这类中断的响应与否,可以通过软件进行灵活控制。程序员可以通过设置中断使能寄存器(如IER)来"使能 "(允许响应)或"屏蔽"(禁止响应)它们。当系统正在执行关键代码段,不允许被中断打扰时,可以暂时屏蔽这些中断;在条件允许时,再重新使能,让CPU处理外设的请求。

- 例子:绝大多数片内外设(如定时器、串口)和外部引脚(XINT)引发的中断都属于此类。

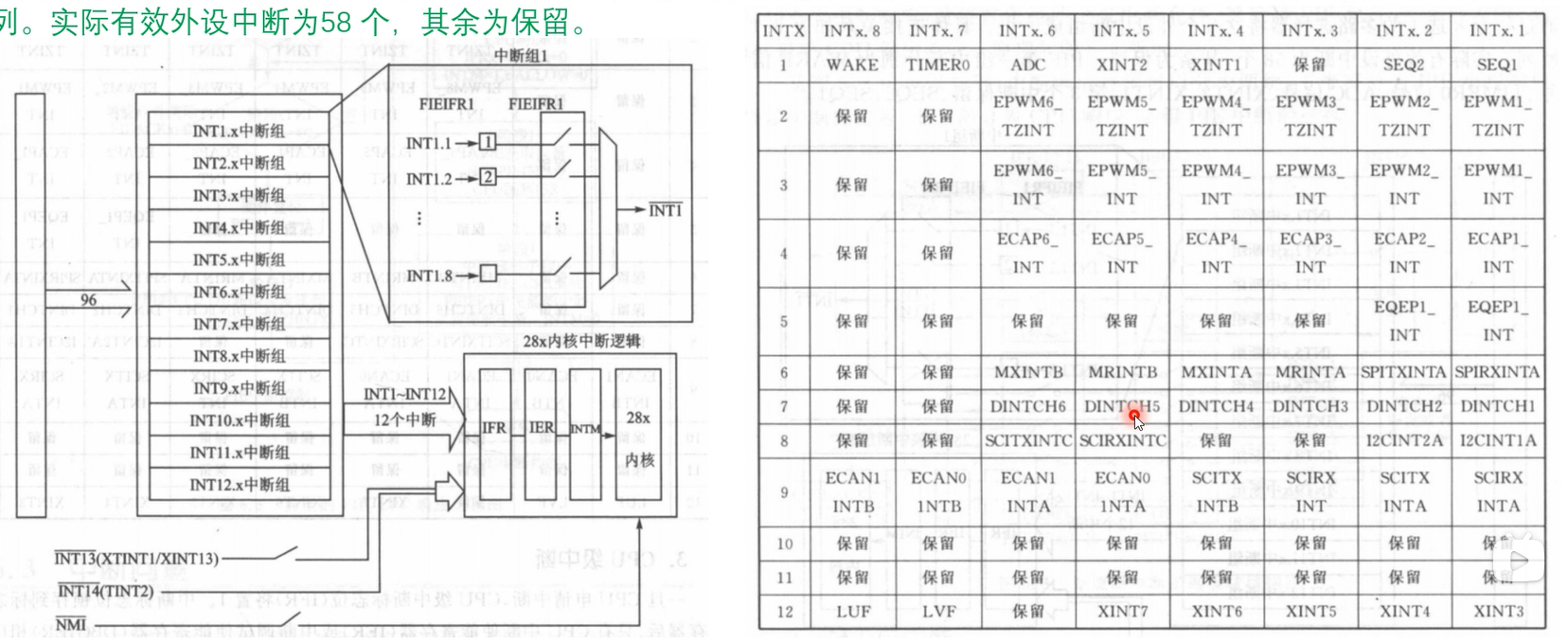

PIE (外设中断扩展)模块的核心作用

从图中可以看到,F28335丰富的片内外设中断源(多达96个)远多于CPU的14个可屏蔽中断线。为了解决这个矛盾,芯片内置了强大的PIE 模块 。

- 功能:PIE模块充当了一个高度组织化的"中断调度中心"。它将96个外设中断源分成12个组(PIE Group 1 ~ Group 12),每组管理8个中断。然后,每一组"借用"一个CPU的中断线(例如,PIE Group 1 对应 CPU的INT1,Group 2 对应 INT2,依此类推)。

- 工作流程:

- 当一个外设(例如PWM1)产生中断时,请求信号首先发送到PIE模块。

- PIE模块识别出该中断属于哪个组(例如PWM1属于Group 2),并检查该组和对应的CPU中断线是否已使能。

- 如果条件满足,PIE模块会通过对应的CPU中断线(例如INT2)向CPU发出请求。

- CPU响应INT2后,会询问PIE模块:"是Group 2中的哪一个中断?"

- PIE模块会给出一个具体的向量号,CPU根据这个向量号,跳转到预先在PIE 向量表中设置好的、唯一对应的中断服务函数地址去执行。

通过这种分级管理机制,PIE成功地实现了将海量外设中断源复用、映射到有限的CPU中断线上,使F28335能够高效地管理复杂的中断系统。

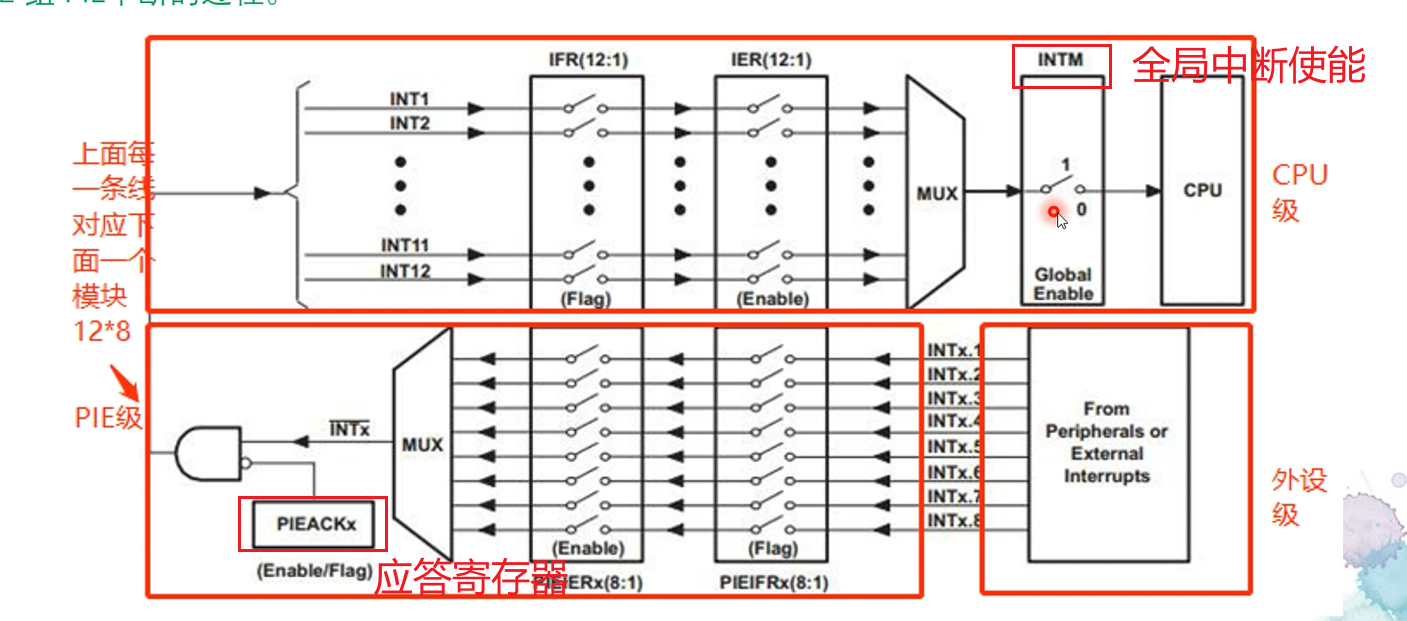

F28335 采用**外设级中断、**PIE 级中断、 CPU 级中断 的三级中断机制,以高效管理大量外设中断:

- CPU 级中断:是最核心的中断响应层,CPU 仅能响应自身中断线上传递来的中断请求;但因 F28335 中断源极多、CPU 中断线数量有限,需通过 "中断线复用" 扩展能力。

- PIE 级中断:作为中间层,负责管理中断线的复用,解决 "中断源数量远多于 CPU 中断线数量" 的矛盾。

- 外设级中断:是中断的起始层,外设需先获得自身的中断允许,才能进一步向更高层传递中断请求。

中断响应流程 :外设要触发中断并被 CPU 响应,需依次经过「外设级中断允许」→「PIE 级中断允许」→「CPU 级中断允许」,三级允许都满足后,CPU 才会响应。

外设级中断的核心机制可总结为以下几点:

- 标志与使能联动:外设产生中断事件时,自身对应中断标志位(IF)会置 1;只有当该中断的使能位(IE)也被置 1 时,外设才会向 PIE 控制器发送中断请求。

- 标志位的保持性:若中断使能位(IE)为 0,即便中断标志位(IF)已置位,外设也不会向 PIE 发请求,但 IF 会持续保持置位状态,直到程序手动清除;若后续 IE 被置 1,外设会立即向 PIE 发起中断请求。

- 标志位的清除:进入中断服务程序后,部分硬件外设会自动复位中断标志寄存器,多数外设则需要通过程序手动复位中断标志寄存器。

PIE 级中断是为解决 "CPU 中断线数量不足,无法直接处理所有外设级中断" 而设计的中间层管理机制,核心要点如下:

- 分组复用逻辑 :F28335 的 PIE 模块将众多外设中断划分为12 个组 ,每组对应 CPU 的 1 个可屏蔽中断线;每组内部又包含8 个外设级中断,通过 "8 选 1 多路选择器" 实现组内中断的复用与转发管理。

- 中断规模适配:实际有效外设中断共 58 个(其余为保留),借助 PIE 的分组复用,可适配 CPU 仅 12 个可屏蔽中断线的硬件限制,让大量外设中断能被有序处理。

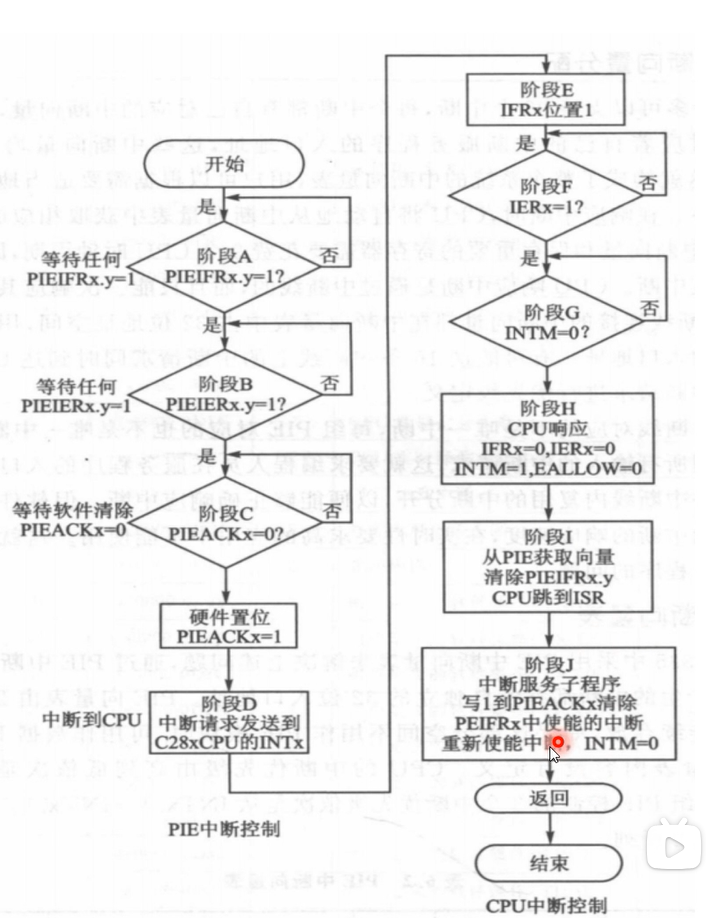

CPU 级中断作为中断响应的核心执行层,通过 ** 中断标志寄存器(IFR)、中断使能寄存器(IER)、全局中断屏蔽位(INTM)** 协同管理,流程分为四步:

- 请求接收与标志锁存

当外设中断经 PIE(外设中断扩展模块)传递到 CPU 时,IFR中对应中断的标志位(如外部中断 XINT1 的标志位)会置 1,并被锁存在寄存器中。

- 响应条件判断

CPU 不会立即响应中断,需同时满足两个条件:

IER 使能:IER中对应中断的使能位已置 1(允许该中断被 CPU 响应);

全局中断允许:全局中断屏蔽位INTM为 0(表示 CPU 允许响应全局可屏蔽中断)。

- 上下文保护与中断屏蔽

为确保中断返回后能恢复原程序执行,CPU 会执行一系列准备操作:

清除IFR中已响应的对应中断标志位;

清除EALLOW(权限控制位,限制关键寄存器访问);

置位INTM(暂时屏蔽其他可屏蔽中断,避免普通中断嵌套干扰;需注意:**RESET(复位信号)、NMI(不可屏蔽中断)** 优先级最高,即使 INTM 置位,仍会强制触发 CPU 响应);

存储返回地址,并将当前运行的关键数据(如寄存器值)压入堆栈。

- 执行中断服务子程序

准备完成后,CPU 从PIE 向量表中取出对应的中断服务子程序(ISR)向量,转而执行中断服务程序。

一、DSP28335 内部定时器中断--配置详解

等待补充

二、DSP28335 外部中断配置详解

概述

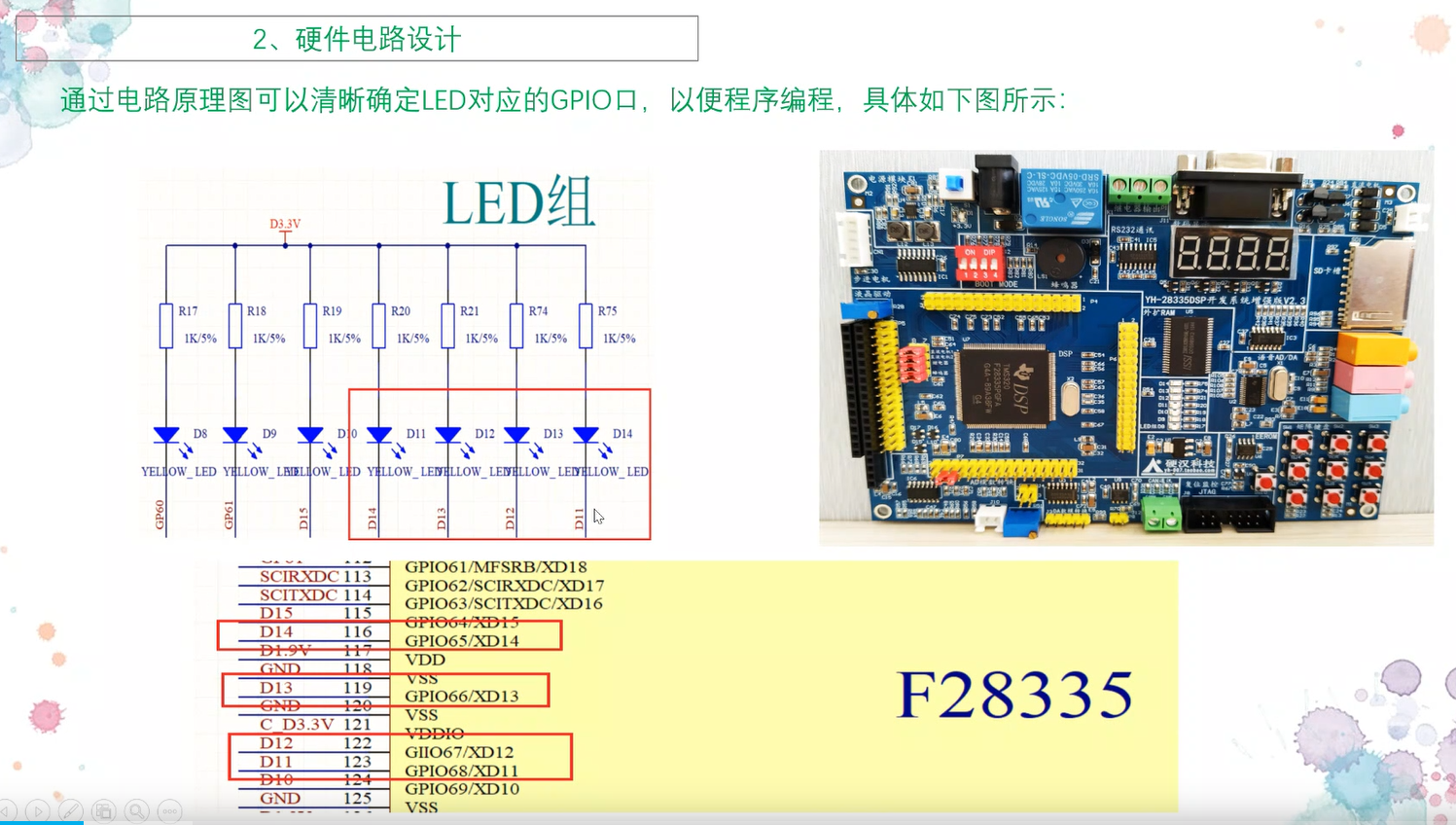

本案例基于DSP28335微控制器,实现了两个外部中断功能,分别对应GPIO12和GPIO13两个按键输入,控制LED13和LED12的翻转。下面将详细解析外部中断的初始化配置过程。

硬件连接原理

按键电路

- 按键采用上拉电阻设计,IO口外部连接3.3V上拉电阻

- 按键未按下时:IO口保持高电平(3.3V)

- 按键按下时:IO口被拉低到地(GND)

- 中断触发方式:下降沿触发(从高电平变为低电平时触发)

LED 电路

- LED采用共阳极接法,阳极连接3.3V电源

- 阴极通过限流电阻连接到DSP的IO口

- 当IO口输出低电平时,LED导通发光

- 当IO口输出高电平时,LED熄灭

外部中断 1(XINT1) 初始化详解

1. 时钟使能

c

EALLOW;

SysCtrlRegs.PCLKCR3.bit.GPIOINENCLK = 1; // 使能 GPIO 输入时钟

EDIS;

作用 :开启GPIO输入模块的时钟,这是GPIO中断功能正常工作的前提。

2. GPIO 端口配置

c

EALLOW;

// KEY1 端口配置 (GPIO12)

GpioCtrlRegs.GPAMUX1.bit.GPIO12 = 0; // 配置为 GPIO 功能

GpioCtrlRegs.GPADIR.bit.GPIO12 = 0; // 配置为输入方向

GpioCtrlRegs.GPAPUD.bit.GPIO12 = 0; // 使能上拉电阻

GpioCtrlRegs.GPAQSEL1.bit.GPIO12 = 0; // 与系统时钟同步,无采样周期

// LED 控制端口配置 (GPIO48)

GpioCtrlRegs.GPBMUX2.bit.GPIO48 = 0; // 配置为 GPIO 功能

GpioCtrlRegs.GPBDIR.bit.GPIO48 = 1; // 配置为输出方向

GpioCtrlRegs.GPBPUD.bit.GPIO48 = 0; // 使能上拉电阻

GpioDataRegs.GPBCLEAR.bit.GPIO48 = 1; // 初始化为高电平, LED 熄灭

EDIS;

3. 外部中断引脚选择

c

EALLOW;

GpioIntRegs.GPIOXINT1SEL.bit.GPIOSEL = 12; // 将 XINT1 映射到 GPIO12

EDIS;

作用 :DSP28335的XINT1可以映射到多个GPIO引脚,这里选择GPIO12作为外部中断1的输入源。

4. 中断向量表配置

c

EALLOW;

PieVectTable.XINT1 = &EXINT1_IRQn; // 注册中断服务函数

EDIS;

作用 :将中断服务函数EXINT1_IRQn的地址写入PIE中断向量表,当中断发生时CPU会自动跳转到该函数执行。

5. PIE 级中断使能

c

PieCtrlRegs.PIEIER1.bit.INTx4 = 1; // 使能 PIE 组 1 的第 4 个中断 (XINT1)

作用 :在PIE(外设中断扩展)模块中使能XINT1中断。

6. 外部中断控制器配置

c

XIntruptRegs.XINT1CR.bit.POLARITY = 0; // 下降沿触发

XIntruptRegs.XINT1CR.bit.ENABLE = 1; // 使能 XINT1 中断

参数说明 :

- POLARITY = 0:下降沿触发

- POLARITY = 1:上升沿触发

- POLARITY = 2:双边沿触发

7. CPU 级中断使能

c

IER |= M_INT1; // 使能 CPU 中断 1 (对应 PIE 组 1 )

EINT; // 开启全局中断

ERTM; // 开启实时调试中断

外部中断 2(XINT2) 初始化详解

XINT2的初始化流程与XINT1类似,主要区别在于输入限定器的配置:

输入限定器特殊配置

c

GpioCtrlRegs.GPAQSEL1.bit.GPIO13 = 2; // 6 个采样窗口限定具体工作流程。

// GPAQSEL1 寄存器位域定义

GPAQSEL1.bit.GPIO13 = 0; // 同步模式,无采样限定

GPAQSEL1.bit.GPIO13 = 1; // 3 采样模式

GPAQSEL1.bit.GPIO13 = 2; // 6 采样模式 ← 案例中使用

GPAQSEL1.bit.GPIO13 = 3; // 保留

GpioCtrlRegs.GPACTRL.bit.QUALPRD1 = 0xFF; // 采样周期为 512*SYSCLKOUT

正确公式:采样周期 = (QUALPRD + 1) × 2 × TSYSCLKOUT

案例计算:0xFF → (255+1)×2 = 512个SYSCLKOUT周期

输入限定器作用 :

- 防止按键抖动导致误触发

- 采用6个采样窗口,只有当连续6个采样点都满足触发条件时才认为有效中断

- 采样周期配置为较大值,增强抗干扰能力

其他配置差异

c

GpioIntRegs.GPIOXINT2SEL.bit.GPIOSEL = 13; // XINT2 映射到 GPIO13

PieCtrlRegs.PIEIER1.bit.INTx5 = 1; // 使能 PIE 组 1 的第 5 个中断 (XINT2)

中断服务函数详解

XINT1 中断服务函数

c

interrupt void EXINT1_IRQn(void)

{

Uint32 i;

for(i=0;i<10000;i++); // 延时消抖

while(!KEY_H1); // 等待按键释放

LED13_TOGGLE; // 翻转 LED13 状态

PieCtrlRegs.PIEACK.bit.ACK1 = 1; // 清除 PIE 中断标志

}

中断处理流程

- 延时消抖:通过循环延时消除按键机械抖动

- 等待释放:确保在按键释放后才执行后续操作

- 执行功能:翻转LED状态

- 清除标志:向PIEACK寄存器写1,清除中断标志,允许新的中断

关键技术要点

1. 中断优先级管理

- PIE模块将96个外设中断分为12组,每组8个中断

- XINT1属于PIE组1的INT4,XINT2属于PIE组1的INT5

- 同一组内的中断有固定的硬件优先级

2. 中断响应流程

- 外设产生中断信号

- PIE模块接收并判断中断源

- CPU响应中断,跳转到对应的中断服务函数

- 执行中断处理代码

- 清除中断标志,返回主程序

3. EALLOW/EDIS 保护机制

- 某些关键寄存器受EALLOW保护,修改前需要使用EALLOW指令

- 修改完成后使用EDIS指令恢复保护状态

- 防止意外修改重要系统配置

总结

本案例完整展示了DSP28335外部中断的配置流程,涵盖了从GPIO配置、中断映射、PIE配置到中断服务函数编写的全过程。通过按键触发外部中断控制LED状态,是学习DSP中断系统的经典案例。特别需要注意的是中断标志的清除和按键消抖处理,这些是确保中断稳定可靠工作的关键。