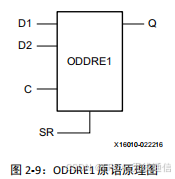

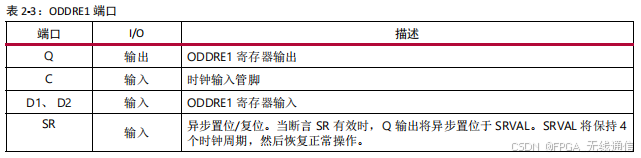

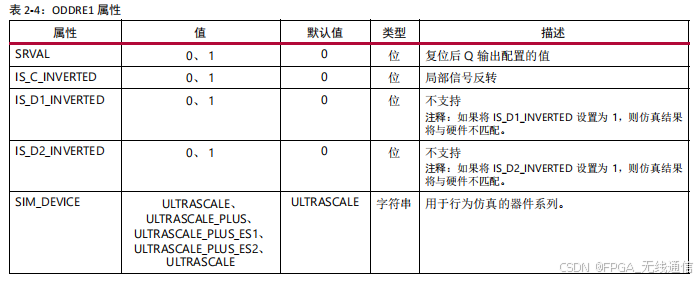

IDDRE1、ODDRE1

IDDR、ODDR为7系列;

两者功能相同;

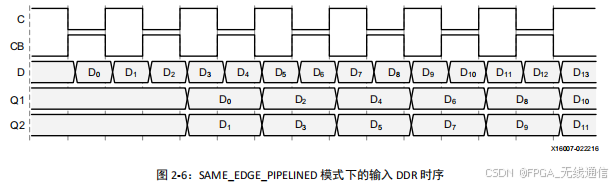

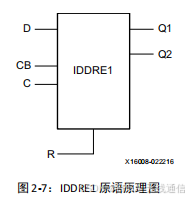

FPGA为单沿处理数据,PHY为双沿处理数据;

PHY数据进入FPGA之后,需要将双沿数据转为单沿数据;

IDDR:双沿数据转单沿数据,用于PHY传输数据给FPGA;

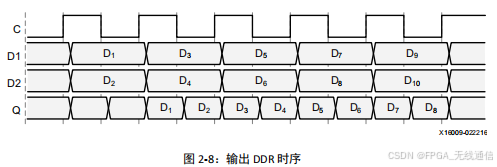

ODDR:单沿数据转双沿数据,用于FPGA传输数据给PHY;

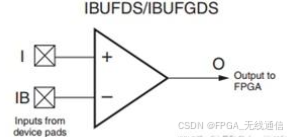

IBUFDS,OBUFDS

LVDS:低压差分信号;

LVDS使用一对相位相反的差分信号传输数据,通过两者电压差判断逻辑值,在发送端单端转差分,在接收端差分转单端;

差分信号用于信号传输,在FPGA 内部数据处理时,需要将外部给入的差分信号转为单端信号使用,因此需要使用 IBUFDS原语实现;

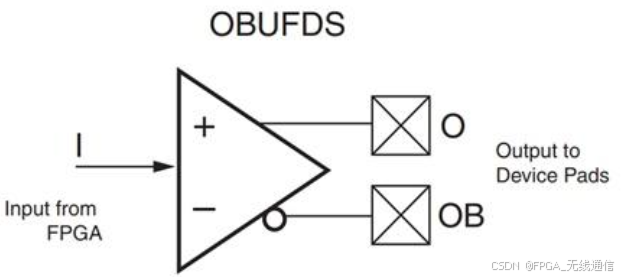

将FPGA 内部的单端信号转为差分信号输出,使用OBUFDS 原语实现;

I 和 IB为 FPGA的外部信号,I为差分信号正端,IB为差分信号的负端;

O 为输出的单端信号;

I = 1, IB = 0, O = 1;

I = 0, IB = 1, O = 0;

I=IB,原语不工作,保持之前值不变

I = 0, O = 0, OB = 1;

I = 1, O = 1, OB = 0;

IOBUFDS

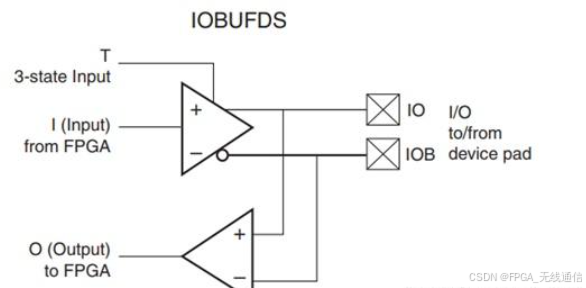

IOBUFDS:三态双向差分信号原语

针对inout管脚,例如 DDR接口的 DQS数据选通信号

IOBUFDS为差分输入/输出缓存原语。 T 管脚上的逻辑高电平表示禁用输出缓存。

端口IO、IOB:双向端口,连接到焊盘上的双向差分信号;

端口I:原语的输入端口,接收FPGA内部数据变换后从IO和IOB输出;

端口O:原语的输出端口,IO和IOB接收数据转换后从O端口输出到FPGA内部;

端口T:原语的输入端口,控制原语的功能模式;

功能模式说明:

输入模式(T=1):

IO和IOB由外部设备驱动,作为差分输入信号。

内部逻辑将IO和IOB的差分值(IO - IOB)转换为单端信号输出至O。

例如,若IO=1且IOB=0,则O=1;若IO=0且IOB=1,则O=0,此时功能与IBUFDS一致。

若外部差分信号未驱动(高阻态),O可能保持前一次有效值或进入不定态(X),需通过外部约束或硬件设计避免此情况。

此时T=1,输出缓存被禁用,I到IO、IOB的路径关闭,原语的I端口输入任何值(无论0/1或是悬空)都不会对IO、IOB的电压状态造成任何影响;

输出模式(T=0):

I的单端信号被转换为差分信号,驱动到IO(与I同相)和IOB(与I反相)。

例如,若I=1,则IO=1且IOB=0;若I=0,则IO=0且IOB=1,此时功能与OBUFDS一致。

此时T=1,输出缓存启用,可以看到在原语的图中,IO、IOB到O的路径没有受到T端口开关的影响,此时O的输出来自IO、IOB,而IO、IOB的值此时来自于I,所以O值与I值相同。

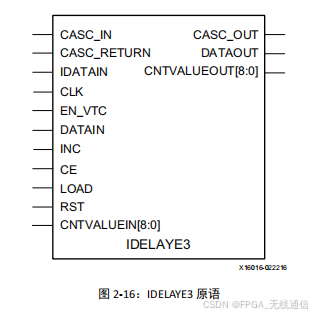

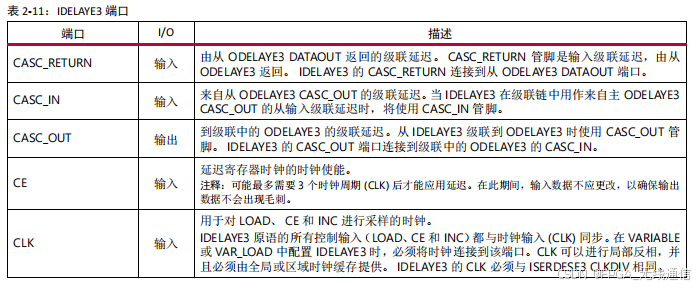

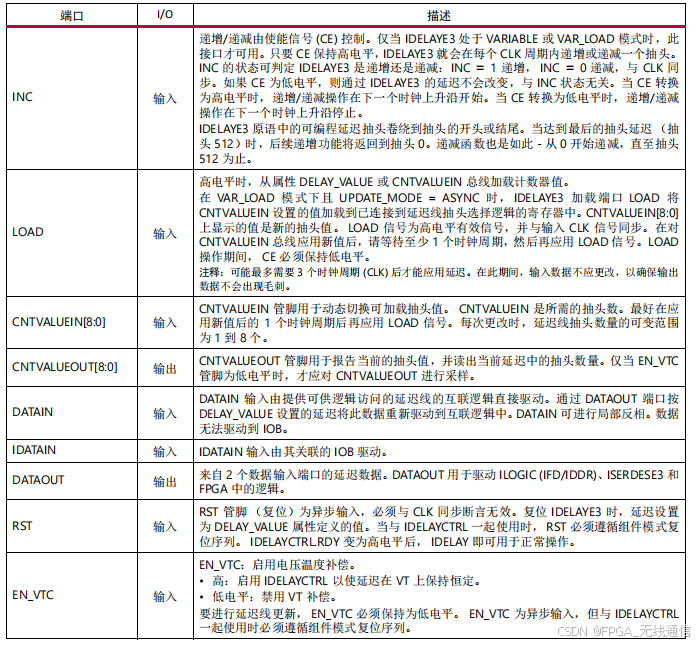

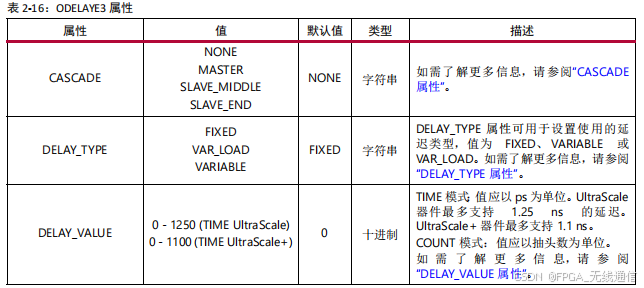

IDELAYE3、ODELAYE3、IDELAYCTRL

LVDS输入信号线在经过PCB输入到FPGA 中后,本来该严格对齐的信号线会出现时延,所以需要在 FPGA内部对齐进行延时对齐后再进行解析;

Xilinx 7系器件中用于输入信号延时的组件为IDELAYE2可编程原语,通过可以编程的32抽

头延迟线、环绕式延迟实现信号延迟。

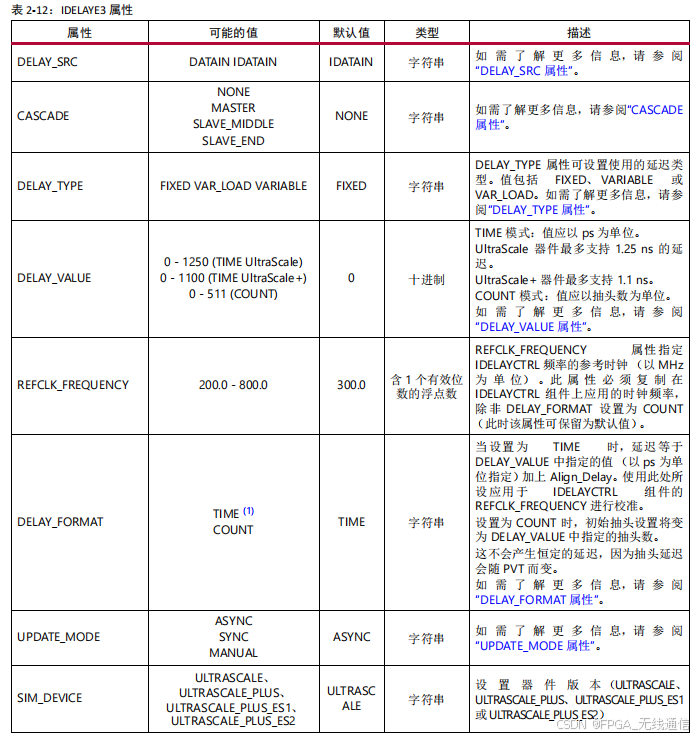

U+系列为IDELAYE3;

可以使用该原语延迟除时钟以外的任何输入信号,然后将其直接转发到器件逻辑,

或者使用输入/输出互联 (IOI) 内部的单数据速率 (SDR) 时钟或双倍数据速率 (DDR) 时钟将其寄存到简单的触发器、IDDDR 或 ISERDESE3 中。不 应使用 IDELAYE3 来延迟时钟,因为 IDELAY 无法直接布线到全局时钟缓存。如必须延迟时钟,请使用 MMCM 或 PLL 生成时钟,并使用精细相移功能来延迟时钟。

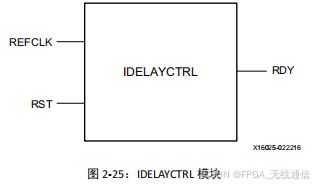

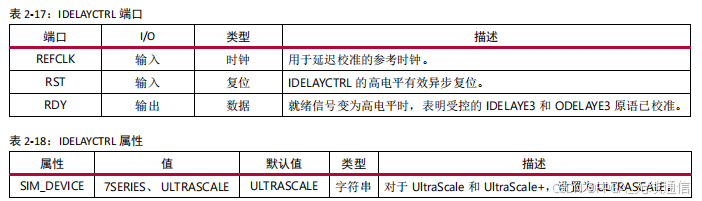

在使用IDELAYE2 或者 IDELAYE3 的同时,还需要例化 IDELAYCTRL原语, IDELAYCTRL 原语为IDELAYE2 或者 IDELAYE3 提供时钟参考,同时持续校准各个延迟抽头,减少外部环境和器件对于延迟精度的影响;

如果使用了IDELAYE3或ODELAYE3的TIME模式,就必须例化IDELAYCTRL组件,如果使用

COUNT模式,就不使用IDELAYCTRL组件;

REFCLK:参考时钟,使用时参考时钟与其联合使用的IDELAYE3和ODELAYE3设置相同值;

原语可用于组合输入路径、寄存器输入路径、FPGA逻辑直接访问;可以对单个输入引脚

进行信号延迟。原语的抽头延迟分辨率也就是延时精度由 IDELAYCTRL原语控制。

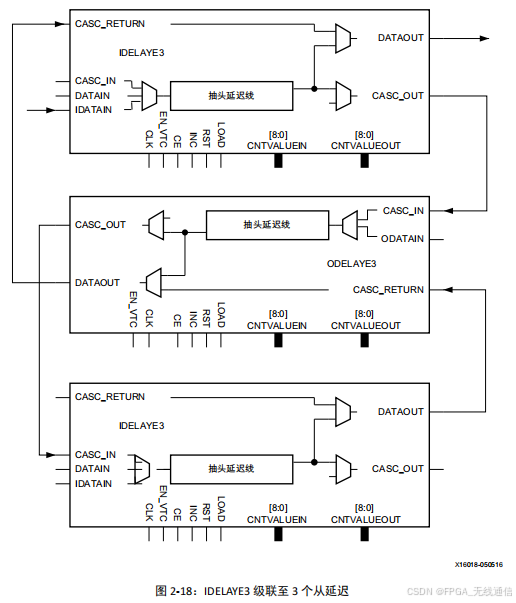

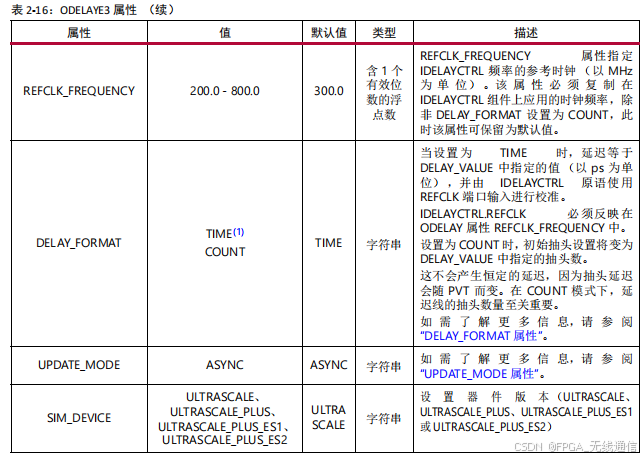

上图中可以看到,IDELAYE3的级联操作需要ODELAYE3一起穿插使用,第一级CASCADE参数设置为MASTER,中间级设置为SLAVE_MIDDLE,最后一级设置为SLAVE_END,级联组件之间的布线是专用高速布线,IDELAYE3 或 ODELAYE3 级联的固定内部插入延迟总量是初始插入延迟与级联插入延迟的总和。此延迟按 IDELAYE3 和 ODELAYE3 级联次数而成倍增加。

在TIME模式下级联时,同一site下两者延迟要相同,如把IDELAYE3延时0.75ns,级联的ODELAYE3延时0.75ns,那么就延时了1.5ns,在FIXED模式下DELAY_VALUE设置两者相同,VAR_LOAD模式下两者CNTVALUEIN输入相同值;

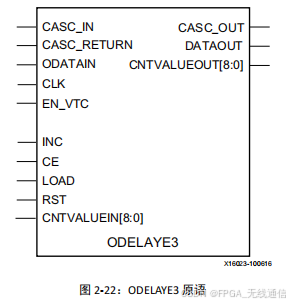

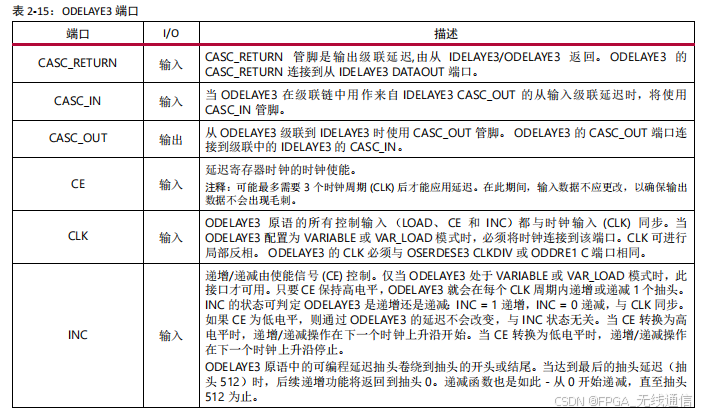

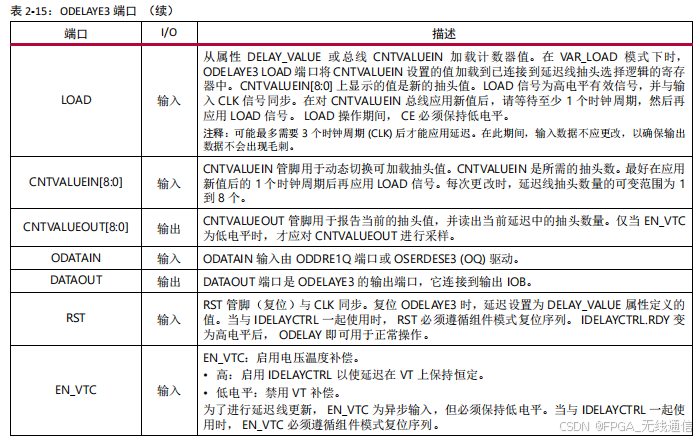

Ultrascale 系的输出原语ODELAYE3可以对任何输出信号进行延迟,这些输出信号可以直接

从器件逻辑进行转发,或是使用单沿SDR或双沿DDR时钟寄存在触发器或是OSERDES中,可以延迟的范围较广;

ODELAYE3同样有两种模式:

COUNT模式:不使用IDELAYCTRL组件,延时线不校准,没有电压温度补偿,延迟线只用

抽头进行计数,不使用ps进行计数,参数DELAY_VALUE用抽头数量表示,0-511;

TIME模式:使用IDELAYCTRL组件,延时线按请求的时间进行校准,电压温度补偿确保延

时线的延迟值不随时间变化,参数DELAY_VALUE用ps表示;

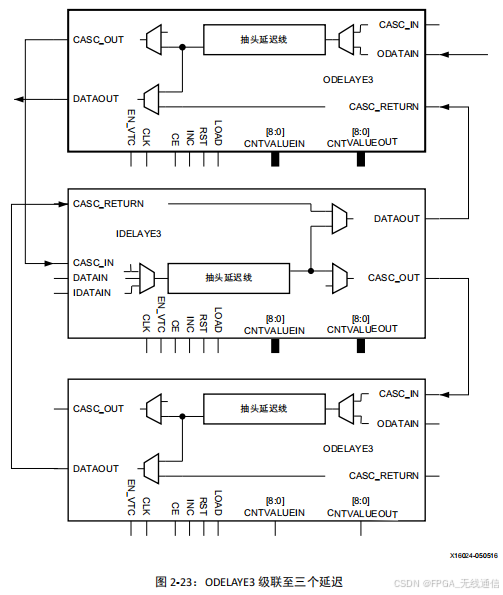

ISERDESE3、OSERDESE3

ISERDESE3 元素可用于为从先前的 FPGA 系列移植的设计或不需要原生模式原语的设计执行输入解串化。 UltraScale 器 件中的 ISERDESE3 是具有特定时控和逻辑功能的串并转换器,便于实现高速源同步应用。 ISERDESE3 可避免在器件逻 辑中设计解串器时所遇到的额外时序复杂性。

RX_BITSLICE原理图:

ISERDESE3 与先前使用的工具之间存在一些差异。 ISERDESE3 没有:

• BITSLIP 输入,它可执行与 CLKDIV 同步的比特滑动操作。

• 可选的 CE 输入,它可用作由 CLKDIV 进行时控的 2:1 串并转换器。

• OFB 输入,它是 OSERDES 串行输出和该输入之间的直接连接。

• SHIFTIN 和 SHIFTOUT 管脚,这些管脚通过使用直接连接来级联 2 个 ISERDES,从而允许将解串功能扩展到 14 位。

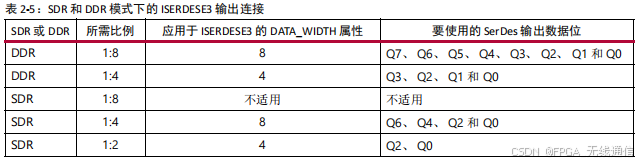

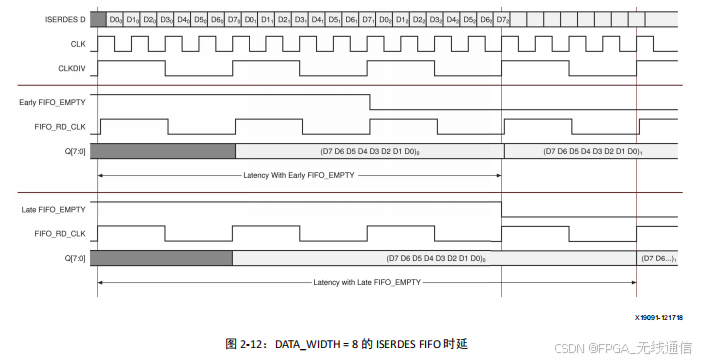

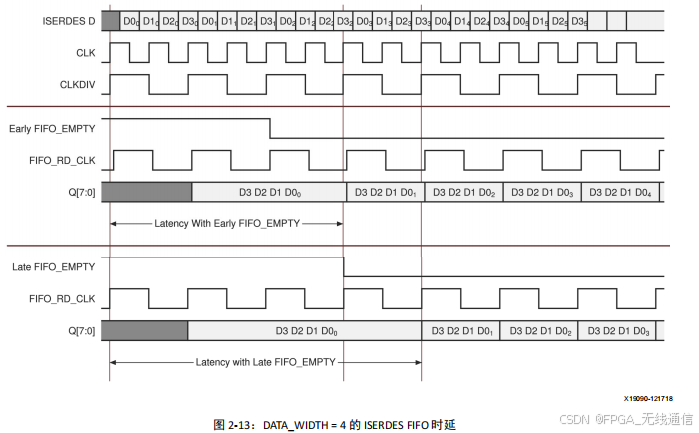

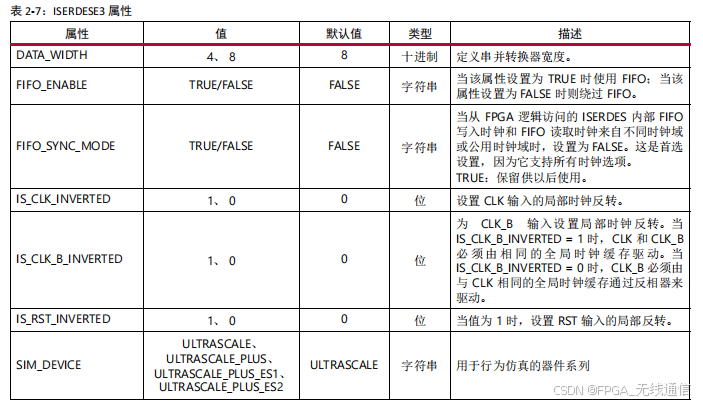

ISERDESE3 可在 SDR 数据捕获中将传入信号按 2 或 4 位进行解串,而在 DDR 数据捕获模式中则可以按 4 或 8 位进行解 串。当用于 SDR 数据捕获时,每隔一个数据输出管脚即为有效输出。例如,当使用 SDR 时钟作为 1:4 解串器时,数据 宽度应设置为 8,接收到的数据取自 Q0、 Q2、 Q4 和 Q6。

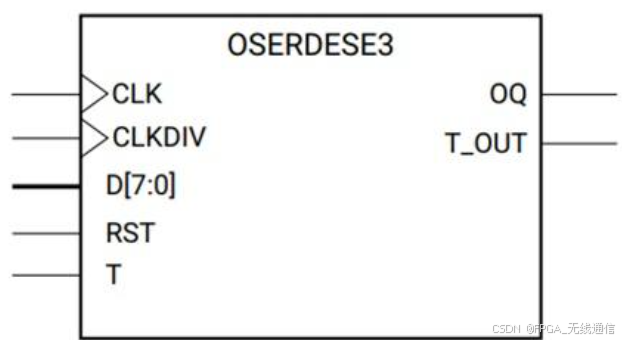

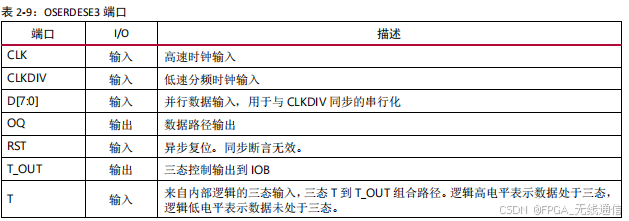

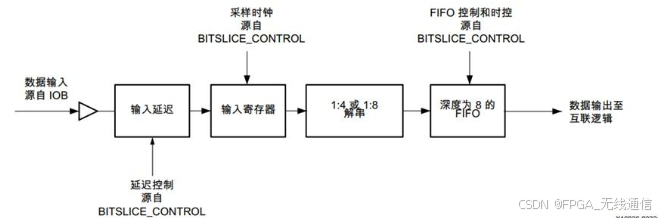

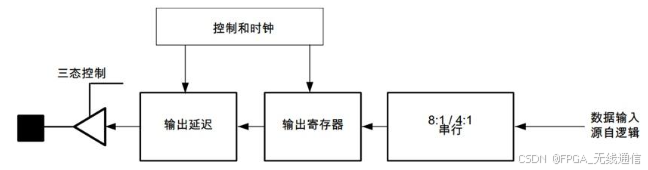

OSERDESE3 原语可用于为从先前的 FPGA 系列进行移植的设计或不需要原生模式原语的设计执行输出串行化。

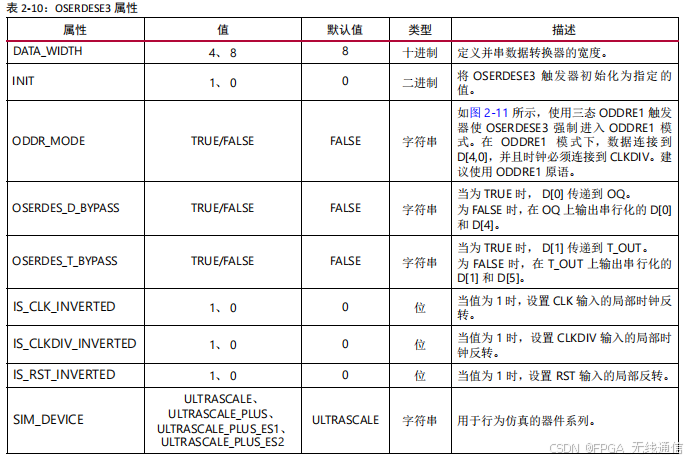

UltraScale 器件中的 OSERDESE3 是一个 4 或 8 位并串转换器,具有特定的时控功能,便于实现源同步应用和其它应用。如果需要其它串并转换因子,请使用 ODDRE1 原语或在内部逻辑中实现变速箱。

TX_BITSLICE原理图:

OSERDESE3 与先前使用的工具之间存在一些差异。以下功能在 OSERDESE3 中不可用:

• OCE 输入使能管脚,该管脚用于 OSERDES 的串行输出。

• SHIFTIN 和 SHIFTOUT 管脚,这些管脚可以使用局部专用连接来扩展 OSERDES 的串行化功能。

• OFB 输出,用于提供 OSERDES 输出与 ISERDES 输入之间的直接连接,而无需使用输入和/或输出缓存 (IOB) 和管

脚。

• 并联三态和串联 TBYTE 功能。

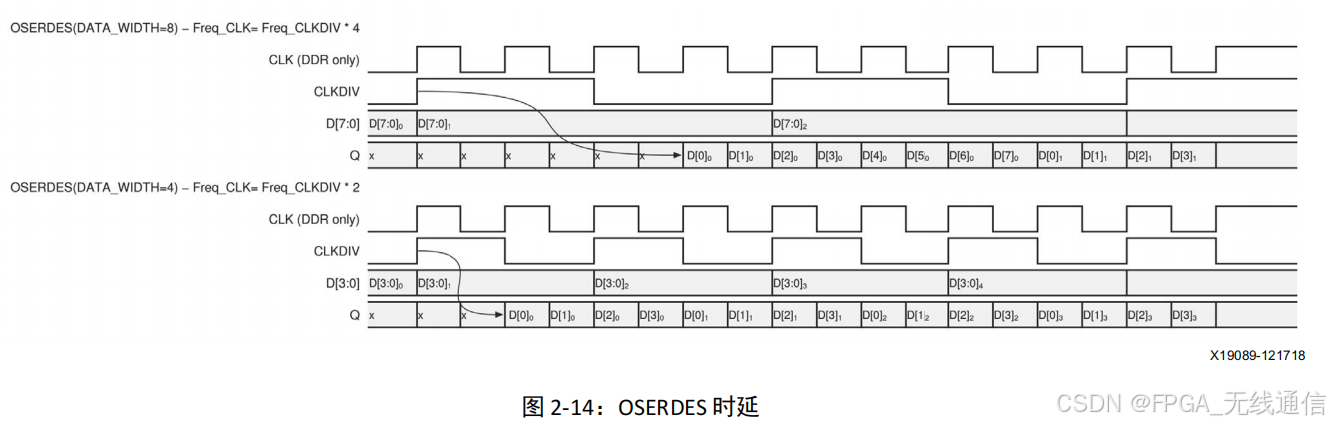

穿过 OSERDES 的时延取决于 DATA_WIDTH 设置,

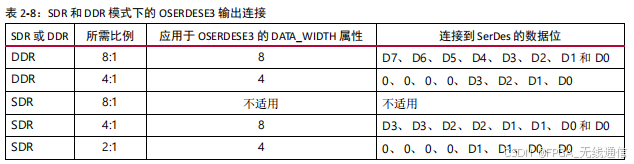

OSERDESE3 可以在 SDR 模式下按 2 或 4 位对传出信号进行串行化,或在 DDR 模式下按 4 或 8 位进行串行化。搭配 SDR 时控一起使用时, DATA_WIDTH 属性应设置为所需宽度的两倍,并且要传输的数据应同时应用于 2 个管脚。