Performance Mode

高性能模式将使用 AXI4 代替 AXI4-Lite 接⼝,并且在内核的发送和接收 FIFO 地址处可以使用突发功能。

transaction width

设置传输事务的数据宽度:

如果设置为8,即每次数据传输宽度为8-bit,一次数据传输需要8个SCK时钟

如果设置为16,即每次数据传输宽度为16-bit,一次数据传输需要16个SCK时钟

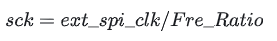

Frequency Ratio

频率比是由两个数的乘积。输出的SPI时钟(sck)满足:

Enable Master Mode

这个选项决定SPI设备的主从模式,也可以在配置寄存器60h中修改。

Enable STARTUPEn Primitive

STARTUPEn 原语有⼀个专⽤时钟引脚,可⽤于为从存储器提供 SPI 时钟。这个选项主要用来设置FPGA的默认程序flash的时钟,可用于远程更新配置。