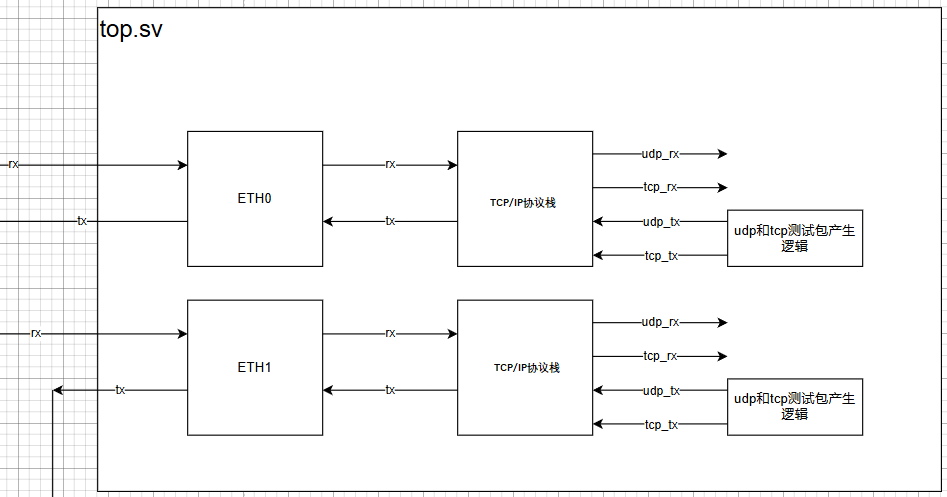

项目简要架构

当前项目主要利用10G万兆以太网与上位机进行数据传输。TCP传输逻辑是当FPGA与TCP建立连接之后,FPGA板卡将数据发送到上位机上,当前阶段为了测试方便,FPGA内部发送有规则的累加数据到上位机。其简要结构如图所示,例化了2个TCP/IP模块,实现TCP/UDP协议栈,每个TCP/IP协议栈最多支持256个TCP连接,当前实际支持的个数为<4个。根据需求可配置。

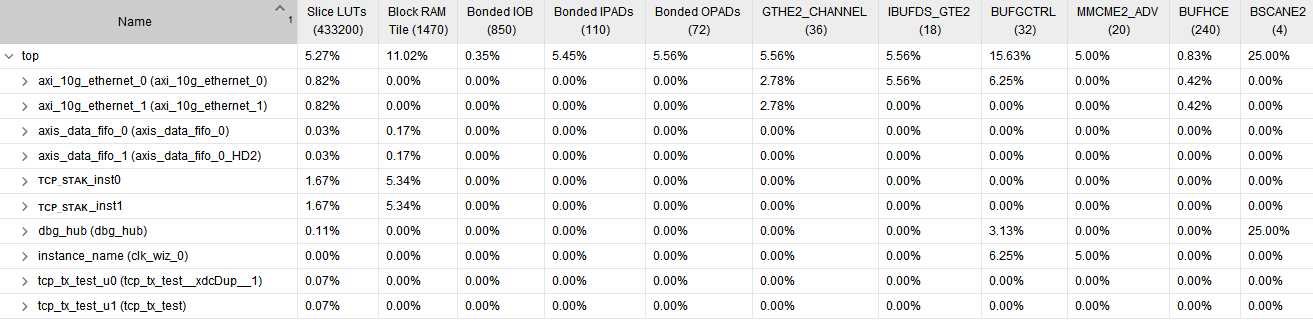

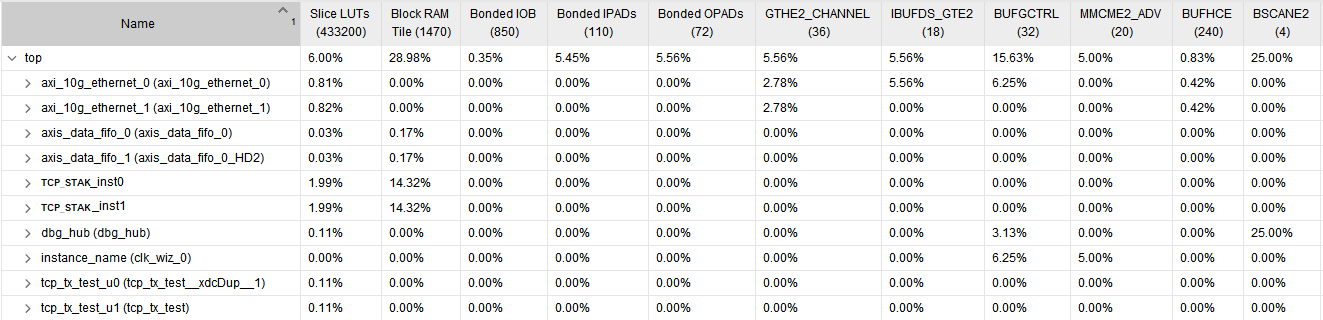

资源性能对比说明 :

|----------------|-------|-----|----------|--------------------|

| 版本 | 缓存大小 | 端口数 | TCP/IP速率 | 690t中BLOCK_RAM使用情况 |

| PCIE404_TCP_01 | 128KB | 1端口 | 3.3Gbps | 162 |

| PCIE404_TCP_02 | 128KB | 2端口 | 6.6Gbps | 226 |

| PCIE404_TCP_04 | 256KB | 1端口 | 8.4Gbps | 298 |

| PCIE404_TCP_05 | 256KB | 2端口 | 9.7Gbps | 426 |

| PCIE404_TCP_07 | 512KB | 1端口 | 9.3Gbps | 570 |

| PCIE404_TCP_08 | 512KB | 2端口 | 9.7Gbps | 826 |

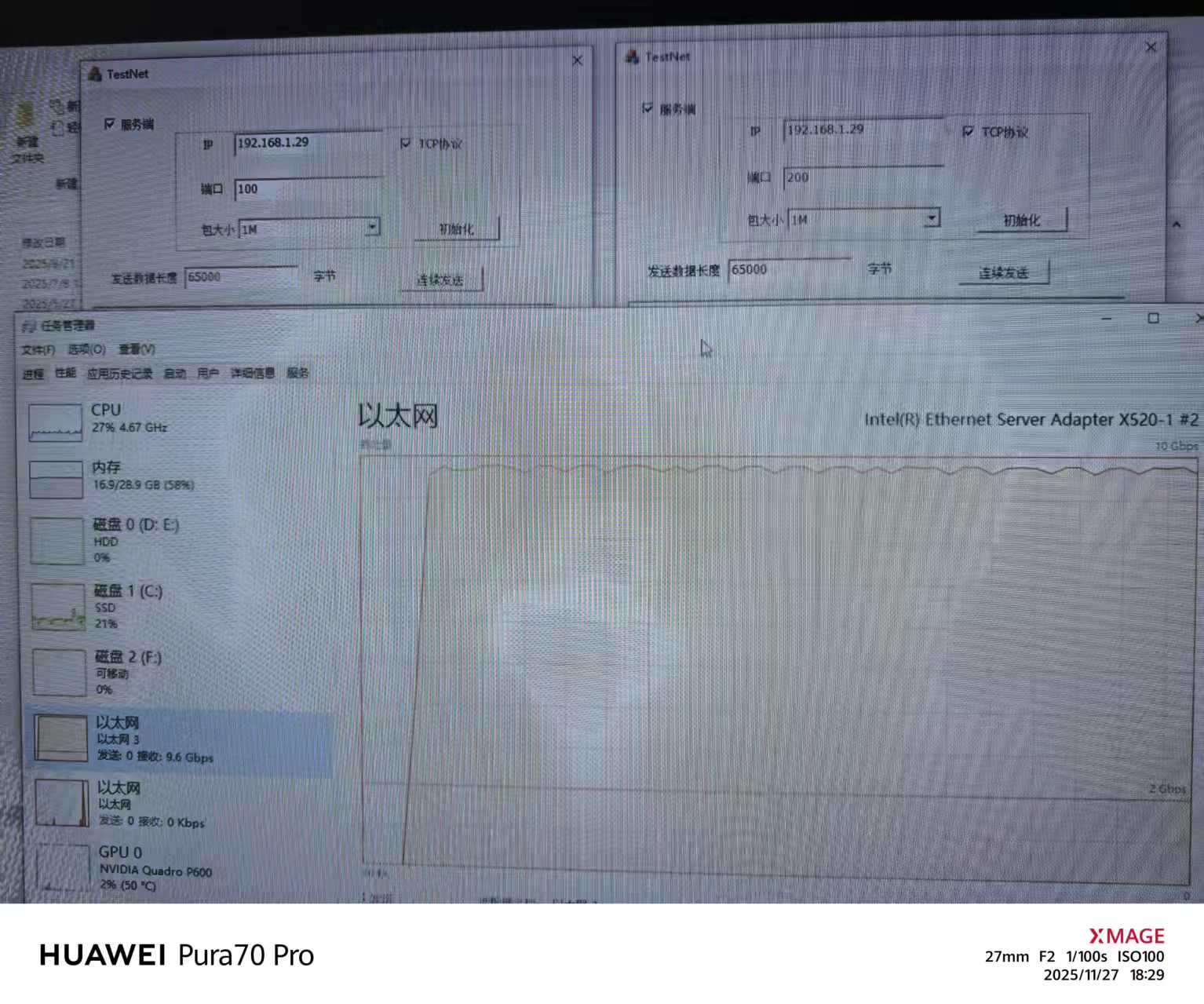

TCP/IP测试速率如下(9.6Gbps/s):

详细资源使用情况

PCIE404_TCP_01

PCIE404_TCP_05

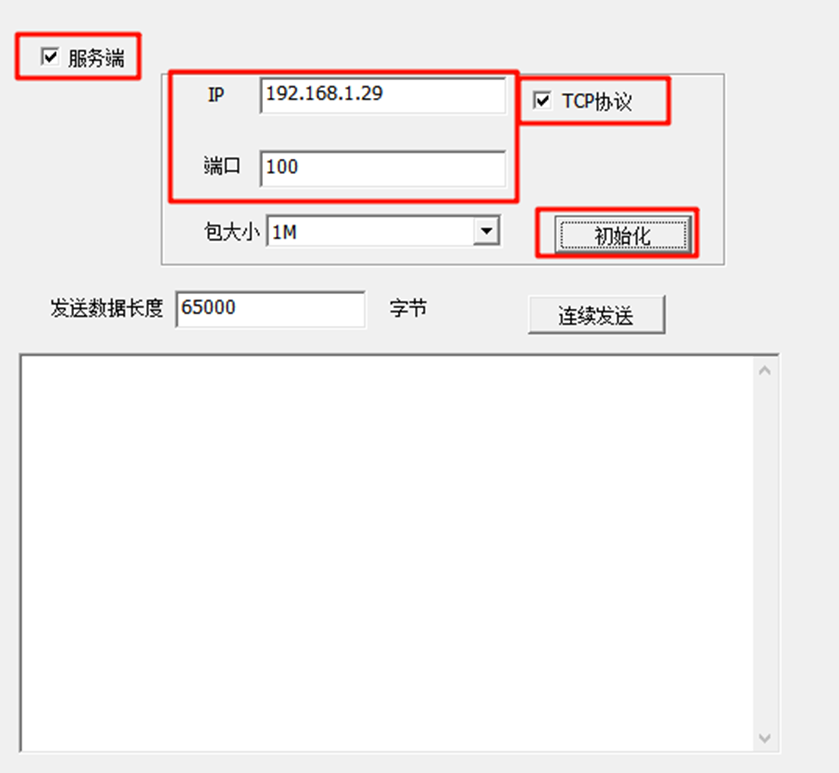

当前TestNet配置如下:

- 需指定当前电脑为服务端

- IP为FPGA板卡的IP地址

- PORT为FPGA板卡设置的PORT

- 需要勾选TCP协议的支持

完成以上配置后,完成初始化后,即可显示TCP报文收包情况。

完成以上配置后,完成初始化后,即可显示TCP报文收包情况。

仿真补充

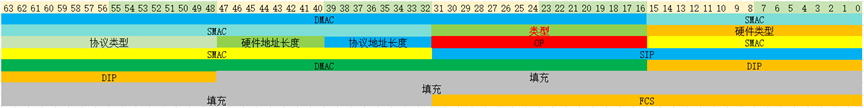

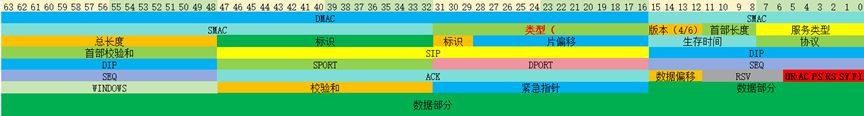

- 接口数据结构

为方便仿真及抓信号是数据分析,补充接口的数据结构

ARP数据结构

TCP数据结构

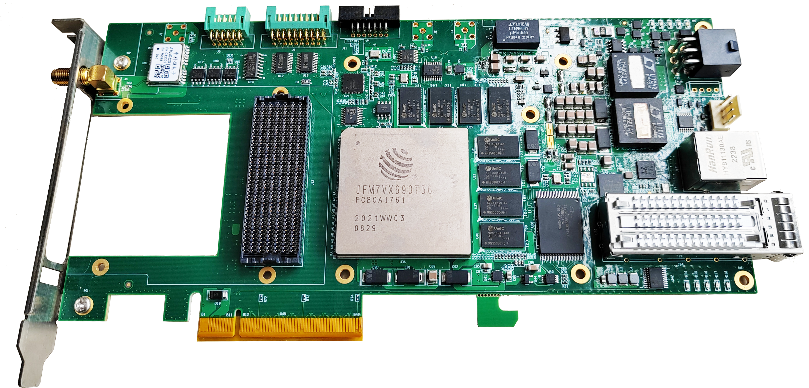

以上在优数科技的UD PCIe-404上测试验证。

UD PCIe-404全国产化信号处理模块为标准PCIe全高的结构,对外支持PCIe3.0×8通信,也可以采用千兆以太网(RJ45连接器)、万兆以太网(或RapidIO、Aurora,QSFP+连接器)接口进行通信,支持多板级联。模块为100%国产化设计(同时也兼容进口器件)。FPGA芯片可选JFM7VX690T、SMQ7VX690T、BQR7VX690T等,两组DDR3的存储容量分别可配置为2~4GByte。板载有1个FMC+(兼容FMC子板)全互联的接口,满足VITA57.1和VITA57.4规范,可以适配大多数ADC/DAC/光纤 FMC或FMC+子卡。全部器件选择工业级和以上质量等级元器件。

UD PCIe-404全国产化信号处理模块为标准PCIe全高的结构,对外支持PCIe3.0×8通信,也可以采用千兆以太网(RJ45连接器)、万兆以太网(或RapidIO、Aurora,QSFP+连接器)接口进行通信,支持多板级联。模块为100%国产化设计(同时也兼容进口器件)。FPGA芯片可选JFM7VX690T、SMQ7VX690T、BQR7VX690T等,两组DDR3的存储容量分别可配置为2~4GByte。板载有1个FMC+(兼容FMC子板)全互联的接口,满足VITA57.1和VITA57.4规范,可以适配大多数ADC/DAC/光纤 FMC或FMC+子卡。全部器件选择工业级和以上质量等级元器件。