这篇文章可以很好辅助江协大的视频,都是根据上课的内容进行补充和补全

51单片机的定时器都是内部的装置,作用就是用于计时系统,可以实现软件计时,或者是程序每隔一段时间完成操作

或者可以代替长时间的Delay,提高cpu的效率(在Delay中我们cpu都会延迟不动,这样就会浪费cpu的效率,我们就可以用定时器来代替Delay)等等,这两个是重要的作用

STC89C52

定时器个数:3 个(T0、T1、T2),T0 和 T1 与传统的 51 单片机兼容,T2 是此型号单片机增加的资源

注意:定时器的资源和单片机的型号是关联在一起的,不同的型号可能会有不同的定时器个数和操作方式,但一般来说,T0 和 T1 的操作方式是所有 51 单片机所共有的

简单来说就是定时器一般都是2到3个定时器

定时器框图

定时器在单片机内部就像一个小闹钟一样,根据时钟的输出信号,每隔 "一秒",(这个一秒只是类似闹钟的说法)计数单元的数值就增加一,当计数单元数值增加到 "设定的闹钟提醒时间" 时,计数单元就会向中断系统发出中断申请,产生 "响铃提醒",使程序跳转到中断服务函数中执行

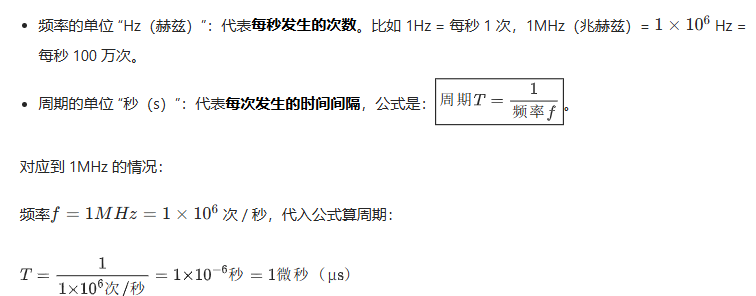

时钟:提供计数单元的时钟脉冲

计数单元:时钟计数

中断系统:产生中断,执行定时任务

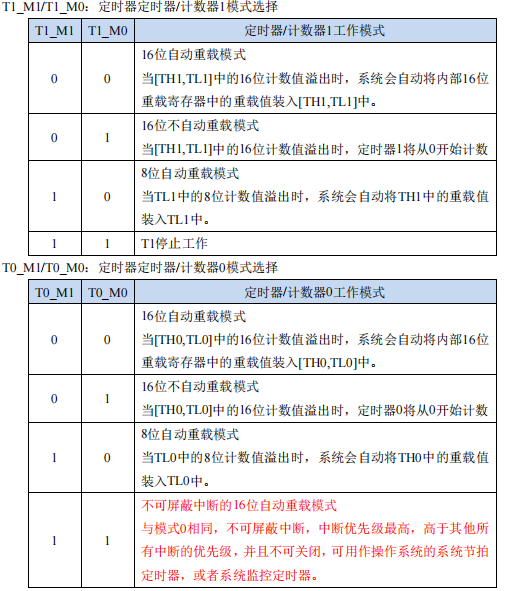

STC89C52 的 T0 和 T1 均有四种工作模式:

- 模式 0:13 位定时器 / 计数器

- 模式 1:16 位定时器 / 计数器(常用)

- 模式 2:8 位自动重装模式

- 模式 3:两个 8 位计数器 (我们只要掌握模式1就可以,剩下就不太常用)

模式 0:13 位定时器 / 计数器(少用)

- 结构:由定时器的高 8 位寄存器({THx})(x 是 0 或 1) + 低 5 位寄存器({TLx})(仅用 TLx 的低 5 位),共同组成 13 位的计数单元。

- 计数范围:(0~ 2^13-1 )= 8191(最多计 8192 个数

- 特点:是早期 51 单片机的兼容模式,初值计算麻烦(因为要拆分 13 位到 THx 和 TLx 的低 5 位)

- 适用场景:现在基本不用,仅用于兼容老式程序(不重要)

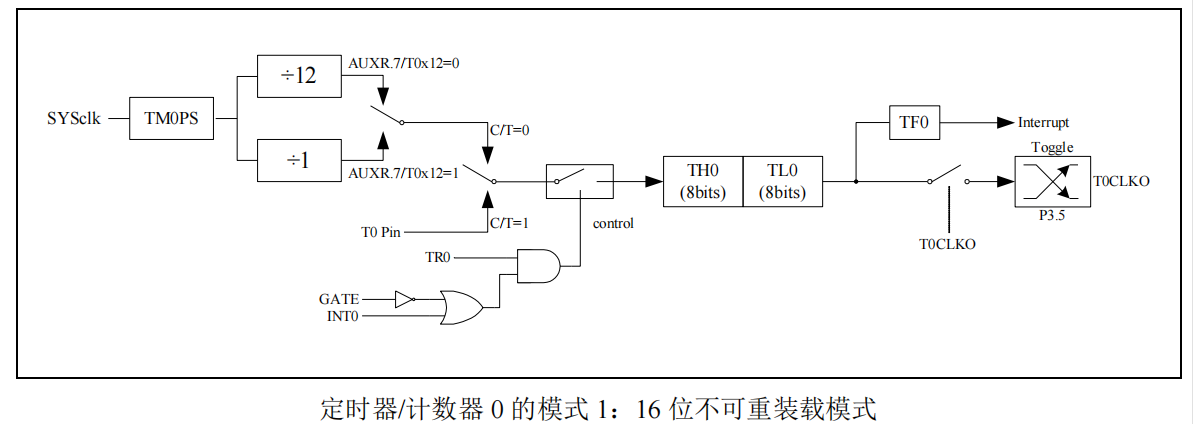

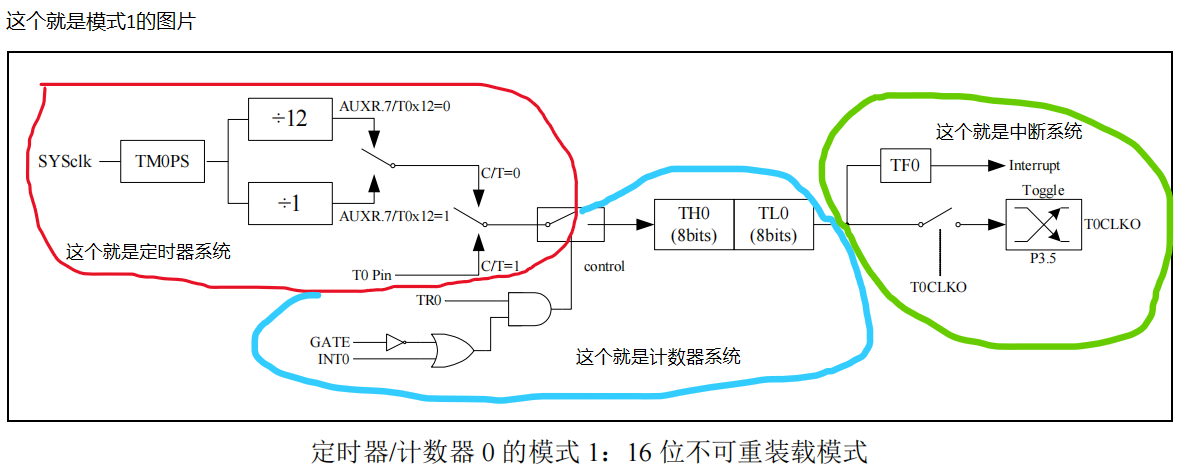

模式 1:16 位定时器 / 计数器(常用)

- 结构:由{THx})(高 8 位) + ({TLx})(低 8 位),组成完整的 16 位计数单元

- 计数范围:(0~ 2^16-1) = 65535(最多计 65536 个数),定时 / 计数的范围比模式 0 大很多

- 特点:需要手动设置初值;溢出后计数单元会清零,若要重复定时,需在中断服务函数里重新给 THx、TLx 赋值。

- 适用场景:最常用的模式,适合需要较长定时 / 计数的场景(比如毫秒级延时、外部信号计数)

模式 2:8 位自动重装模式(还行)

- 结构:{TLx}作为 8 位计数单元,{THx}作为 "初值寄存器"(提前存好要重装的 8 位初值)

- 计数范围:2^8-1 = 256(最多计 256 个数)

- 特点:TLx(低4位) 计数溢出时,THx 里的初值会自动装入 TLx,无需手动重新赋值(避免了手动重装的误差)

- 适用场景:适合需要高频、精确定时的场景,比如串口通信的 "波特率发生器"(需要稳定的时钟频率)

模式 3:两个 8 位计数器(少用)

- 结构:仅 T0 支持模式 3(T1 若设为模式 3 会停止工作)。此时 T0 被拆分为两个独立的 8 位单元:

- TL0:使用原 T0 的资源(定时 / 计数、中断等);

- TH0:占用 T1 的资源(用 T1 的中断、定时器时钟等)。

- 特点:相当于 "额外扩展了一个 8 位定时器",但会占用 T1 的资源

- 适用场景:需要同时运行多个独立定时任务的场景(比如同时需要两个不同频率的延时)

THO:time high的意思,0就代表着定时器0,TLO:time lower 这两个一共16bits,就是65535位

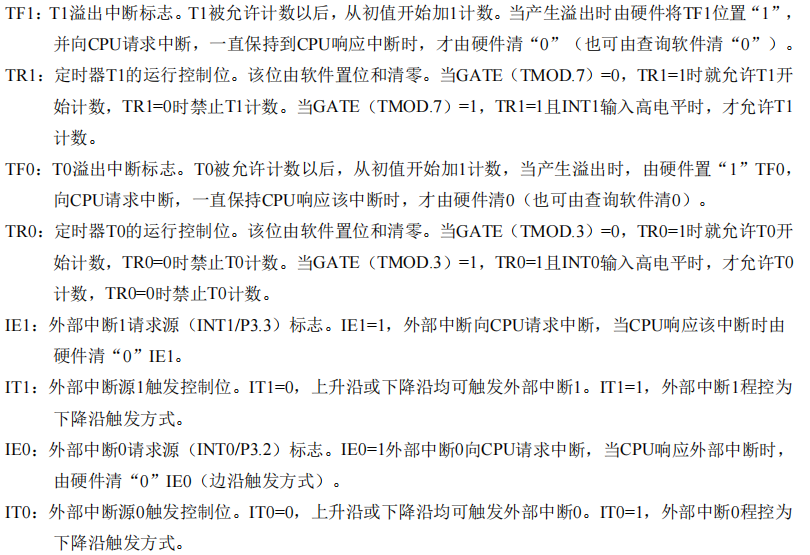

前面的定时器会提供脉冲后,TH0和TL0就会加一,当到最大值的时候就会向TF0申请中断

- SYSclk:系统时钟,即晶振周期(系统时钟),本开发板上的晶振为 12MHz

- T0Pin :外部时钟,这个相当于计数器(因为外部来一个脉冲,就会加一,这个相当于一个计数器)(不常用)

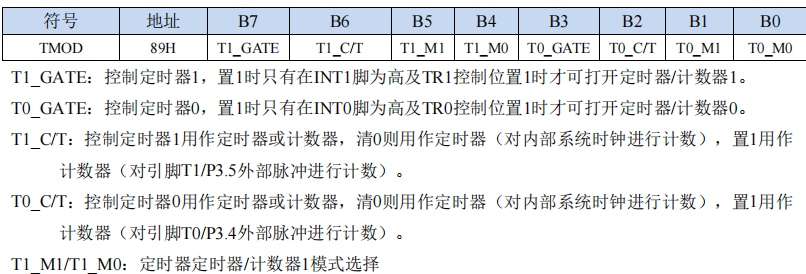

后面还有一个 C/T=0 和 C/T=1 :

当你选择是0(低电平)的时候,就代表的是T,也就是time定时器

那如果选择的是1(高电平)的时候,就代表的是C,也就是counter计数器

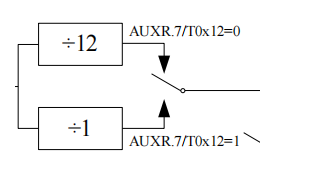

这个图里 TM0PS(定时器 0 的时钟路径)后的两个分支是定时器 0 的 "时钟分频选择" 模块,作用是决定定时器 0 的计数脉冲频率,核心是通过寄存器位切换 "系统时钟的分频系数":

分支 1:÷12

- 对应条件:图中AUXR.7/T0x12=0(STC89C52 的 AUXR 寄存器第 7 位设为 0)

- 功能:这是传统 51 单片机的兼容分频方式------ 系统时钟(SYSclk)先除以 12,再作为定时器 0 的计数脉冲

比如开发板晶振是 12MHz,分频后计数脉冲频率为 12MHz ÷ 12 = 1MHz,即每 1μs 计数单元加 1

分支 2:÷1

- 对应条件:图中AUXR.7/T0x12=1(AUXR 寄存器第 7 位设为 1)

- 功能:这是STC89C52 新增的高速分频方式------ 系统时钟不做分频,直接作为定时器 0 的计数脉冲

同样 12MHz 晶振,计数脉冲频率就是 12MHz,即每 1/12μs 计数单元加 1,计数速度比 ÷12 模式快 12 倍

中断系统就是使CPU有应对突发事件的能力而设置的,中断系统可以指定优先级的任务进行操作

STC89C52 中断资源(和定时器一样每一个型号的资源都不一样)

- 中断源个数:8 个(外部中断 0、定时器 0 中断、外部中断 1、定时器 1 中断、串口中断、外部中断 2、外部中断 3)一般的51单片机都是没有后面的外部中断1和2,STC补充了

- 中断优先级个数:4 个 (一般的也是只有2个而已)

定时器控制寄存器TCON

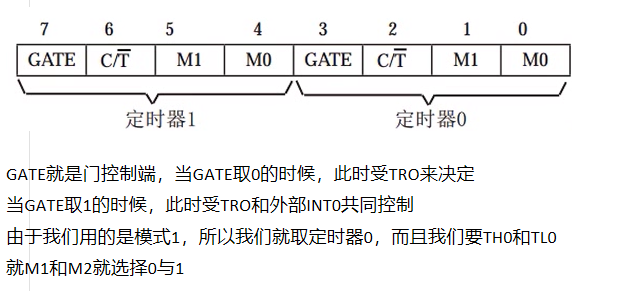

定时器模式寄存器

注意:

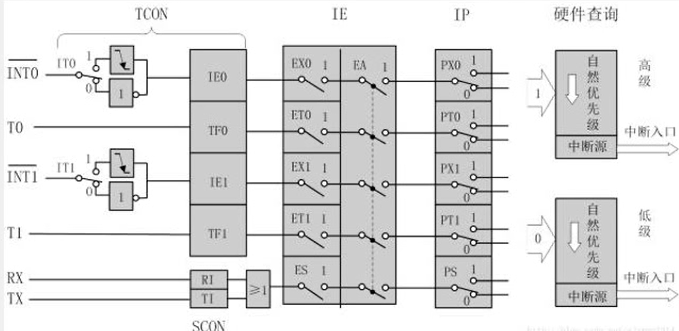

中断系统

IE 是中断允许寄存器,决定 "哪些中断能被 CPU 响应",相当于 "开关总闸 + 分闸"

- EA:中断总允许位(图中设为 1):必须置 1,所有中断才能生效;若 EA=0,所有中断都被屏蔽

- EX0:外部中断 0 的分允许位(图中设为 1):置 1 则允许外部中断 0,置 0 则屏蔽

- ET0:定时器 0 中断的分允许位(图中设为 1):置 1 则允许定时器 0 中断

- EX1:外部中断 1 的分允许位(图中设为 1):逻辑同 EX0。

- ET1:定时器 1 中断的分允许位(图中设为 0):置 0 则屏蔽定时器 1 中断

- ES:串口中断的分允许位(图中设为 1):置 1 则允许串口中断

IP 是中断优先级寄存器,决定 "多个中断同时请求时,先响应谁",51 架构支持 "高、低"2 个优先级:

- PX0:外部中断 0 的优先级(图中设为 1):1=高优先级,0=低优先级

- PT0:定时器 0 的优先级(图中设为 0):0=低优先级

- PX1:外部中断 1 的优先级(图中设为 1):高优先级

- PT1:定时器 1 的优先级(图中设为 0):低优先级

- PS:串口中断的优先级(图中设为 0):低优先级