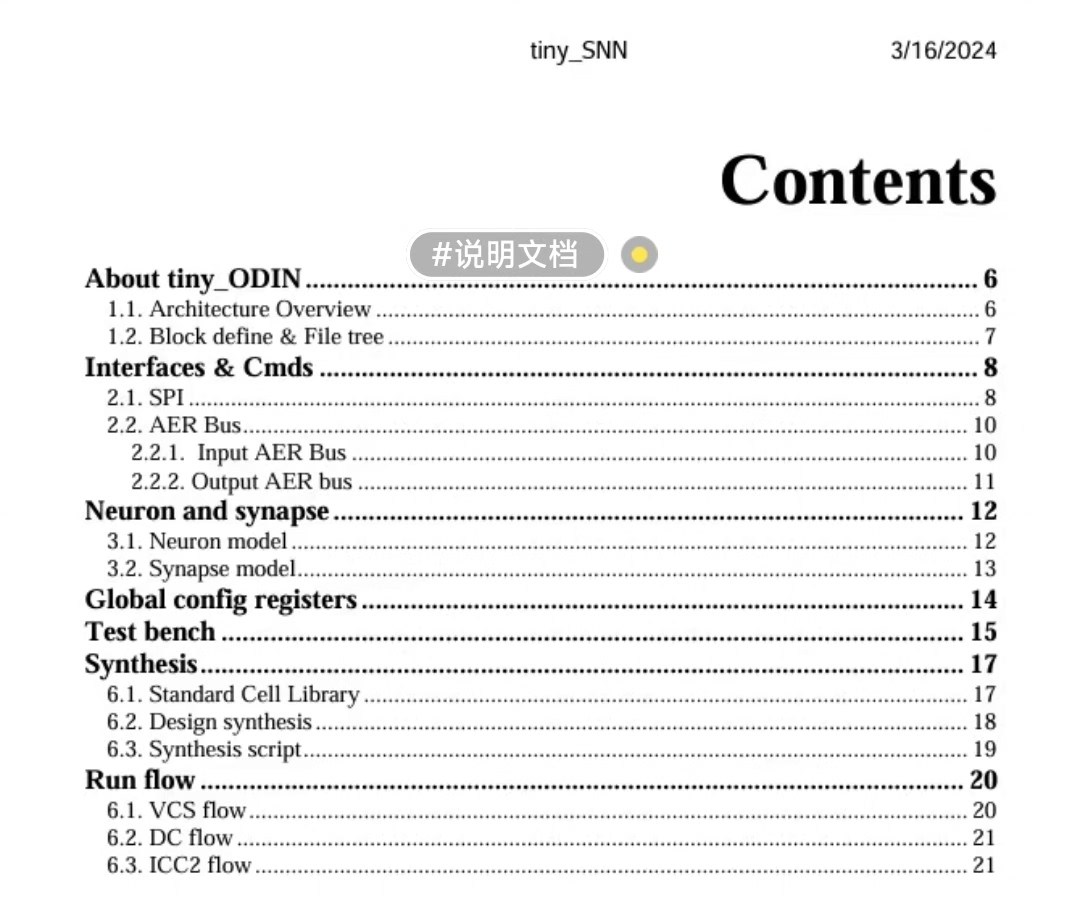

数字IC新手项目,从RTL、综合到floorplan,前仿到门级电路布局。 40nm工艺,SNN加速器。 设计和流程说明文档rtl源代码门级电路综合报告ICC2布局 [1]vcs 前仿真 dc综合 icc2布局 [2]40nm工艺库综合,10m布局 [3]面积 qor timing power等报告 带有完整makefile和tcl脚本,自动化流程

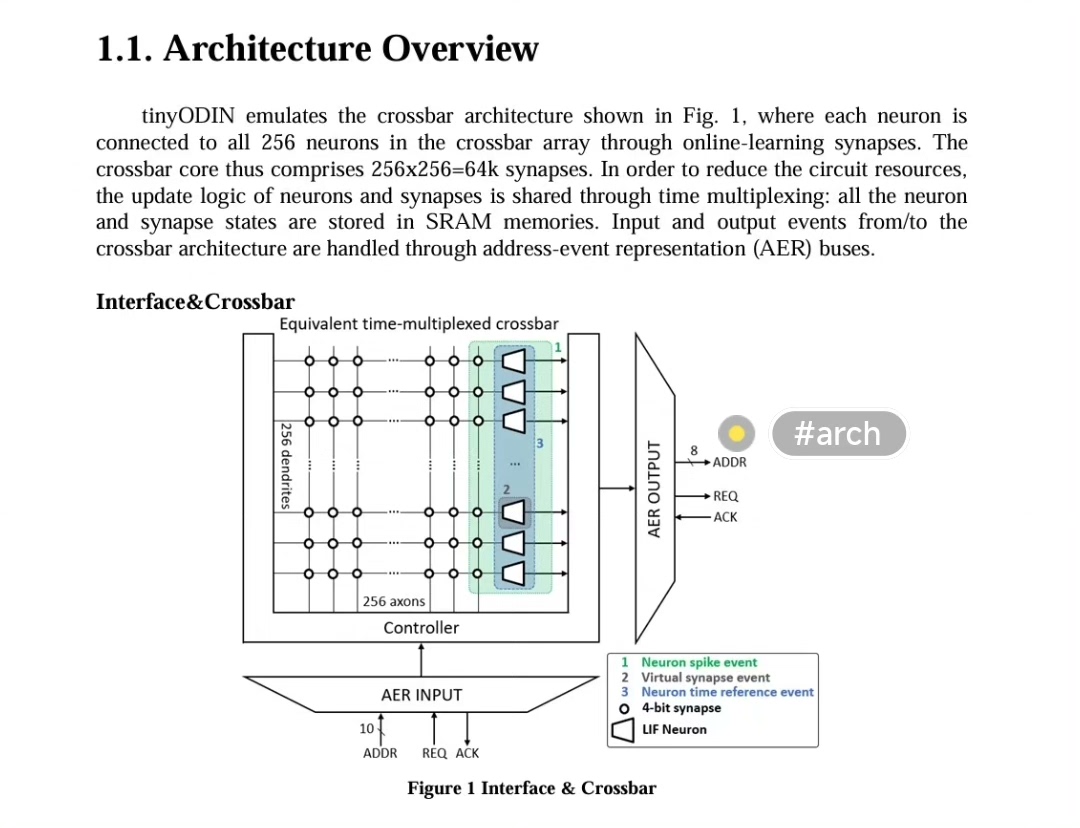

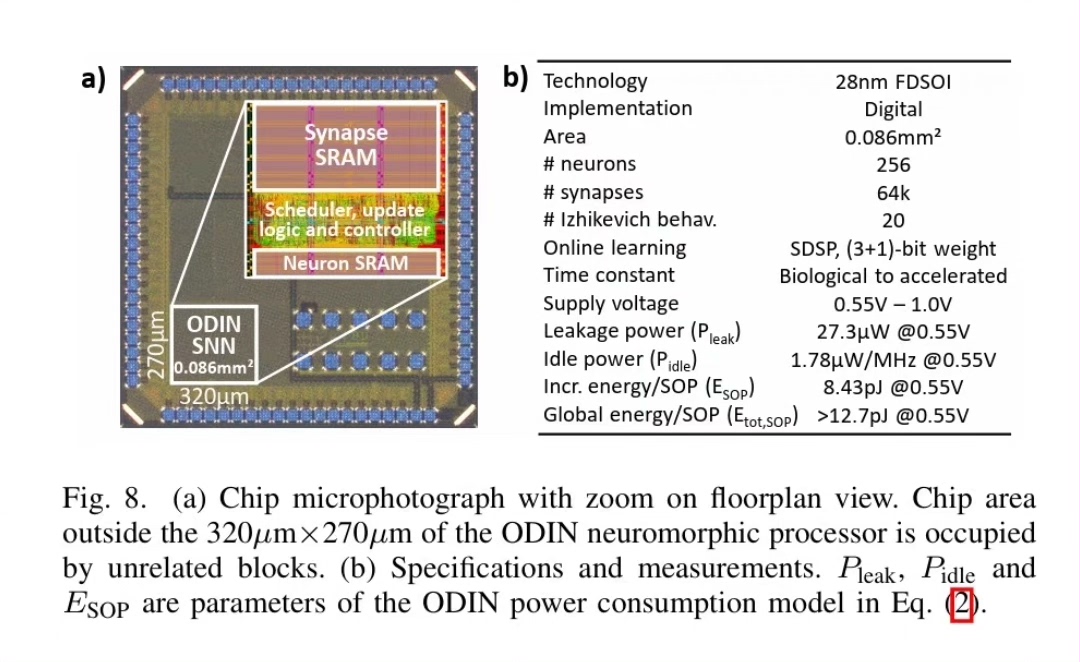

最近在做一个超有意思的数字IC项目,基于40nm工艺打造SNN加速器 ,从RTL设计一路走到门级电路布局,这过程就像一场探索数字世界的冒险,现在就来跟大家分享分享。

RTL设计:项目的起点

RTL(Register Transfer Level)设计是整个项目的根基。我们的SNN加速器RTL代码是这样的,以一个简单的神经元模块为例:

verilog

module neuron (

input wire clk,

input wire rst,

input wire [31:0] input_signal,

output reg [31:0] output_signal

);

reg [31:0] internal_state;

always @(posedge clk or posedge rst) begin

if (rst) begin

internal_state <= 32'b0;

output_signal <= 32'b0;

end else begin

// 这里简单模拟神经元计算,实际可能更复杂

internal_state <= internal_state + input_signal;

if (internal_state > 32'd100) begin

output_signal <= 32'd1;

end else begin

output_signal <= 32'd0;

end

end

end

endmodule这段代码定义了一个神经元模块,在时钟上升沿或者复位信号有效时,会对输入信号进行处理,根据内部状态决定输出。这只是一个简单示例,实际的SNN加速器会有大量神经元模块以及复杂的连接关系。

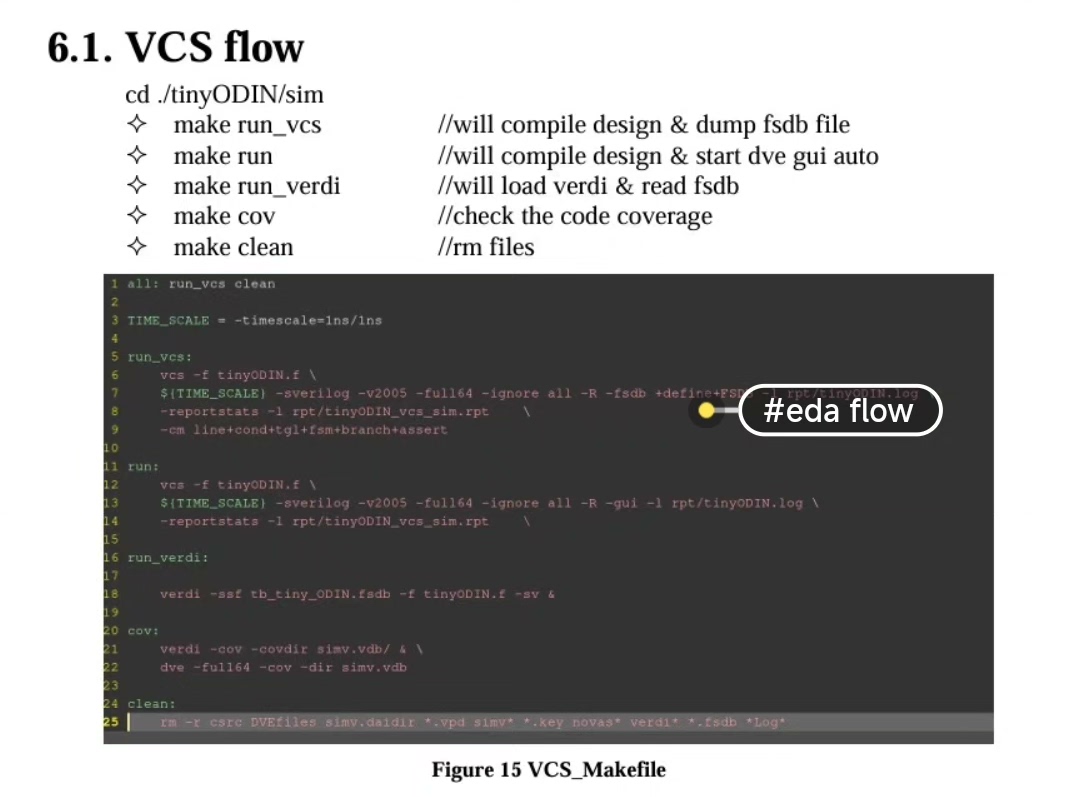

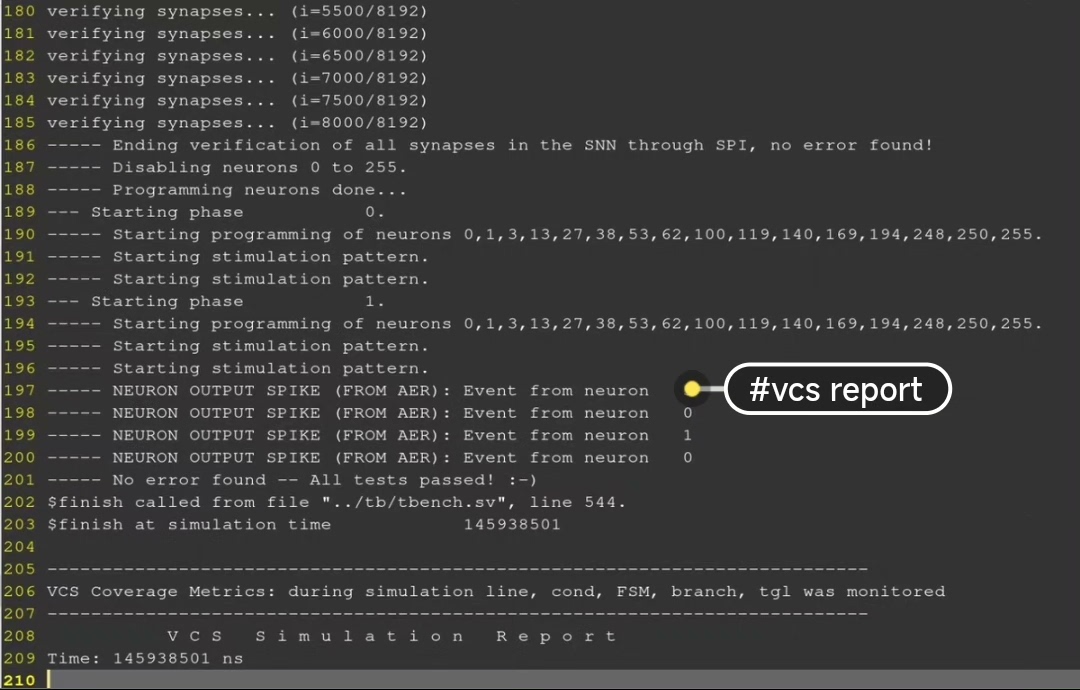

前仿真:确保设计正确性

前仿真我们选用了vcs工具。在运行vcs前,需要编写测试平台(testbench)。以下是上述神经元模块的测试平台代码:

verilog

module tb_neuron;

reg clk;

reg rst;

reg [31:0] input_signal;

wire [31:0] output_signal;

neuron uut (

.clk(clk),

.rst(rst),

.input_signal(input_signal),

.output_signal(output_signal)

);

initial begin

clk = 0;

forever #5 clk = ~clk; // 10ns周期的时钟

end

initial begin

input_signal = 32'd0;

rst = 1;

#10;

rst = 0;

#20;

input_signal = 32'd50;

#20;

input_signal = 32'd70;

#20;

$finish;

end

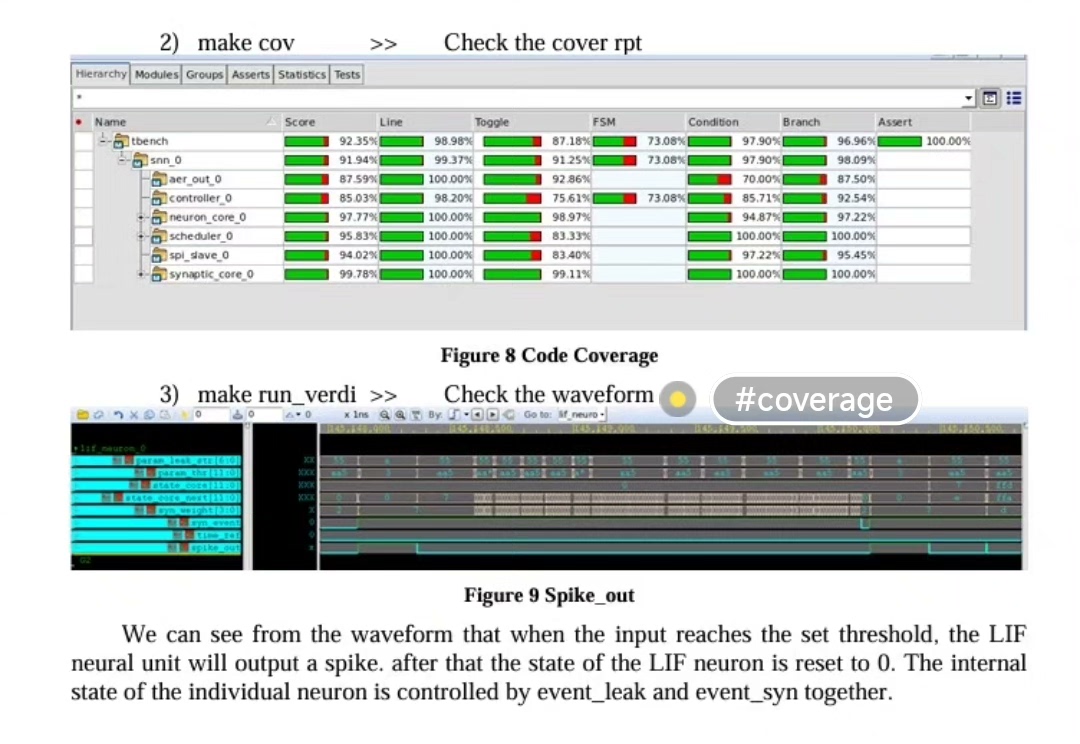

endmodule通过这个测试平台,我们模拟了时钟信号、复位信号以及输入信号的变化,来观察神经元模块的输出是否符合预期。然后在终端运行vcs相关命令就可以进行仿真了,例如:vcs -full64 -sverilog tb_neuron.v neuron.v,运行成功后查看波形文件,就能清楚看到各个信号的变化,确保设计在功能上是正确的。

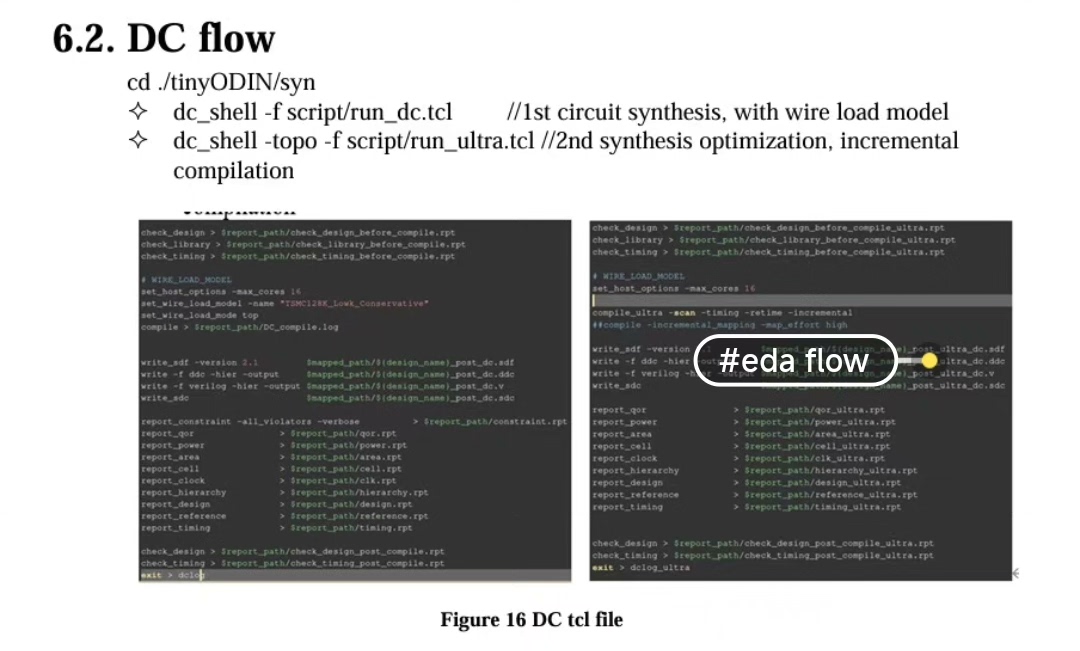

综合:从RTL到门级网表

综合阶段我们使用Design Compiler(DC)。首先要准备好工艺库,这里是40nm工艺库。在DC中,通过TCL脚本进行综合操作。下面是一段简单的TCL脚本示例:

tcl

# 设置搜索路径

set search_path [list. /path/to/40nm_lib]

# 读入RTL文件

read_verilog neuron.v

# 定义工艺库

link_library {*40nm_lib.db}

# 综合

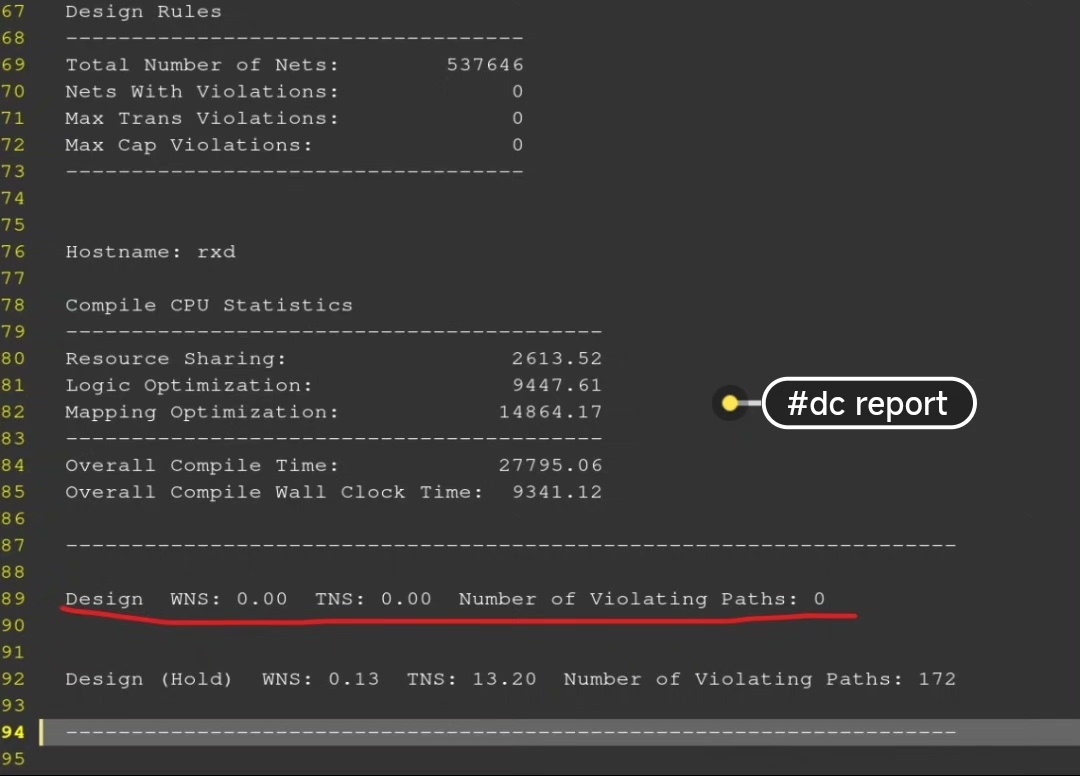

compile这段脚本设置了搜索路径,读入RTL文件,指定工艺库,最后执行综合操作。综合完成后,DC会生成门级网表文件,这时候设计就从RTL描述转变为了门级电路描述。同时,还会生成综合报告,像面积、QoR(Quality of Result)、timing以及power等关键指标都会在报告里呈现。通过分析这些报告,我们可以了解设计的优劣,为后续优化提供依据。

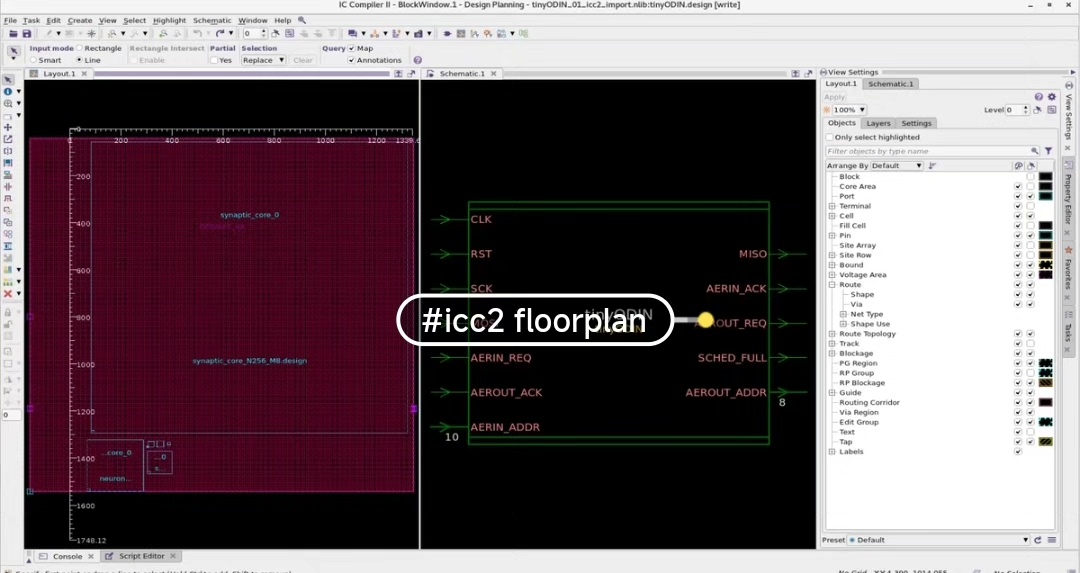

ICC2布局:打造物理版图

完成综合后,就进入到ICC2布局阶段。同样,这也依赖TCL脚本实现自动化流程。以下是简单的布局TCL脚本框架:

tcl

# 设置工作目录

set_app_var work_dir./icc2_work

# 读入门级网表

read_netlist neuron.vg

# 设置工艺相关参数

set_physical_library *40nm_tech.lib

# 布局规划

create_fp_plane -core_area 10m -site CORE_SITE

# 布局

place_opt_design这里先设置了工作目录,读入门级网表,然后设置工艺库,接着规划了一个10m大小的核心区域用于布局,最后执行布局优化操作。通过ICC2的一系列操作,我们将门级网表转换为了物理布局,为后续的布线等后端设计奠定基础。

整个项目带有完整的makefile和TCL脚本,实现了自动化流程。比如makefile可以这样写:

makefile

SIM:

vcs -full64 -sverilog tb_neuron.v neuron.v

./simv

SYNTHESIS:

dc_shell -f synth.tcl

PLACEMENT:

icc2_shell -f place.tcl通过简单的make SIM、make SYNTHESIS、make PLACEMENT命令,就能轻松执行前仿真、综合和布局操作,大大提高了项目的效率。

这次数字IC新手项目,从RTL设计到门级电路布局,每一步都充满挑战与收获。希望我的分享能给同样在数字IC领域探索的小伙伴们一些启发。