基于FPGA的相位差测量设计 程序注释清晰

在数字电路和信号处理领域,相位差测量是一个常见且重要的任务。FPGA(现场可编程门阵列)以其灵活性和并行处理能力,成为实现相位差测量的理想平台。今天就来聊聊基于FPGA的相位差测量设计。

基本原理

要测量两个信号的相位差,我们可以利用数字电路对信号的上升沿或下降沿进行捕捉。假设我们有两个输入信号 signalA 和 signalB,通过记录它们上升沿之间的时间差,再结合系统时钟,就能计算出相位差。

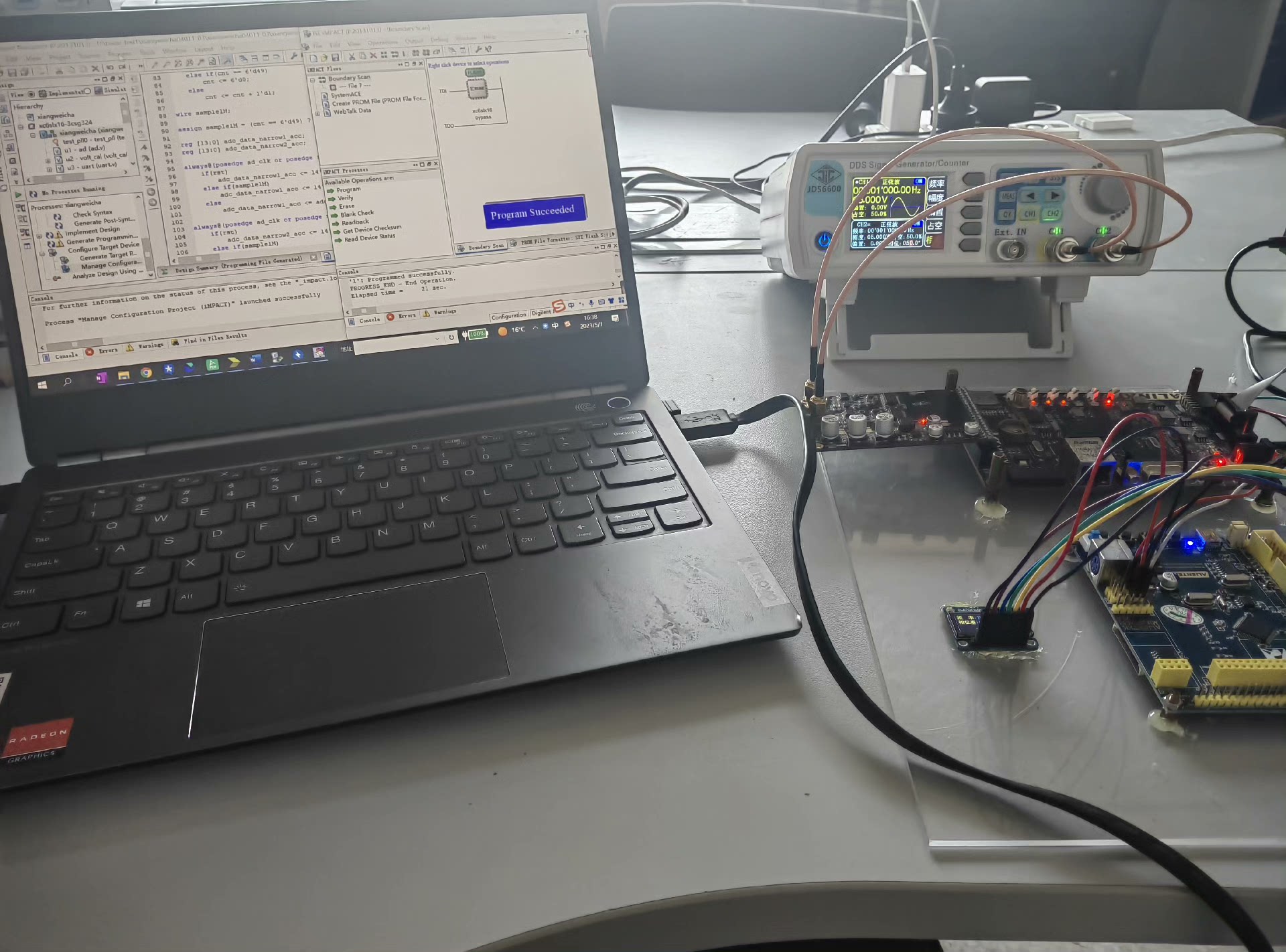

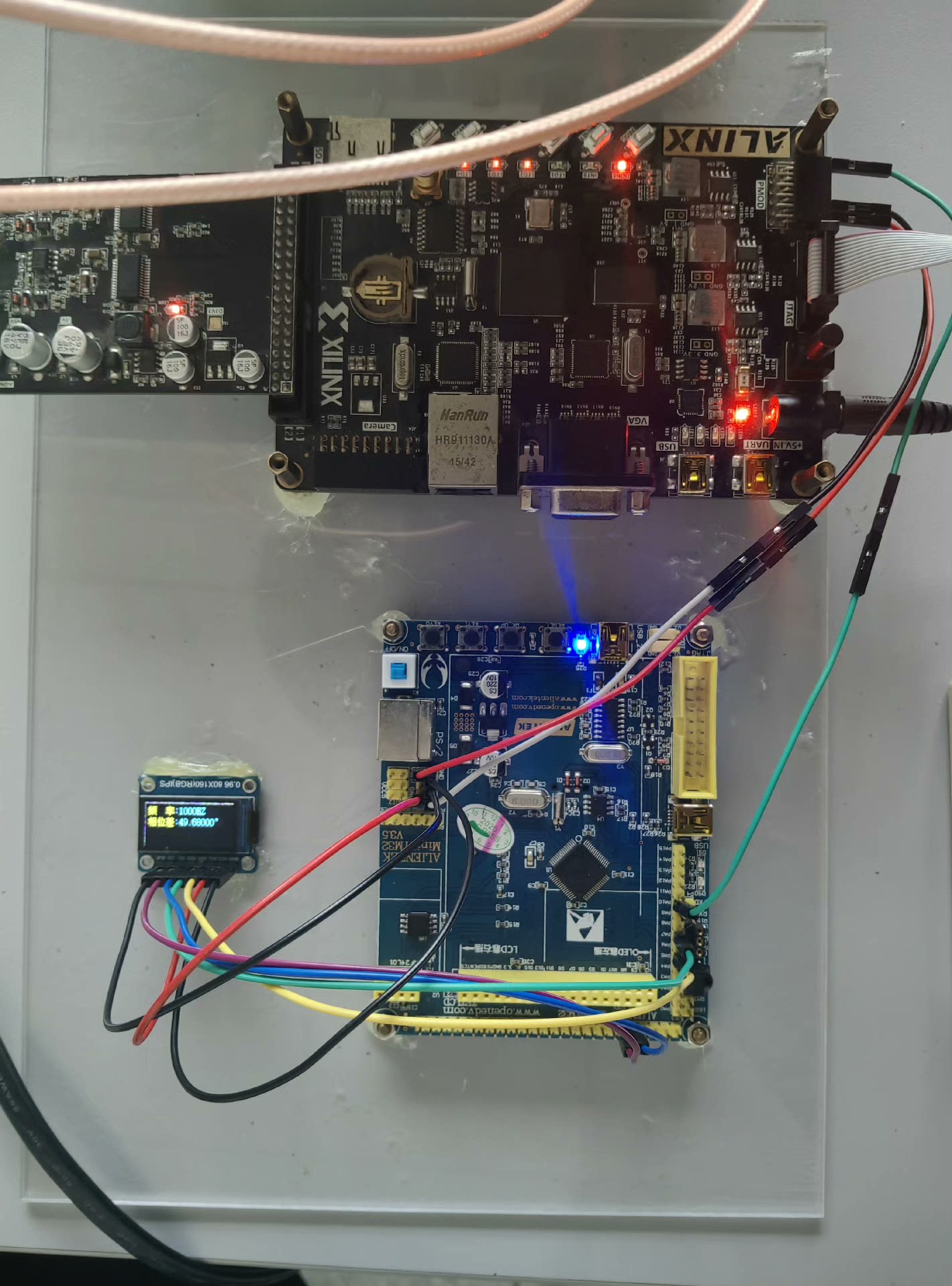

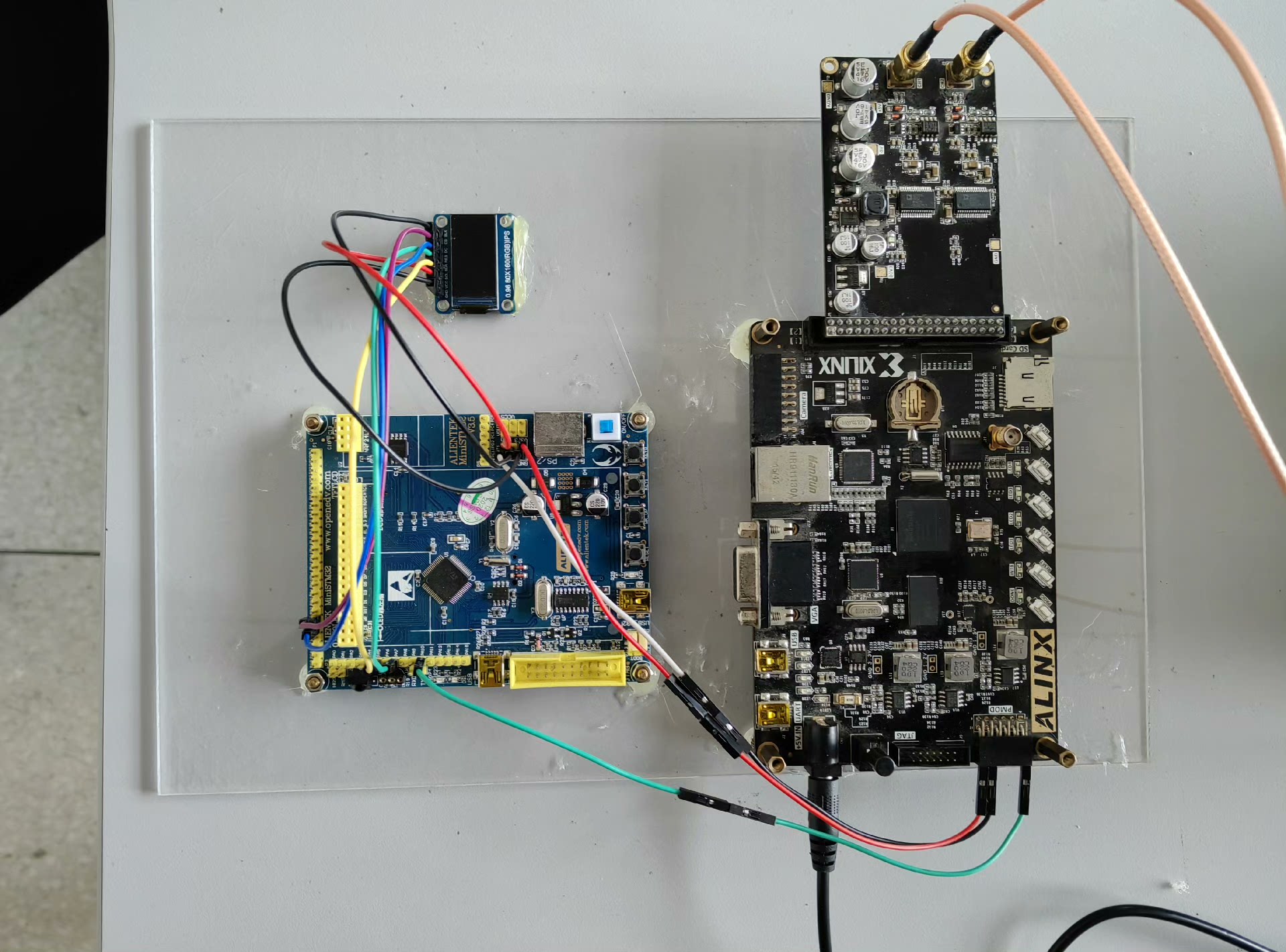

FPGA 实现代码

下面我们来看一段简单的Verilog代码示例,实现对两个信号相位差的初步捕捉。

verilog

module phase_difference_measurement (

input wire clk, // 系统时钟

input wire rst, // 复位信号

input wire signalA, // 输入信号A

input wire signalB, // 输入信号B

output reg [31:0] phase_diff_count // 用于记录相位差的计数值

);

reg signalA_previous;

reg signalB_previous;

reg [31:0] count;

always @(posedge clk or posedge rst) begin

if (rst) begin

signalA_previous <= 0;

signalB_previous <= 0;

count <= 0;

phase_diff_count <= 0;

end else begin

signalA_previous <= signalA;

signalB_previous <= signalB;

// 检测 signalA 的上升沿

if (!signalA_previous && signalA) begin

count <= 0;

end

// 检测 signalB 的上升沿

else if (!signalB_previous && signalB) begin

phase_diff_count <= count;

end

// 计数

count <= count + 1;

end

end

endmodule代码分析

- 模块定义 :

module phasedifferencemeasurement定义了一个名为phasedifferencemeasurement的模块,它有五个端口:clk(系统时钟)、rst(复位信号)、signalA和signalB(两个待测量相位差的输入信号),以及phasediffcount(用于输出相位差的计数值)。 - 内部寄存器定义 :

signalAprevious**和signalBprevious用于存储上一个时钟周期signalA和signalB的值,以便检测上升沿。count是一个32位的计数器,用于记录两个信号上升沿之间的时钟周期数。 - always 块 :在

always @(posedge clk or posedge rst)块中,当rst信号为高电平时,所有寄存器被复位到初始值。当rst为低电平时,在每个时钟上升沿,更新signalAprevious**和signalBprevious的值。- 如果检测到

signalA的上升沿(!signalAprevious && signalA*),将count清零,开始新一轮计数。 - 如果检测到

signalB的上升沿(!signalB*previous && signalB),将当前的count值赋给phasediffcount,这个phasediffcount就是两个信号上升沿之间的时钟周期数,代表了相位差的一个量化值。 - 无论如何,每个时钟周期

count都会加1。

- 如果检测到

后续处理

通过上述代码得到的 phasediffcount 只是一个量化的计数值。要得到实际的相位差,我们还需要结合系统时钟的周期进行换算。假设系统时钟周期为 T_clk,则相位差 \\theta 可以通过以下公式计算:

\\theta = \\frac{phase\\*diff\\*count \\times 360\^{\\circ}}{N}

其中 N 是在一个完整周期内的时钟周期数,与信号频率和系统时钟频率相关。

基于FPGA的相位差测量设计为我们提供了一种灵活且高效的方式来处理相位差测量任务。通过合理的逻辑设计和代码实现,能够满足不同应用场景下对相位差测量的精度和速度要求。希望这篇文章能为你在相关领域的学习和实践中提供一些帮助。

以上代码只是一个基础示例,实际应用中可能需要根据具体需求进行优化,比如提高测量精度、处理更高频率信号等。大家可以一起探讨更多的改进方向。