DDR5 Write leveling

-

- [0 开始之前](#0 开始之前)

- [1 背景](#1 背景)

- [2 步骤](#2 步骤)

- [3 时序](#3 时序)

- [4 总结](#4 总结)

本系列博客中介绍,记录一些DDR5 中涉及的特性和调试经验,大家有需要可以收藏,有问题欢迎交流讨论,不足之处欢迎指出。

0 开始之前

博主之前调试过LPDDR4 内存控制器的上电Calibration。对于LPDDR4来说,Write leveling的实现方式,简单又粗暴:调整DQS(从memory controller到DRAM方向)与DRAM CK的相位关系,并且以DRAM CK为参考,调整DQS直到与DRAM CK对齐(上升沿对上升沿)。

然而对于DDR5来说,有一些不同之处,需要先进行外部write leveling,对齐管脚,再进行内部write leveling以"降低功耗与延时"(JESD79-5的官方套话)。

对于内部write leveling 的具体作用,

Deepseek表示:"DDR5的数据速率能达到6400Mbps甚至更高,在这种极端速度下,不仅仅是PCB板级的信号延迟问题(这是External Write Leveling解决的),连芯片内部路径的微小差异都会成为瓶颈。之前几代速度没那么高,内部路径的时序差异可以靠设计余量消化掉,但DDR5不行了,必须主动进行内部校准。"

整体来看复杂了不少,因此写下这篇博文进行记录。

1 背景

本文中并不过多赘述,write leveling 的目的。

DDR5中,在write leveling方面有更新。支持两种模式,外部write leveling,内部write leveling,并且是先进行外部write leveling, 在此基础上进行内部write leveling。

如何理解这两种模式?

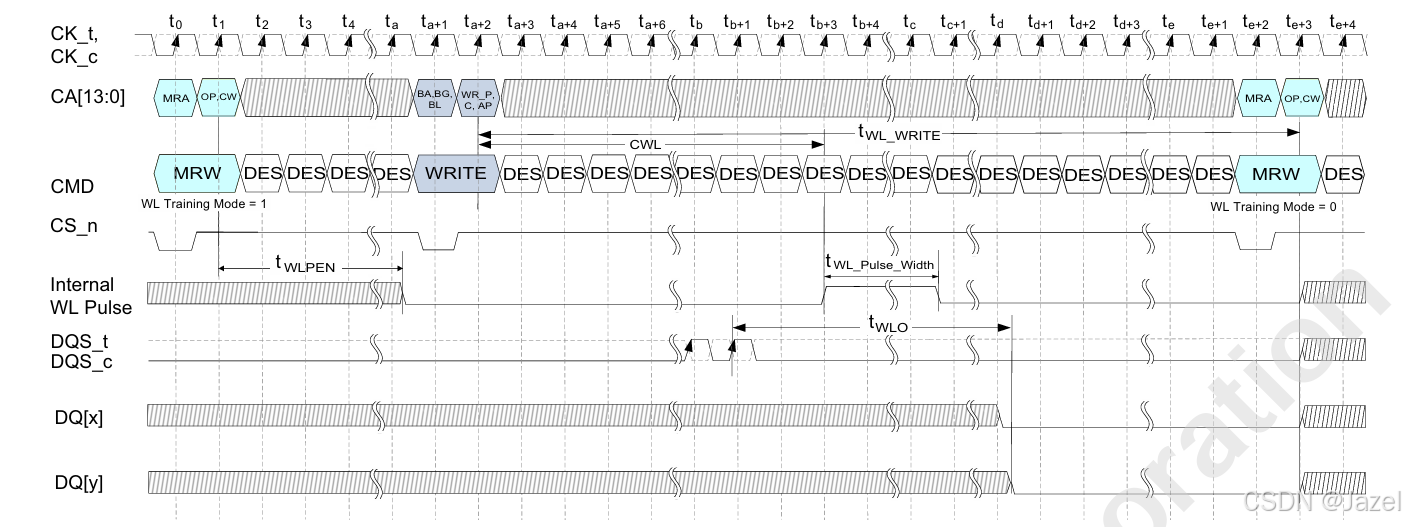

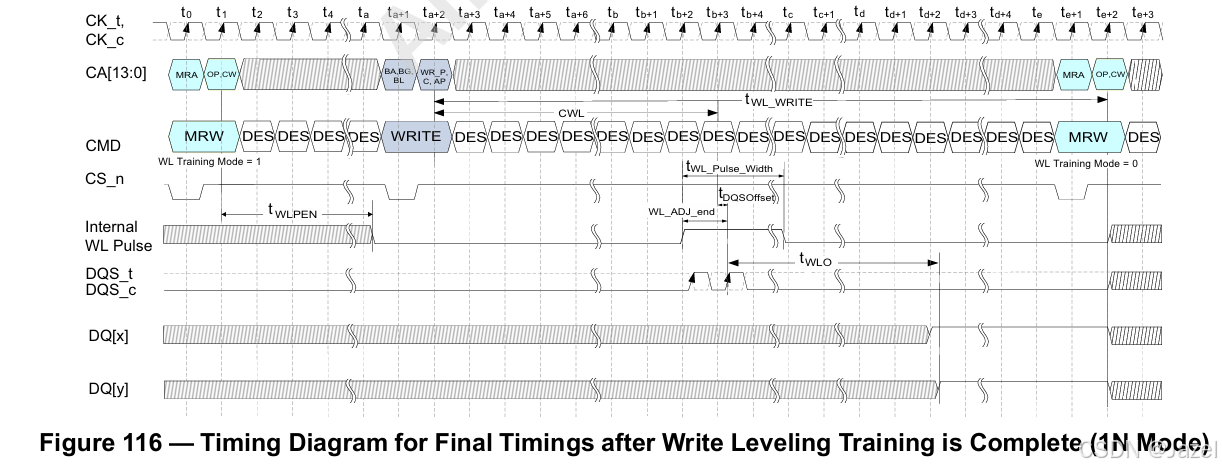

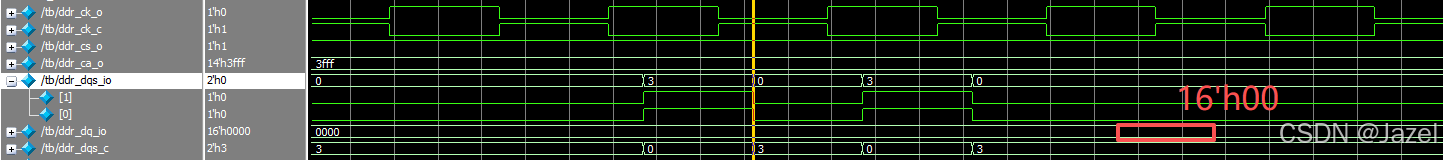

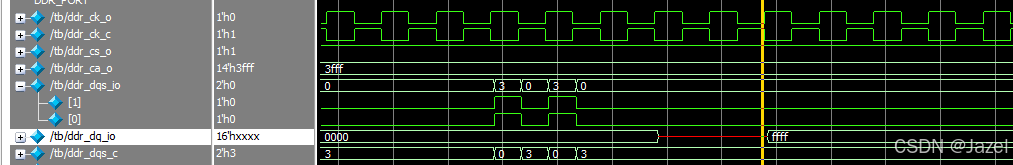

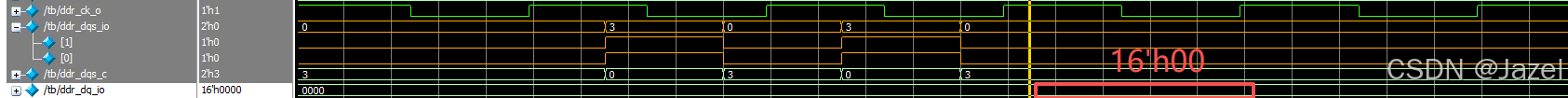

外部Write leveling\]: 使用DRAM内部产生的write leveling 脉冲作为"参考",这个脉冲信号与CK的上升沿对齐。DDR5中,DQS不再是需要单纯地,调节管脚上的DQS与CK之间的相位。而是进一步的,加入了write latency。 \[内部Write leveling\]: 在外部Write leveling的基础上,继续调节DQS,并且还要调节 DRAM内部产生的write leveling 脉冲的相位。 ### 2 步骤 **2.1 外部Write leveling** 开局来张图:  ***步骤1***,t0之前:将DQS_t拉低,DQS_c拉高 ***步骤2***,t0,t1: 发送MRW配置Mode register MR02 第1bit,进入write leveling 模式 ***步骤3***,t1-ta:等待至少tWLPEN(15ns) ***步骤4***,ta+1,ta+2:发送 写 命令 ***步骤5***,tb+3时,内部脉冲会拉高,memory controller 发出的DQS脉冲如果在tb, tb+1处,那么采到的内部脉冲将会是0,经过tWLO之后,从DQ中返回采样值。(可参考时序部分图1) ***步骤6*** ,给DQS_t, DQS_c加延时 重复步骤1-6,直到DQ采样值从0变为1(大概是DQS_t,DQS_c右边的上升沿与tb+3对齐的样子),表示此时的DQS已经能够采样到内部write leveling 脉冲的高电平。(可参考时序部分图2) **2.2 内部Write leveling** 在外部Write leveling 已经完成的情况下,此时DQS理当能够采集到write leveling 脉冲高电平。 ***步骤7*** ,把DQS_t, DQS_c 往左移,移动的步长为WL_ADJ_start\*,他的值需要依据write preamble来决定,JESD79-5上面有相应关系的表格。举例来说,如果Write preamble=2, WL_ADJ_start=-0.75tCK。 此时的DQ采样值应当是'0',(可参考时序部分图3) ***步骤8***,通过写mode register MR03设置,把内部脉冲向左移动,单位是tCK。目的是使DQ采样值从'0' 变为'1'。 ***步骤9***,继续把DQS_t, DQS_c 往左移,知道采样值又变为'0'。目的是跟内部脉冲对齐,因为内部脉冲它每次delay的单位是tCK,步长太大。 ***步骤10*** ,最终步。将DQS_t, DQS_c向右移动,移动的步长为WL_ADJ_end\*,这个值也是根据write preamble来决定的。举例来说,如果Write preamble=2, WL_ADJ_end=+1.25tCK.。 最终相位关系见该图  > \*参数释义 > > WL_ADJ_start:开始内部write leveling的时候,首先需要移动DQS_t,DQS_c的相位, 方向:左移。 > > WL_ADJ_end: 完成内部write leveling的时候,需要移动DQS_t,DQS_c的相位,方向:右移。 > > WICA:指的是这个内部产生的write leveling 脉冲的delay,方向:左移。 ### 3 时序 外部training开始时,可以看到DQ\[15:0\]全部输出低电平:  **图 1 '步骤5'对应波形** 外部training完成时,可以看到DQ\[15:0\]已经全部输出高电平了:  **图 2 '步骤6'对应波形**  **图3 '步骤7'对应波形** ### 4 总结 在LPDDR4 中,完成write leveling 之后,只能保证DQS与CK的相位关系,write latency错了也没关系。真正调节write latency,是在 write training中进行调节的。 但是从DDR5外部Write leveling的步骤来看,似乎DDR5的机制更加科学合理,完成write leveling之后,既保证了DQS和CK的相位关系,又保证了匹配的write latency,因此,到了后面的write training中,只需要调节DQ的延迟即可,不必再考虑write latency。 然而,做完外部和内部Write leveling,从memory controller的开发角度来看,难度可谓是增加了亿点点。