基础信息

FPGA芯片:xc7v690tffg1761-2L

vivado版本:vivado2018.3

测试板卡:优数科技 PCIe-404、som-404 信号处理模块

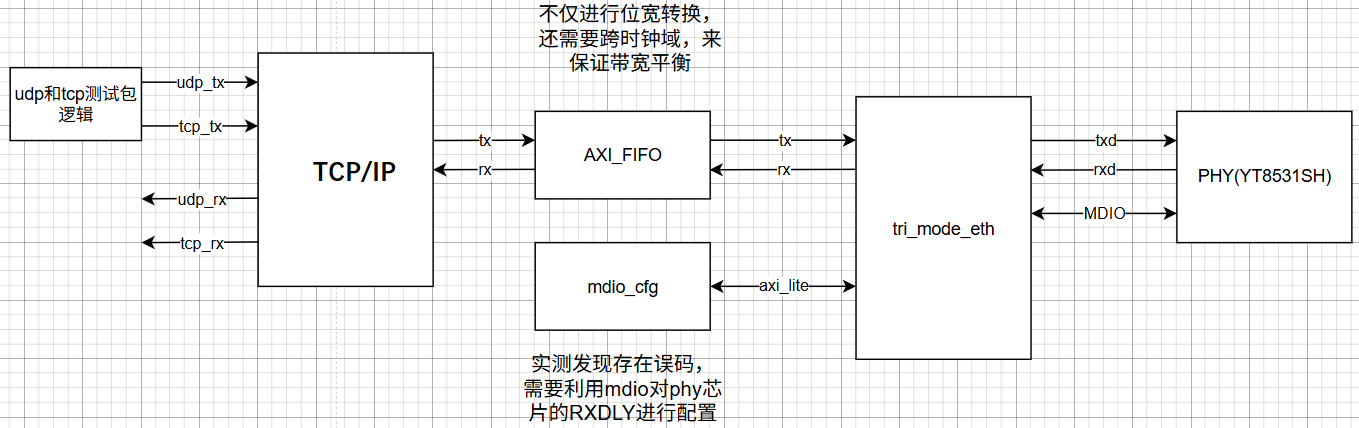

基本架构

说明

- TCP/IP协议栈: 核心的TCP/IP代码,支持ICMP,UDP,TCP,ARP等以太网报文处理。

- Tri_mode_eth:xilinx的千兆网IP_CORE,当前使用RGMII与以太网芯片交互。

- Mdio_cfg:解决误码问题,在本模块进行RXDLY的微调设置,需要根据不同的板卡确定调整值。

实际测试

基础配置

- FPGA_IP地址:192.168.1.30

- FPGA_MAC地址:0x1234_5678_9abb

- 上位机IP地址:192.168.1.26

交互情况

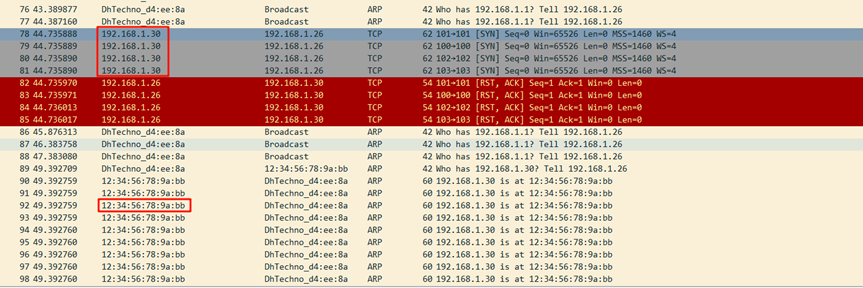

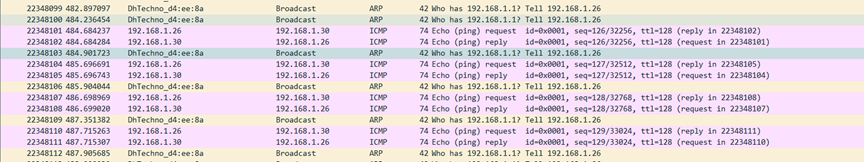

上板测试后,发现FPGA与电脑之间存在报文交互,交互正常。

如下图,arp报文和TCP报文可以正常发送至上位机。

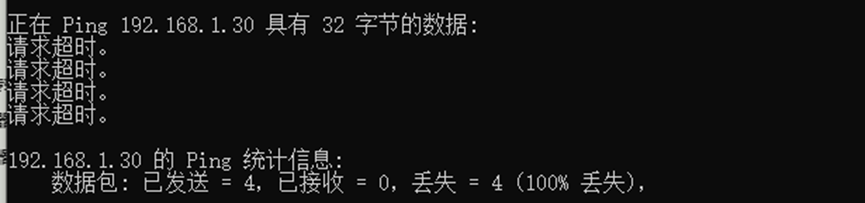

PING异常

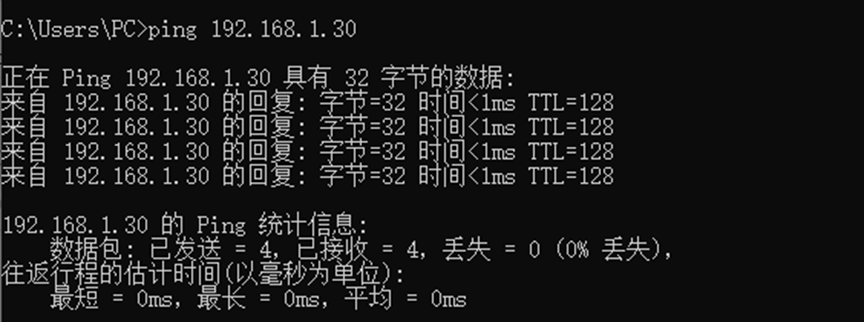

在电脑端ping 192.168.1.30地址,发现ping不通,但wireshark抓包发现FPGA与电脑可正常收发包。

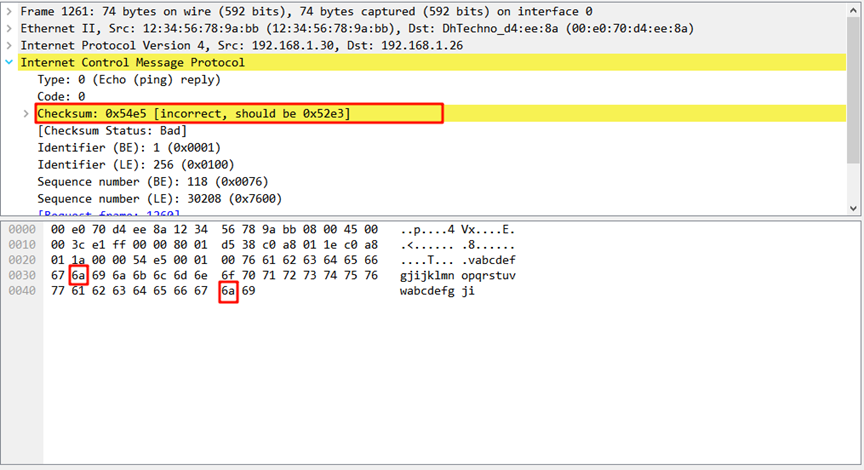

如下图所示,用wireshark抓取ping报文,发现FPGA对ping是有回复的,但是回复的报文在异常,check_sum错误,回复数据也存在异常。本应该6768696a的数据,变为676a696a,分析是存在1位的错误。

在抓取了FPGA内部收到的ping报文后,发现从PHY芯片进入FPGA的报文就已经错了,因此怀疑硬件PCB走线问题。更换PCB板卡后,测试正常。在查阅pg051和以太网PHY芯片的数据手册后,决定尝试通过微调RXDLY的值解决问题。误码如何解决详情见MDIO配置RXDLY延迟章节。

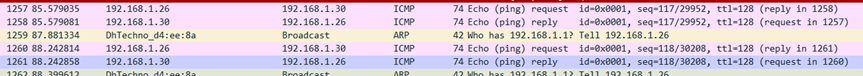

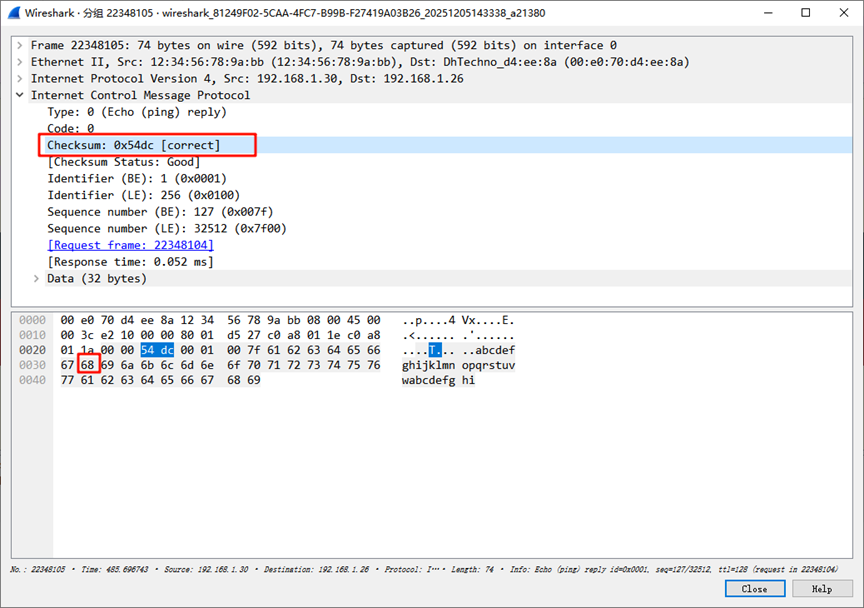

通过修改RXDLY后,再次进行ping报文的操作,发现此时是可以ping通的。

通过wireshark抓包,可以看到此时reply的数据是正常的。

性能及资源

在解决了误码情况后进行性能测试。

性能

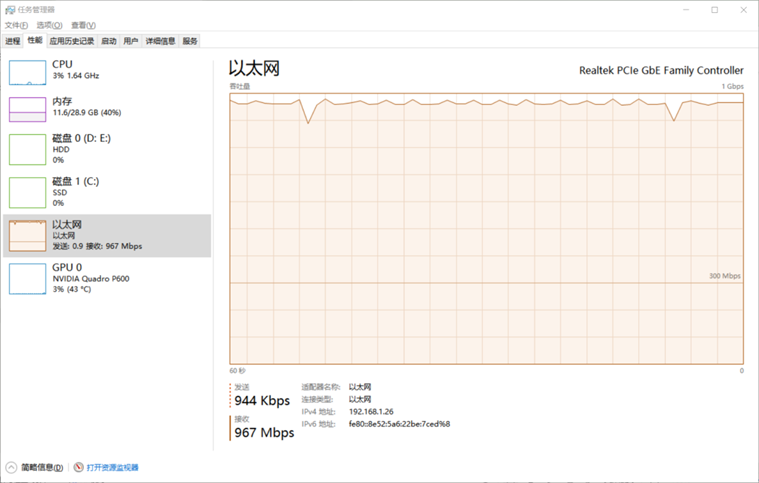

UDP性能测试

千兆网,UDP测试性能在970Mbp左右。

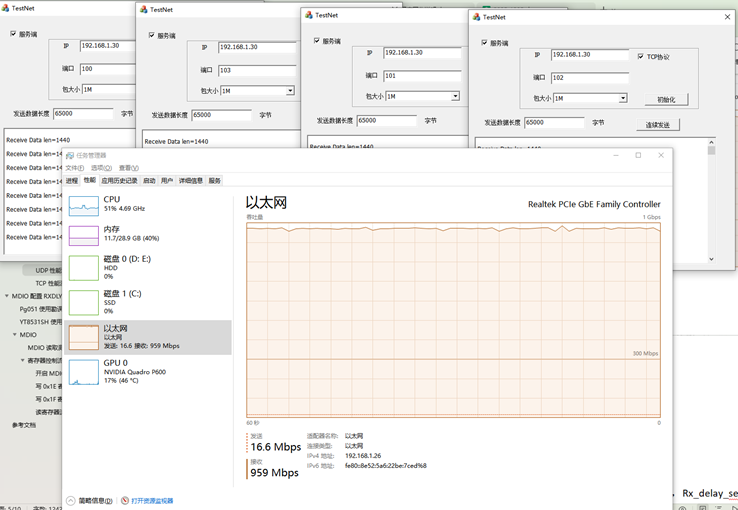

TCP性能测试

TCP的4个port测试,性能在960Mbps左右

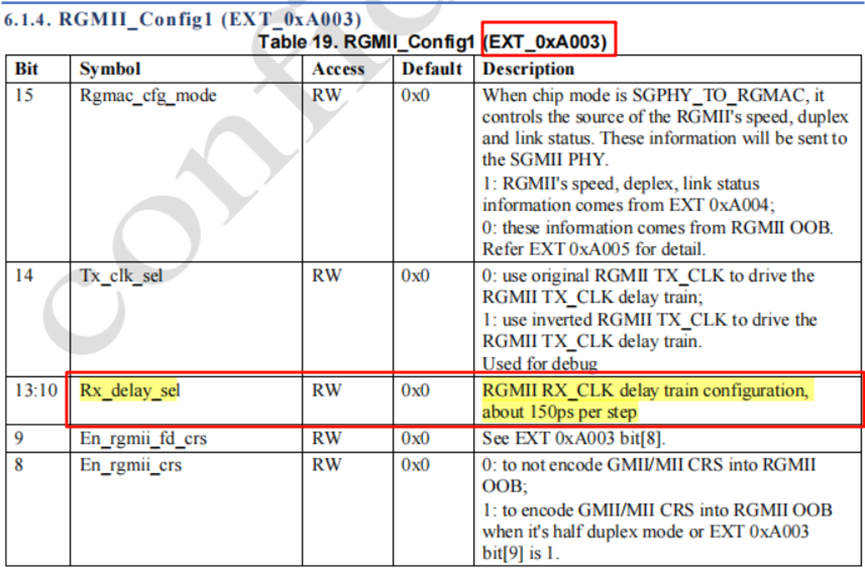

MDIO配置RXDLY延迟

目标是通过MDIO调节Rx_delay_sel的值解决误码问题,如下图所示,Rx_delay_sel位于EXE_0xA003寄存器的【13:10】bit.每步长为150ps.

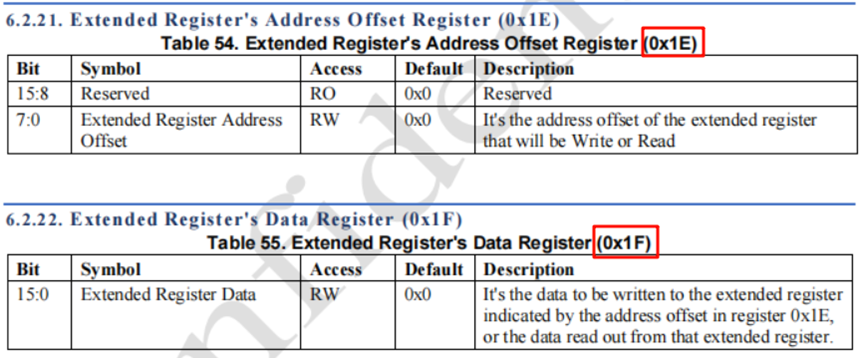

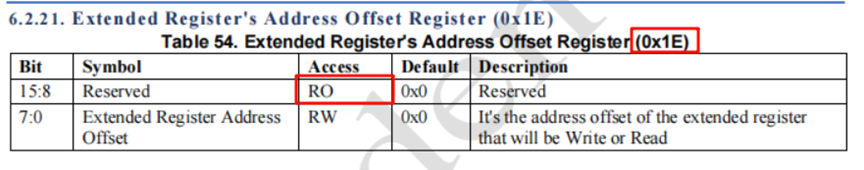

查阅YT8531SH数据手册发现,通过配置0x1E寄存器和0x1F寄存器来实现对扩展寄存器的访问。

Pg051使用勘误

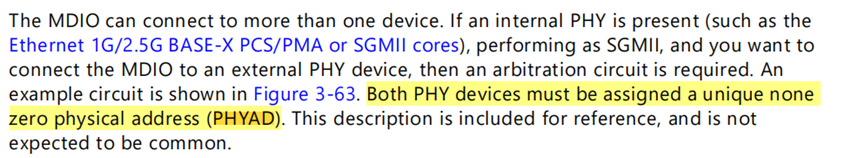

- PHY地址的确定,xilnx手册中描述phy地址不能为0.但是实测发现当前只有1个phy时,仅当 phy 地址为0 才能读取到正确的数据,其他的phy地址时,读取到的数据全部为0xffff。

YT8531SH使用勘误

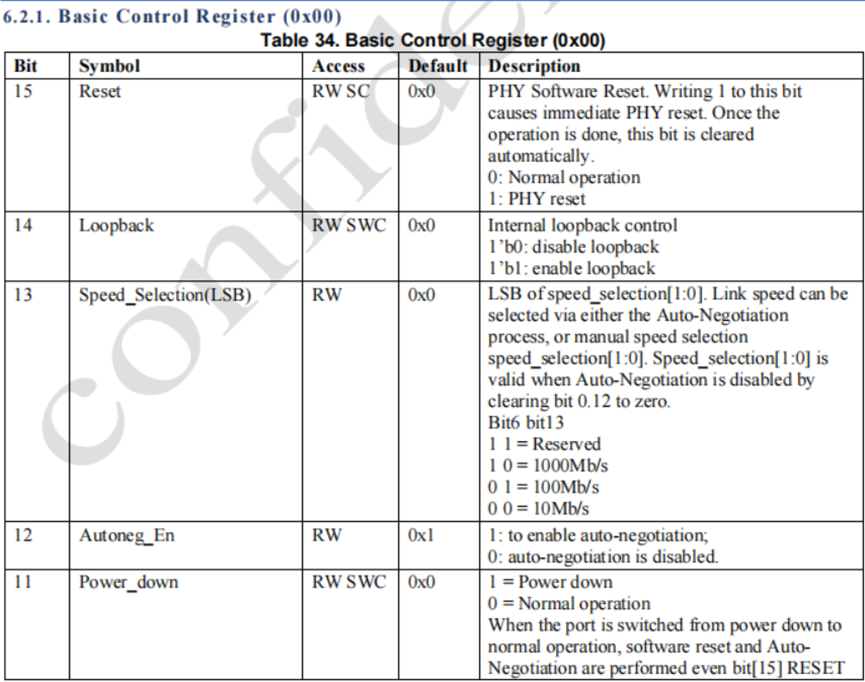

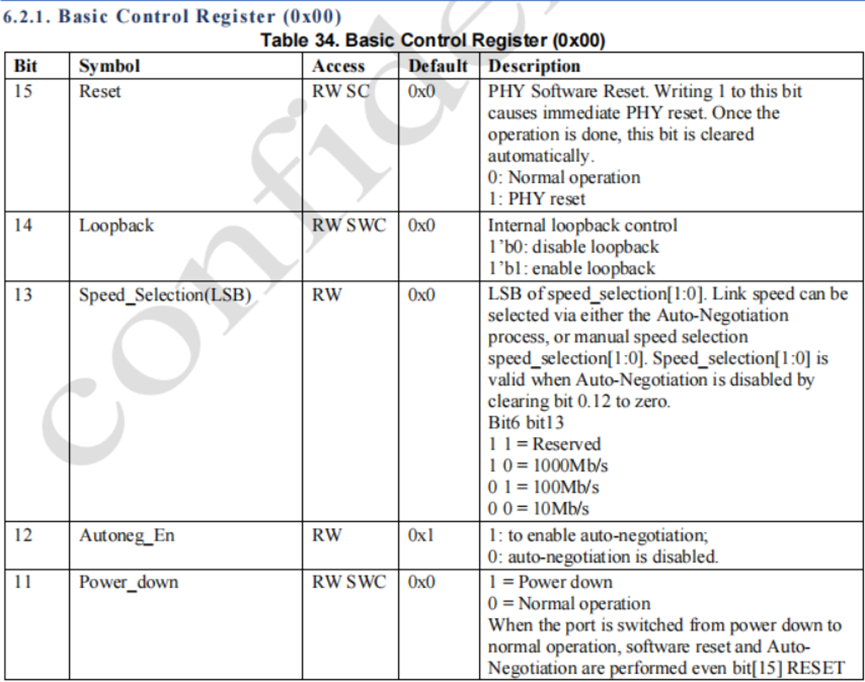

1.如下图,使用是需要配置0x1E寄存器配置为0xA003,图中显示仅【7:0】bit是可写的,【15:8】bit是仅读的,但实际测试发现,整个0x1E寄存器的16bit都是可读可写的,否则无法将0xA003写入。

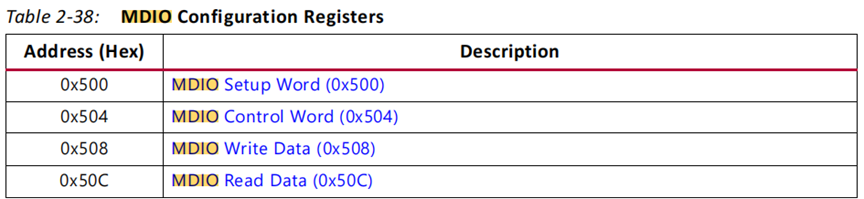

MDIO

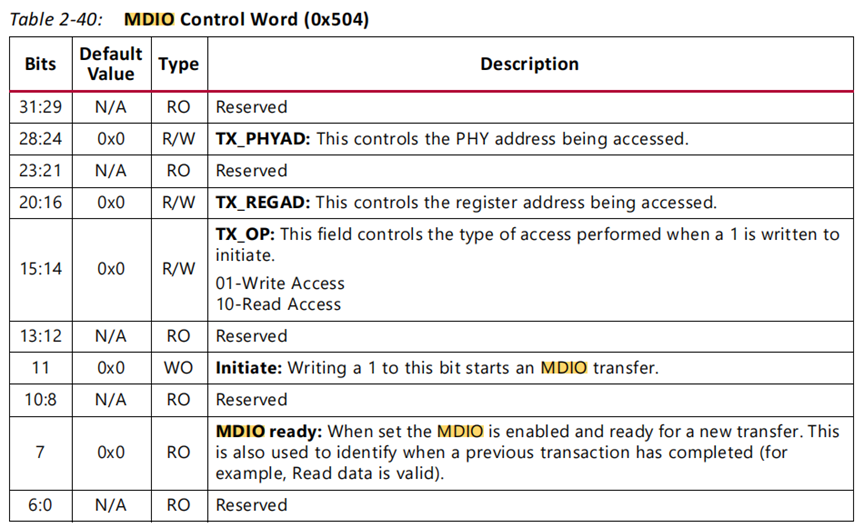

寄存器说明

Xilinx通过axi_lite接口配置MDIO需要关注以下寄存器。

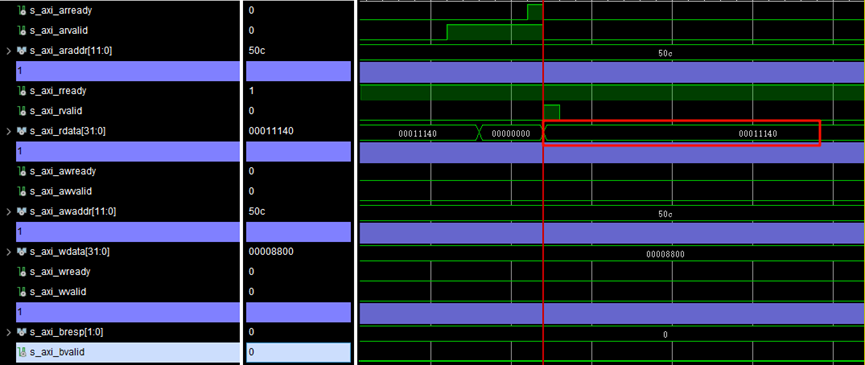

MDIO读取测试

进行初步的测试,观察当前使用读取phy芯片的0x0寄存器,回读的数据,为0x1140,与YT8531SH数据手册之中phy芯片的0x0寄存器默认值能对应的。

寄存器控制流程

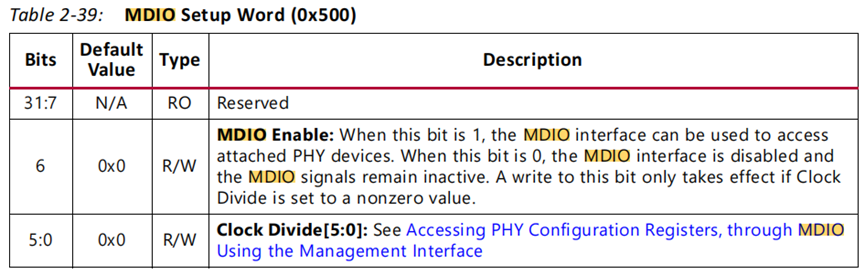

开启MDIO传输

操作phy芯片的寄存器时必须先开启MDIO传输。

|-----|------------|-----------|------------------------|

| 开启MDIO传输 ||||

| w/r | axi_awaddr | axi_wdata | description |

| w | 0x500 | 0x58 | [6]bit 打开MDIO_ENABLE |

写0x1E寄存器

给0x1E寄存器写入0xA003表示我们要操作的扩展寄存器是EXT_A003.

|-----|------------|-------------|-------------------------------|

| 给0x1E寄存器写0xA003 ||||

| w/r | axi_awaddr | axi_wdata | description |

| w | 0x508 | 0xA003 | 需要写的数据是0xA003 |

| w | 0x504 | 0x001E_4800 | 1.[11]bit 开启传输 |

| w | 0x504 | 0x001E_4800 | 2.[15:14]bit是2'b01开启写流程 |

| w | 0x504 | 0x001E_4800 | 3.[20:16]bit TX_REGAD 是0x1E |

| w | 0x504 | 0x001E_4800 | 4.[28:24]bit phy地址是0x0 |

写0x1F寄存器

0x1E寄存器指代要操作的扩展寄存器,0x1F指代给给0x1E指定的扩展寄存器写的值。

给0x1F寄存器写入0x10F1表示,我们要给EXT_A003寄存器写0x10F1.

|-----|------------|-------------|-------------------------------|

| 给0x1F寄存器写0x10F1 ||||

| w/r | axi_awaddr | axi_wdata | description |

| w | 0x508 | 0x10F1 | 需要写的数据是0x10F1 |

| w | 0x504 | 0x001F_4800 | 1.[11]bit 开启传输 |

| w | 0x504 | 0x001F_4800 | 2.[15:14]bit是2'b01开启写流程 |

| w | 0x504 | 0x001F_4800 | 3.[20:16]bit TX_REGAD 是0x1F |

| w | 0x504 | 0x001F_4800 | 4.[28:24]bit phy地址是0x0 |

通过以上开启MDIO传输,写0x1E和写0x1F寄存器,就可以修改RX_DELAY_SEL的值了。

读寄存器流程

写寄存器和读寄存器都要先开启MDIO的控制传输,此处不再赘叙。

以读0x1E地址的数据为例,说明下读寄存器的命令。

先发送axi写数据,给0x504寄存器写入0x001E_8800,表明要读取0x1E地址的数据。而后通过读取0x50C寄存器获取数据。

|-----|----------|-------------|-------------------------------|

| 读取0x1E寄存器的值 ||||

| w/r | axi_addr | axi_wdata | description |

| w | 0x504 | 0x001E_8800 | 1.[11]bit 开启传输 |

| w | 0x504 | 0x001E_8800 | 2.[15:14]bit是2'b10开启读流程 |

| w | 0x504 | 0x001E_8800 | 3.[20:16]bit TX_REGAD 是0x1E |

| w | 0x504 | 0x001E_8800 | 4.[28:24]bit phy地址是0x0 |

| r | 0x50c | | 读取0x50c获取到TX_REGAD寄存器返回的值 |

参考文档

- PG051-tri-mode-eth-mac-en-us-9.0

- 以太网收发器_YT8531SH

公司简介

成都优数科技有限公司成立于2016年9月,是一家提供高性能、通用规范的国产化高速数据采集、数据存储、信号处理产品的技术型服务商,应用于科学研究、医疗测控、通信雷达、电磁场构建等领域,方便用户二次开发。

公司产品适合ODM,面向工业级以上质量要求的用户,具有通用性强、高性能指标、稳定可靠、可维护性好、性价比高等特点。