相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

SDC相关运行时间问题的报告

SDC约束的复杂性、过多的时序路径等因素可能导致综合工具运行时间过长,在早期版本中,综合工具不会提供反馈来帮助识别这些潜在原因,从2018版本开始,Design Compiler会提供关于SDC约束复杂性的反馈信息。

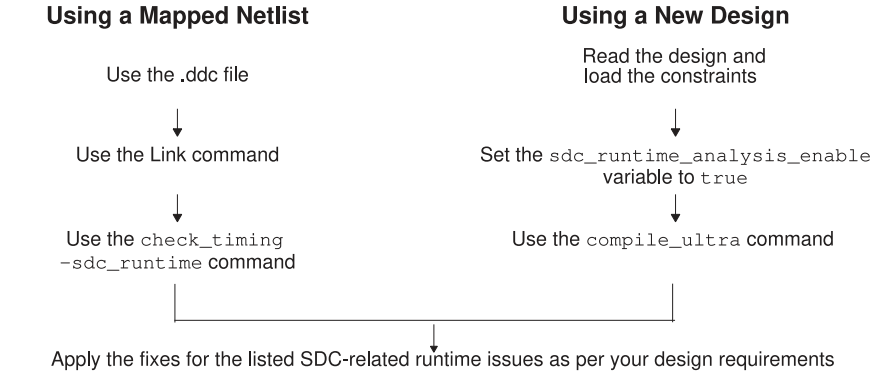

有两种方法可以启用该功能,设置sdc_runtime_analysis_enable变量后进行综合或者使用check_timing -sdc_runtime命令,如图1所示。前者适合新设计,由于进行了优化因此运行时间较长,后者适合已综合的设计,只会进行报告因此运行时间较短。

图1 解决SDC相关运行时间问题的流程

可以通过sdc_runtime_analysis_log_file变量设置报告保存的文件,如果将其设置为空则输出至标准输出,默认情况下报告保存在sdc_runtime_<timestamp>.log文件中。

下面将列举一些报告中会出现的TIM信息。

TIM-601

设计中有些时钟并未被实际使用,但仍然存在于数据库中,这会成为综合工具额外运行时间的来源,当设计中的未使用时钟数量超过sdc_runtime_unused_clocks_threshold变量(默认值为5)时,将会产生TIM-601信息。

TIM-602

对严格约束的时序组进行优化通常会导致综合工具运行时间变长。

TIM-603

TIM-604

当设计中存在不可行路径时,将会产生TIM-604信息。

TIM-605

多时钟交互(多个时钟到达同一个触发器的时钟引脚)可能导致运行时间显著上升,TIM-605信息表示没有遗漏的跨时钟域约束,默认情况下只会产生TIM-099信息。

设置timing_enable_multiple_clocks_per_reg变量也可以解决这个问题,但更建议使用显式约束。

TIM-606

如果设计中存在高扇出线网(由sdc_runtime_nets_missing_exceptions_fanout_threshold变量控制,默认值为500),且这些网络未使用set_ideal_network和set_dont_touch_network等命令约束,综合时对这些线网进行缓冲可能会增加运行时间,TIM-606信息将列出此类线网(数量由sdc_runtime_top_fanout_nets_missing_exceptions变量控制,默认值为100)。

TIM-607

当输入/输出端口被大量时钟约束时(由sdc_runtime_port_clock_constraint_threshold变量控制,默认值为20),综合工具为了优化会增加运行时间,将会产生TIM-607信息。

TIM-608

如果设计中出现很高的WNS,可能的原因之一就是缺少多周期(set_multicycle_path)或虚假路径约束(set_fasle_path),在这种情况下优化设计可能会增加运行时间,将会产生TIM-608信息,每个时序组报告的路径数量由sdc_runtime_paths_missing_inter_clock_constraints变量(默认值为5)控制。

TIM-609

当大量时序弧穿过ETM(extracted timing model)或BAM(block abstraction model)层次模块引脚时,会导致运行时间变长,当某个层级引脚承载超过一定数量(由sdc_runtime_hier_block_pins_timing_path_threshold变量控制,默认值为500)的时序路径时,将会产生TIM-609信息,报告的引脚数量由sdc_runtime_hier_block_pins_top_timing_paths变量控制,默认值为100。

TIM-610

约束可能被施加在实际上不存在的时序路径上,这会导致综合工具运行时间变长,将会产生TIM-610信息(使用report_timing_requirements -ignored命令也是一种解决方案)。

TIM-612

当大量周期和波形相同的时钟到达同一个时钟引脚,综合工具在优化时会将这些时钟逐一考虑,导致运行时间显著增加,将会产生TIM-612信息。

TIM-613

多时钟交互(多个时钟到达同一个触发器的时钟引脚)可能导致运行时间显著上升,TIM-613信息表示部分遗漏了跨时钟域约束,默认情况下只会产生TIM-099信息。

设置timing_enable_multiple_clocks_per_reg变量也可以解决这个问题,但更建议使用显式约束。

TIM-614

多时钟交互(多个时钟到达同一个触发器的时钟引脚)可能导致运行时间显著上升,TIM-614信息表示遗漏了全部跨时钟域约束,默认情况下只会产生TIM-099信息。

设置timing_enable_multiple_clocks_per_reg变量也可以解决这个问题,但更建议使用显式约束。

TIM-615、TIM-616、TIM-617

这三个信息类似TIM-605、TIM-613、TIM-614,也是由于跨时钟路径缺少约束导致的。

SDC相关运行时间问题的修复

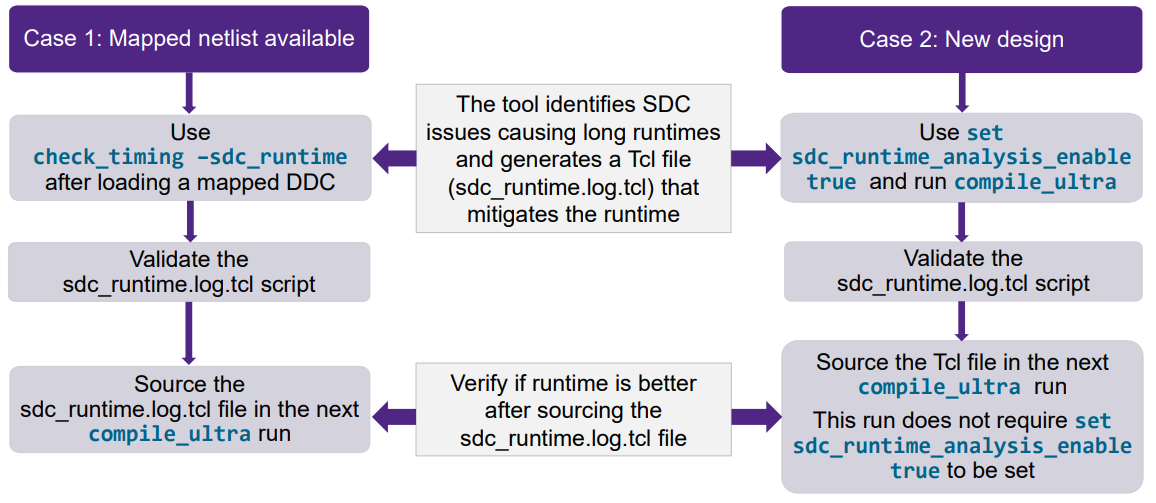

从Design Compiler NXT 2019版本开始,综合工具会在报告SDC相关运行时间问题的同时,自动生成包含推荐修复方案的Tcl文件,文件名为<报告名>.tcl,表1列出了针对各种信息,Tcl文件中推荐的修复措施。

表1 信息及对应修复措施

|--------------------------------------------------|--------------------------------------------------|

| 信息 | 修复措施 |

| TIM-601 | 使用remove_clock命令移除未使用的时钟 |

| TIM-602、TIM-608 | 使用set_multicycle_path命令设置多周期路径 |

| TIM-604 | 使用set_false_path命令设置虚假路径 |

| TIM-606 | 使用set_ideal_network命令设置理想网络 |

| TIM-607 | 使用remove_input_delay或remove_output_delay命令移除端口约束 |

| TIM-609、TIM-610 | 使用reset_path命令移除约束 |

| TIM-612 | 使用set_clock_sense -stop_propagation命令阻止时钟传播 |

| TIM-605、TIM-613、TIM-614、 TIM-615、TIM-616、TIM-617 | 使用set_clock_groups命令创建时钟组 |

图2展示了修复SDC相关运行时间问题的流程。

图2 修复SDC相关运行时间问题的流程

综合过程中,由于解组等原因,生成的Tcl文件可能包含修改后的名称,将enable_rule_based_query变量设置为true可以解决这个问题;另外,线网也可能会被重命名,如果这些线网在Tcl文件中被TIM-606信息作为高扇出线网报告,应检查该信息,并将set_ideal_network命令应用到原始线网名上。

自动修复

Design Compiler NXT 2019版本支持在综合时自动修复检测到的SDC相关运行时间问题,自动修复内容与生成的Tcl文件中的修复内容相同,这有助于评估在下一次工具运行中应用Tcl文件修复的收益,该功能默认开启,如果将sdc_runtime_fixing_enable变量设置为false则可以关闭自动修复。

Information: The "sdc_runtime_fixing_enable" variable is enabled. SDC changes can cause QoR changes. (TIM-619)