相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

写在开始

关于Multibit优化的简介和RTL向量自动推断流程、手动创建多比特组件流程,已经在之前的文章中讨论,本文将不再赘述,具体内容可以参考下面的博客,建议在阅读本文前先学习该文章。

Design Compiler:Multibit优化(RTL向量自动推断流程和手动创建多比特组件流程)![]() https://chenzhang.blog.csdn.net/article/details/155949999 关于布局感知的Multibit Banking流程,已经在之前的文章中讨论,本文将不再赘述,具体内容可以参考下面的博客,建议在阅读本文前先学习该文章。

https://chenzhang.blog.csdn.net/article/details/155949999 关于布局感知的Multibit Banking流程,已经在之前的文章中讨论,本文将不再赘述,具体内容可以参考下面的博客,建议在阅读本文前先学习该文章。

增强型布局感知的Multibit Banking流程

拓扑模式的Design Compiler NXT在2021版本推出了增强型布局感知的Multibit Banking流程,可以在综合过程中就进行布局感知的Multibit优化,在进行增量综合前就获得较好的结果质量(QoR)。

该流程分为两种,一种是单独的增强型布局感知的Multibit Banking流程,一种是集成的增强型布局感知的Multibit Banking流程(需要使用compile_ultra -spg命令)。

多比特单元替换后,report_multibit命令可用于报告设计中的多比特组件或为寄存器组的实现情况,它们被命名为 mbm_seg_*cluster*,以表明其实际上是由增强型布局感知的Multibit Banking流程得到的。

单独的增强型布局感知的Multibit Banking流程

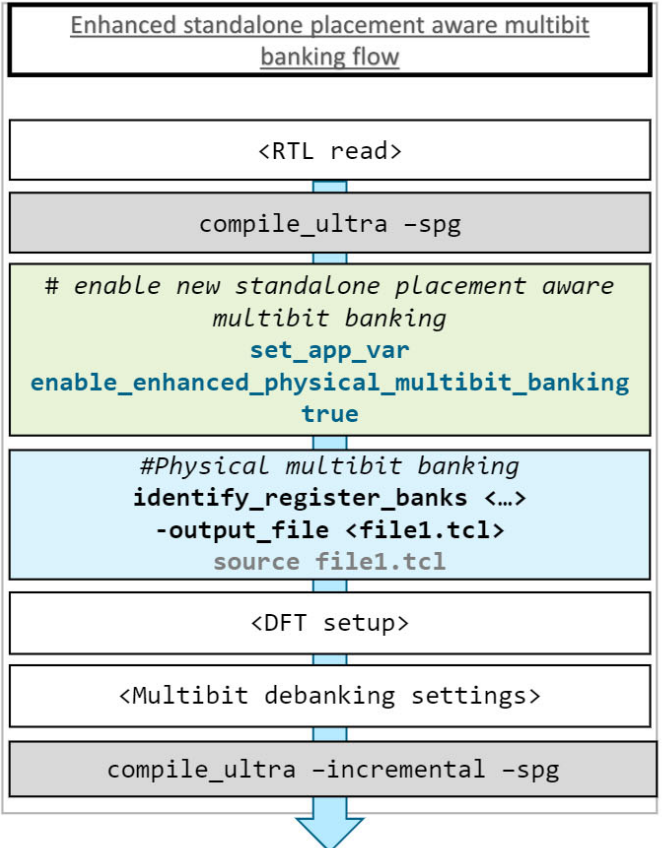

图1展示单独的增强型布局感知的Multibit Banking流程。

图1 单独的增强型布局感知的Multibit Banking流程

用户首先需要将enable_enhanced_physical_multibit_banking变量设置为true(默认值为false),与布局感知的Multibit Banking流程不同的是,此时identify_register_banks命令会识别物理位置上彼此接近、且相互兼容的单比特单元并直接将其合并,并不会生成包含create_register_bank命令的Tcl脚本,也无需指定-output_file选项(如果依旧指定,则会产生一个包含以下内容的文件)。

# The netlist transformations were applied by identify_register_banks需要注意的是,此时不能使用-input_map_file、-register_group_file选项,即该流程不能指定输入映射文件和寄存器分组文件。

identify_register_banks命令的其余部分与布局感知的Multibit Banking流程类似,在此不再赘述。

集成的增强型布局感知的Multibit Banking流程

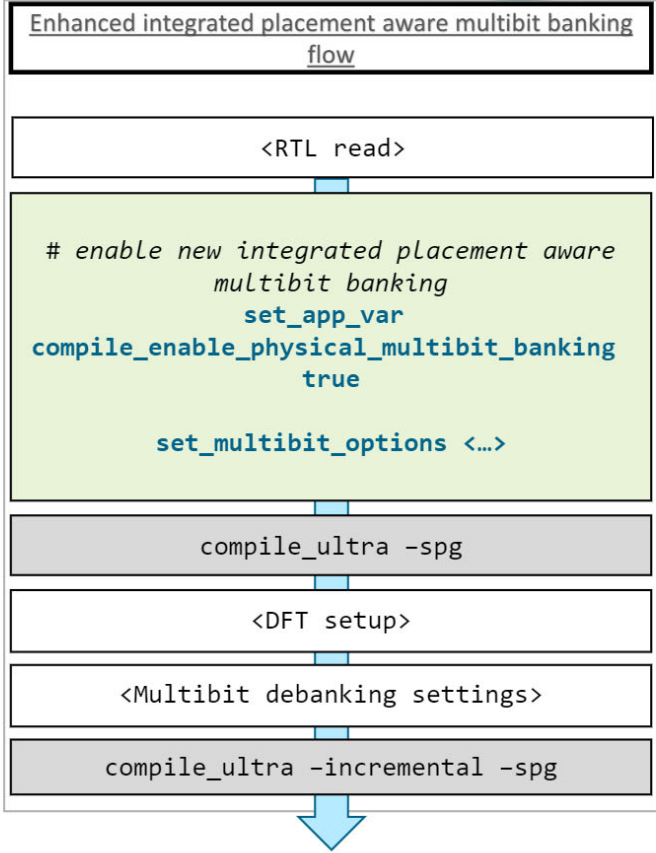

图2展示集成的增强型布局感知的Multibit Banking流程。

图2 集成的增强型布局感知的Multibit Banking流程

用户首先需要将compile_enable_physical_multibit_banking变量设置为true(默认值为false),综合工具会在综合过程中(需要使用compile_ultra -spg命令)先后进行RTL级Multibit优化(类似RTL向量自动推断流程和手动创建多比特组件流程)和物理级Multibit优化(类似布局感知的Multibit流程),与单独的identify_register_banks命令相比,可能获得更好的结果质量(QoR)。

多比特单元命名规则

增强型布局感知的Multibit Banking流程中,多比特单元的命名规则与RTL向量自动推断流程和手动创建多比特组件流程相同。

set_multibit_options命令

set_multibit_options命令的BNF范式(有关BNF范式,可以参考以往文章)为:

set_multibit_options

[-default]

[-stage rtl | physical | debanking | banking_all | none]

[-mode non_timing_driven | timing_driven | timing_friendly | none]

[-critical_range range | -slack_threshold percentage] [-path_groups list_of_pathgoups]

[-exclude_registers_with_timing_exceptions true|false] [-ignore_timing_exceptions list_of_timing_exceptions_to_not_exclude]

[-exclude cells_to_exclude]

[-name_prefix prefix_for_created_mb_cells]

[-multibit_components_only]

//注:该命令的选项和参数顺序任意该命令可以控制增强型布局感知的Multibit Banking流程(尽管图1中并没有显式标出,但该命令可以控制单独的增强型布局感知的Multibit Banking流程)。

其中-stage选项的参数可以是四种之一:rtl(其他选项应用于RTL级Multibit优化)、physical(其他选项应用于物理级Multibit优化)、banking_all(其他选项同时应用于RTL级Multibit优化和物理级Multibit优化,如无特殊需求,可指定该参数)、debanking(其他选项应用于时序感知的Multibit增量综合拆分流程)。

-mode选项的参数可以是四种之一:non_timing_driven(默认,综合工具会在所有可能的地方使用多比特单元,最大化多比特单元替换比例,使剩余的单比特单元数量最少,允许时序和面积变差)、timing_friendly(综合工具的多比特推断力度与non_timing_driven类似,但在选择目标多比特单元时以时序为优先,有助于改善时序,但在Multibit优化过程中仍可能导致时序变差)、timing_driven(综合工具仅在不恶化时序的前提下,才将单比特单元替换为多比特单元,对时序最保守)、none(该参数在增强型布局感知的Multibit Banking流程中失效)。

默认情况下,如果某个单比特单元在共享引脚(时钟引脚、控制引脚)上设置了时序例外(如虚假路径、多周期路径),则需要同组的其他单比特单元也是如此;如果某个单比特单元在非共享引脚上设置了时序例外(如虚假路径、多周期路径),综合工具可以将时序例外转移到多比特单元上。如果使用了set_multibit_options命令的-exclude_registers_with_timing_exceptions选项,则不允许单比特单元设置时序例外;-ignore_timing_exceptions选项用于在使用-exclude_registers_with_timing_exceptions选项的基础上允许部分时序例外,支持group_path、false_path、multicycle_path、max_delay、min_delay。

该命令的-exclude选项、-name_prefix选项、-multibit_components_only选项与identify_register_banks命令的同名选项功能相同。如果在单独的增强型布局感知的Multibit Banking流程中同时使用set_multibit_options命令与identify_register_banks命令的同名选项:-exclude选项叠加,identify_register_banks命令的-name_prefix选项优先,-multibit_components_only选项指定一次即生效。

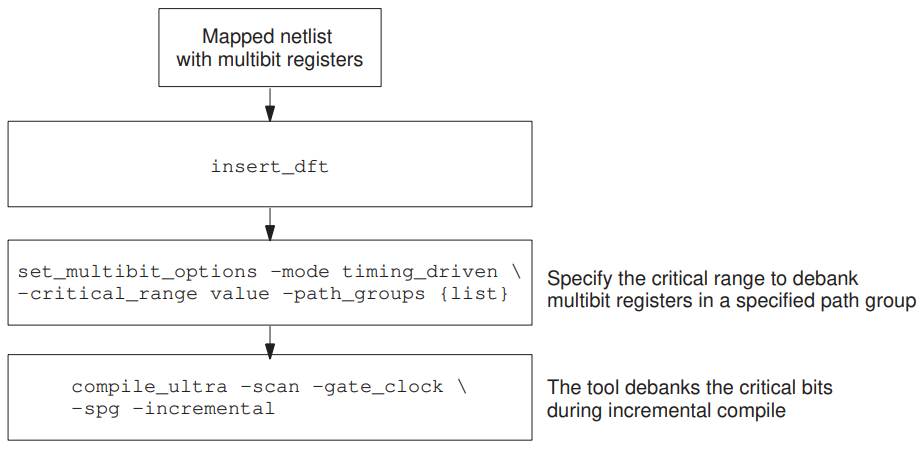

-critical_range选项和-path_groups选项可以开启时序感知的Multibit增量综合拆分流程,图3展示了时序感知的Multibit增量综合拆分流程。

图3 时序感知的Multibit增量综合拆分

将单比特单元替换为多比特单元有时会影响设计的时序结果质量(QoR)。相反,将关键路径上的多比特单元拆分为单比特单元,则可以改善时序结果质量(QoR)。

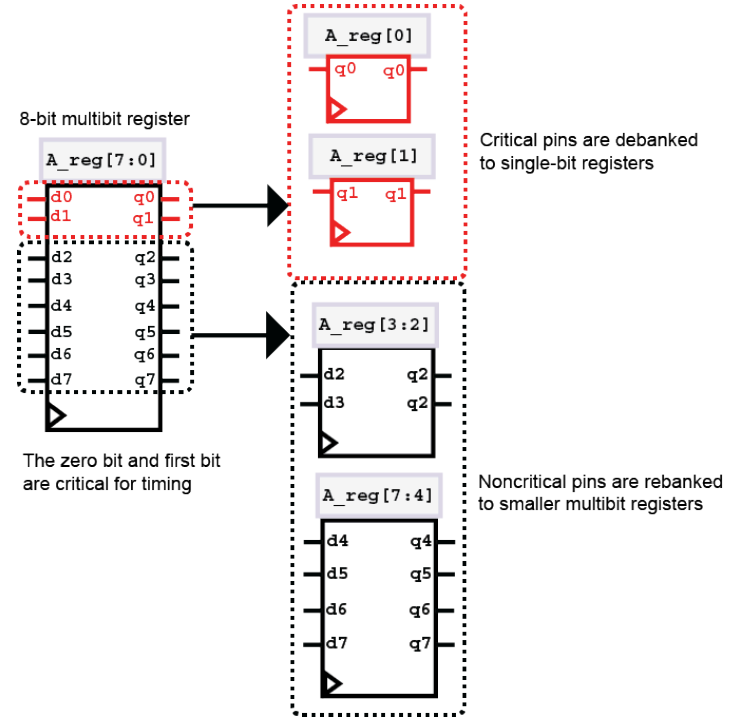

综合工具可以在增量综合(需要使用compile_ultra -spg -incr命令)过程中识别多比特单元中的关键比特并将其拆分成单比特单元,并将非关键比特重新合并成更小位宽的多比特单元,如图4所示。需要注意的是,综合工具仅在这种操作能够改善时序的情况下才会拆分,并尽量保持设计中的单元为多比特形式。

图4 多比特单元拆分

-critical_range选项用于指定关键范围,是一个相对关键路径(Worst Negative Slack, WNS)的范围,它可以是一个非负数、一个百分数(数值后添加%)、0(表示仅关键路径)、default(表示综合工具会根据优化时的设计状态,为每个时序组确定合适的关键范围)、full(表示所有裕量为负的路径)。-slack_threshold percentage选项相当于百分数形式的-critical_range选项,不可一起使用。-path_groups选项用于将关键范围的影响限制在某些时序组中,默认情况下关键范围针对整个设计。需要注意的是,只有未使用-stage选项或使用-stage debanking选项时,时序感知的Multibit增量综合拆分才生效。

例如,下面的命令设置时序组CLK的关键范围为2.0。

dcnxt_shell-topo> set_multibit_options -mode timing_driven -critical_range 2.0 -path_groups {CLK}如果该时序组的WNS为-3.0,则在增量综合过程中,综合工具会尝试拆分裕量位于-3.0到-1.0之间的次关键路径上的多比特单元。

被拆分后的单比特单元的命名方式与split_register_bank命令相同。

在多比特库单元有限时提升分组比例

综合时的Multibit优化分两步完成,第一步是将通用时序单元SEQGEN映射为单比特单元(默认情况下,这一步与Multibit优化无关,即不要求库中存在与单比特单元功能等价的多比特单元),随后再尝试进行多比特单元替换。

当库中的多比特单元种类较少时,可能会造成分组比例较低,此时将seqmap_prefer_registers_with_multibit_equivalent变量(默认值为false)设置为true,这样综合工具在映射通用时序单元时会尽可能选择那些有功能等价多比特单元的单比特单元,从而提高分组比例。

报告Multibit优化结果

可以使用report_multibit_banking命令报告设计中的多比特单元数量和比例,如下所示。

dcnxt_shell-topo> report_multibit_banking

****************************************

Report : multibit banking

Design : mul

Version: W-2024.09-SP2

Date : Fri Dec 26 17:15:32 2025

****************************************

Total number of sequential cells: 74

(a) Number of single-bit flip-flops: 13

(b) Number of single-bit latches: 0

(c) Number of multi-bit flip-flops: 61

(d) Number of multi-bit latches: 0

Total number of single-bit equivalent sequential cells: 257

(A) Single-bit flip-flops: 13

(B) Single-bit latches: 0

(C) Multi-bit flip-flops: 244

(D) Multi-bit latches: 0

Sequential cells banking ratio ((C + D) / (A + B + C + D)): 94.94%

Flip-Flop cells banking ratio ((C) / (A + C)): 94.94%

Sequential bits per cell ((A + B + C + D) / (a + b + c + d)): 3.47

Flip-Flop bits per cell ((A + C) / (a + c)): 3.47

Multi-bit Register Decomposition:

--------------------------------------------------------------------------------

Bit-Width Reference Number of instances Single-bit Equivalent

--------------------------------------------------------------------------------

4-bits 61 ( 82.43%) 244 ( 94.94%)

SAEDHVT14_LSRDPQ4_1 61

--------------------------------------------------------------------------------