相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

Multibit Banking简介

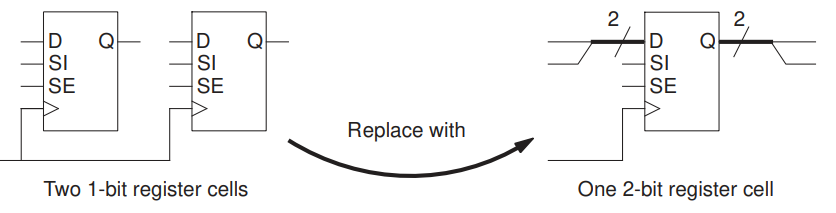

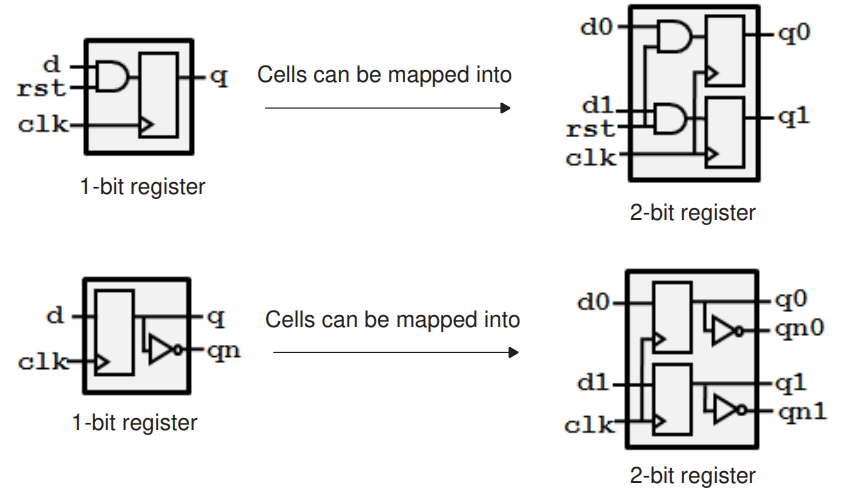

综合(例如Design Compiler)与物理实现(例如IC Compier II)工具可以在将多个单比特触发器组织为多比特触发器,例如八个单比特触发器可以改用一个八比特触发器或两个四比特触发器实现,这个优化过程被称为Multibit Banking,图1展示了一个具体案例。

图1 用一个多比特触发器替换多个单比特触发器

用多比特触发器替换单比特触发器具有以下优点:

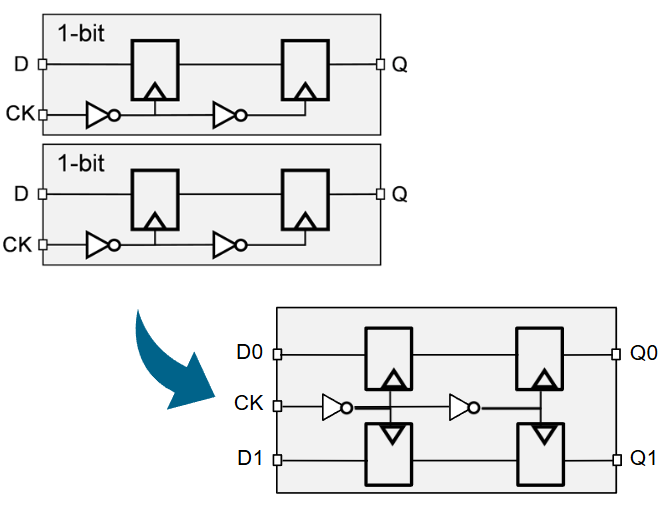

- 由于晶体管共享和晶体管级版图优化,触发器的总面积和总内部功耗降低,如图2所示。

图2 总面积和总内部功耗降低

- 时钟树网络总长度和时钟树缓冲器数量减少,时钟树的翻转功耗降低,如图3所示。

图3 时钟树的翻转功耗降低

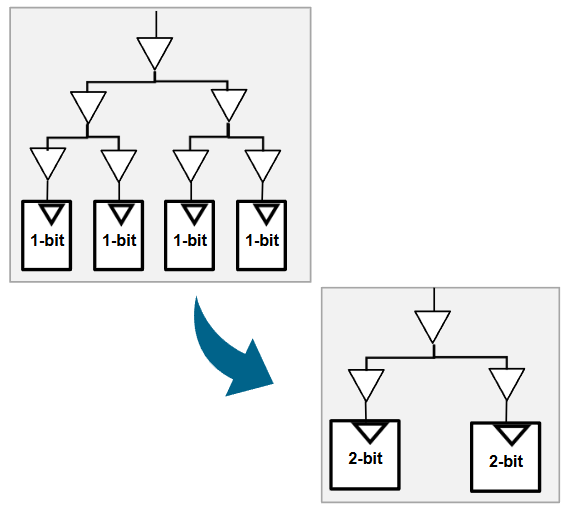

对于可测试性设计,多比特扫描触发器可以在内部直接串接成一条扫描链,也可以为每一比特提供独立的扫描输入和扫描输出,如图4所示。

图4 多比特扫描触发器的映射

Multibit Banking的库要求

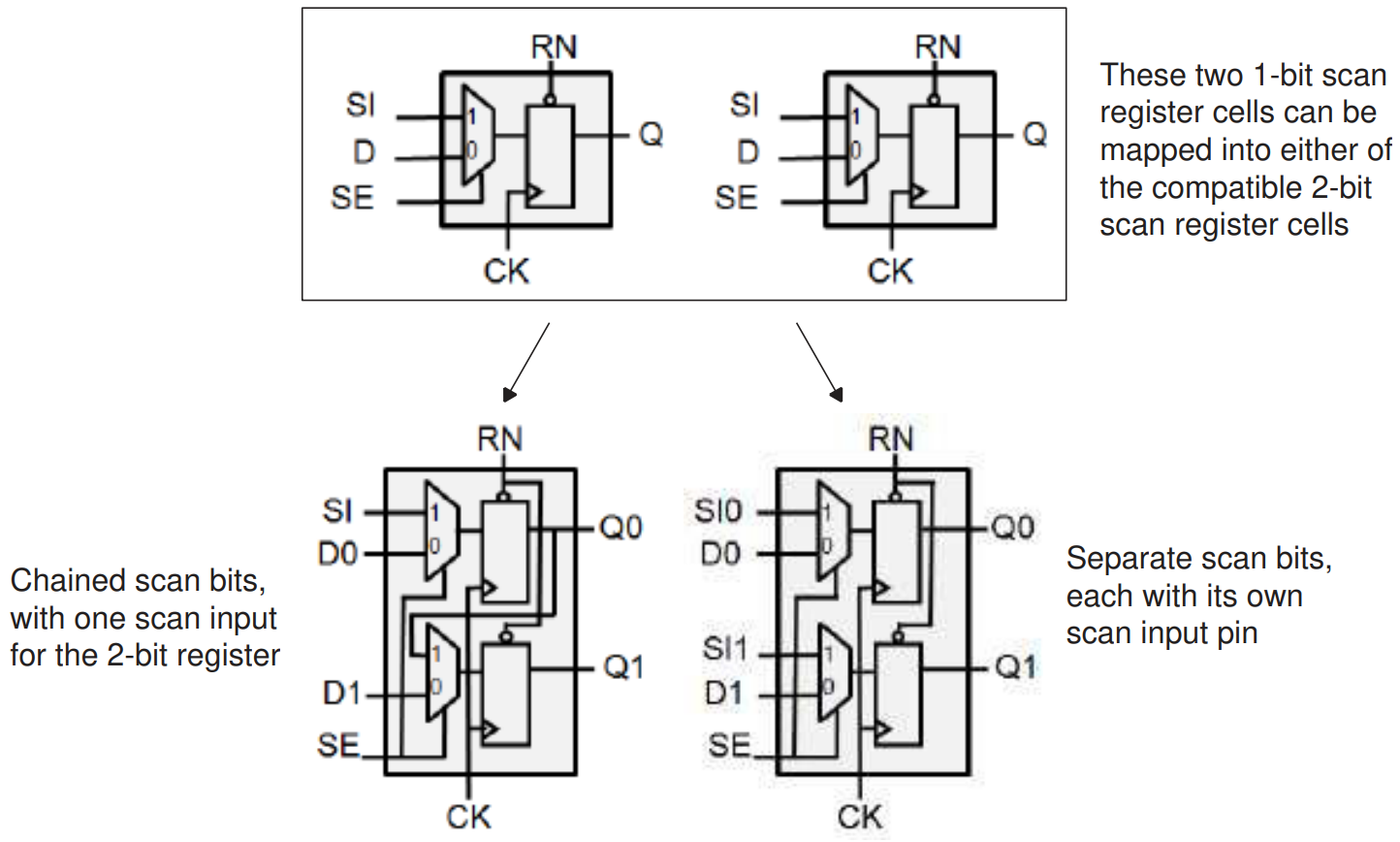

为了执行从单比特触发器到多比特触发器的映射,Design Compiler会检查多比特触发器引脚的功能是否匹配,如图5所示。

图5 具有相同引脚功能的单比特触发器到多比特触发器的映射

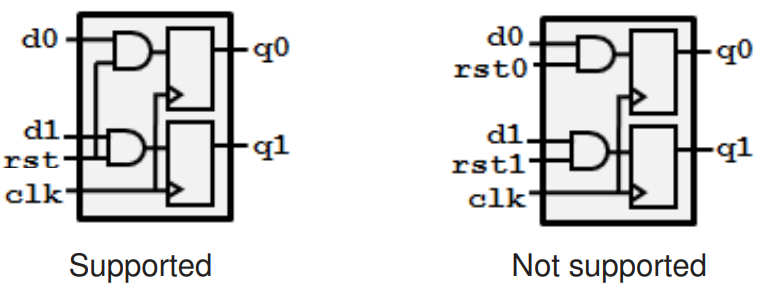

如果一个单比特触发器具有Q和QN输出,Design Compiler只能使用同样在每个输出比特上都提供Q和QN输出的多比特触发器来替换该单比特触发器。需要注意的是,引脚的名字并不影响单比特触发器和多比特触发器的匹配,且工具不支持为单个比特提供独立控制引脚的多比特触发器,如图6所示。

图6 为单个比特提供独立控制引脚的多比特触发器不被支持

在Liberty语法(.lib库)中,cell或test_cell组中的ff_bank、latch_bank或statetable组可以用于描述由多个并行的单比特时序单元组成的多比特时序单元,这些时序单元的各个比特共享控制信号,并执行完全相同的功能。

RTL向量自动推断流程

在RTL向量自动推断流程中,Design Compiler会根据RTL中定义的向量来推断多比特触发器,并将它们分组为一个多比特组件(Multibit Component)。多比特组件是一组被标记为可使用一个或多个多比特触发器进行实现的单比特触发器集合,在综合过程中单比特单元才会被真正替换为多比特单元。

hdlin_infer_multibit变量用于控制HDL Compiler(它是一个内置于Design Compiler的工具,用于将RTL描述转换为GTECH格式)在读取RTL时如何进行向量推断,并配合综合指令infer_multibit和dont_infer_multibit一起使用。

当hdlin_infer_multibit变量设置为never时,HDL Compiler不会进行任何多比特触发器推断;当hdlin_infer_multibit变量设置为default_none(默认值)时,HDL Compiler只在用户在RTL中使用infer_multibit指令时推断多比特触发器;当hdlin_infer_multibit变量设置为default_all时,HDL Compiler会从所有向量中推断多比特触发器,除非用户在RTL中使用infer_multibit指令禁止。

例1展示了默认情况下,在RTL中使用infer_multibit指令以指定推断多比特触发器。

// 例1

module test (d0, d1, rst, clk, q0, q1);

parameter d_width = 8;

input [d_width-1:0] d0, d1;

input clk, rst;

output reg [d_width-1:0] q0, q1;

//synopsys infer_multibit "q0"

always @(posedge clk) begin

if (!rst) q0 <= 0;

else q0 <= d0;

end

always @(posedge clk or negedge rst) begin

if (!rst) q1 <= 0;

else q1 <= d1;

end

endmodule读取设计的结果如下所示,其中q0_reg的MB字段为Y,表明其被推断为多比特触发器,而q1_reg则没有。

==================================================================================

| Register Name | Type | Width | Bus | MB | Set | Reset | ST | Line |

==================================================================================

| q0_reg | Flip-flop | 8 | Y | Y | None | None | N | 8 |

| q1_reg | Flip-flop | 8 | Y | N | None | Async | N | 13 |

==================================================================================综合前使用report_multibit命令可以报告设计中的多比特组件以及其中包含的单元,如下所示。

dcnxt_shell> report_multibit

****************************************

Report : multibit

Design : test

Version: W-2024.09-SP2

Date : Wed Dec 17 22:22:24 2025

****************************************

Attributes:

b - black box (unknown)

h - hierarchical

n - noncombinational

r - removable

u - contains unmapped logic

Multibit Component : q0_reg

Cell Reference Library Area Width Attributes

--------------------------------------------------------------------------------

q0_reg[7] **SEQGEN** 0.00 1 n, u

q0_reg[6] **SEQGEN** 0.00 1 n, u

q0_reg[5] **SEQGEN** 0.00 1 n, u

q0_reg[4] **SEQGEN** 0.00 1 n, u

q0_reg[3] **SEQGEN** 0.00 1 n, u

q0_reg[2] **SEQGEN** 0.00 1 n, u

q0_reg[1] **SEQGEN** 0.00 1 n, u

q0_reg[0] **SEQGEN** 0.00 1 n, u

--------------------------------------------------------------------------------

Total 8 cells 0.00 8

Total 1 Multibit Components多比特组件q0_reg包含了8个单比特通用时序单元SEQGEN(或者称为Generic/Unmapped Sequential Cell),Design Compiler在综合时将考虑将这8个未映射的时序单元映射为多比特触发器。

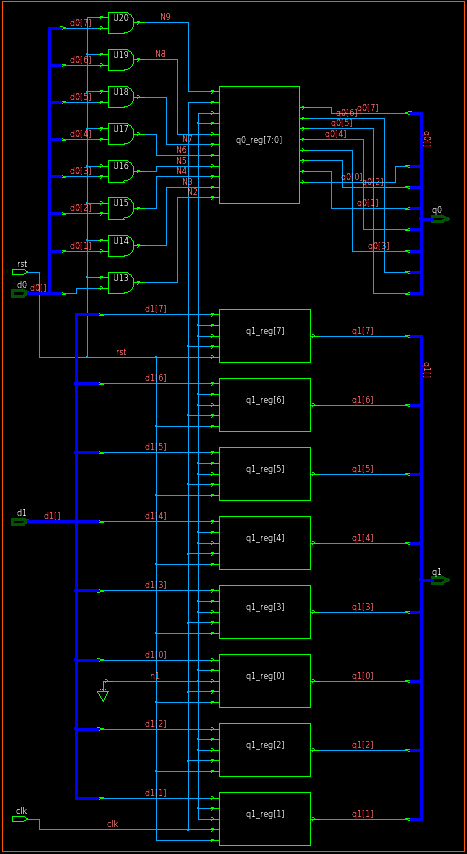

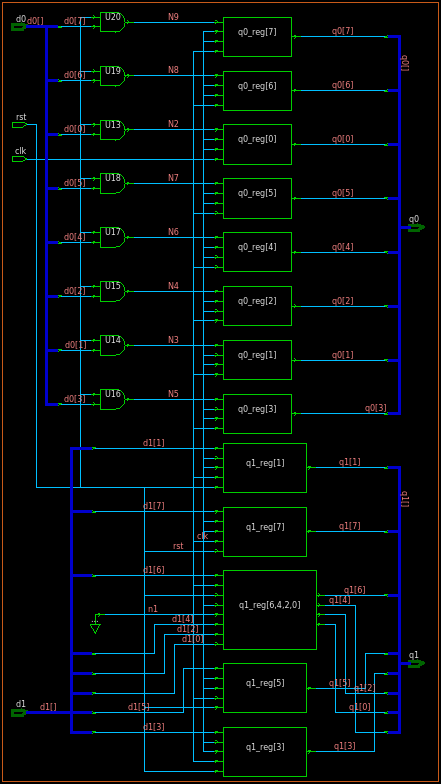

需要注意的是,由于我使用的库只包含多比特扫描触发器,所以需要使用compile_ultra -scan命令进行综合,例1的综合结果如图7所示。

图7 例1的综合结果

综合后再使用report_multibit命令可以报告设计中的多比特组件的实现情况,如下所示。

dcnxt_shell> report_multibit

****************************************

Report : multibit

Design : test

Version: W-2024.09-SP2

Date : Wed Dec 17 22:43:01 2025

****************************************

Attributes:

b - black box (unknown)

h - hierarchical

n - noncombinational

r - removable

u - contains unmapped logic

Multibit Component : q0_reg

Cell Reference Library Area Width Attributes

--------------------------------------------------------------------------------

q0_reg[7:0] MB8SRLSDFQD1BWP7T35P140

tcbn28hpcplusbwp7t35p140mbffg0p88v0c

14.90 8 n, r

--------------------------------------------------------------------------------

Total 1 cells 14.90 8

Total 1 Multibit Components需要注意的是,多比特组件并不能保证映射为多比特触发器,例2展示了一个映射失败的情况。

// 例2

module test (d0, d1, rst, clk1, clk2, q0, q1);

parameter d_width = 8;

input [d_width-1:0] d0, d1;

input clk1, clk2, rst;

output reg [d_width-1:0] q0, q1;

//synopsys infer_multibit "q0"

always @(posedge clk1) begin

if (!rst) q0[6:0] <= 0;

else q0[6:0] <= d0[6:0];

end

always @(posedge clk2) begin

if (!rst) q0[7] <= 0;

else q0[7] <= d0[7];

end

always @(posedge clk1 or negedge rst) begin

if (!rst) q1 <= 0;

else q1 <= d1;

end

endmodule此时读取设计的结果如下所示,其中q0_reg被分为了两部分,它们的MB字段都为Y。

==================================================================================

| Register Name | Type | Width | Bus | MB | Set | Reset | ST | Line |

==================================================================================

| q0_reg | Flip-flop | 7 | Y | Y | None | None | N | 8 |

| q0_reg | Flip-flop | 1 | N | Y | None | None | N | 13 |

| q1_reg | Flip-flop | 8 | Y | N | None | Async | N | 18 |

==================================================================================综合前report_multibit命令的结果如下所示。

dcnxt_shell> report_multibit

****************************************

Report : multibit

Design : test

Version: W-2024.09-SP2

Date : Thu Dec 18 15:59:51 2025

****************************************

Attributes:

b - black box (unknown)

h - hierarchical

n - noncombinational

r - removable

u - contains unmapped logic

Multibit Component : q0_reg

Cell Reference Library Area Width Attributes

--------------------------------------------------------------------------------

q0_reg[6] **SEQGEN** 0.00 1 n, u

q0_reg[5] **SEQGEN** 0.00 1 n, u

q0_reg[4] **SEQGEN** 0.00 1 n, u

q0_reg[3] **SEQGEN** 0.00 1 n, u

q0_reg[2] **SEQGEN** 0.00 1 n, u

q0_reg[1] **SEQGEN** 0.00 1 n, u

q0_reg[0] **SEQGEN** 0.00 1 n, u

q0_reg[7] **SEQGEN** 0.00 1 n, u

--------------------------------------------------------------------------------

Total 8 cells 0.00 8

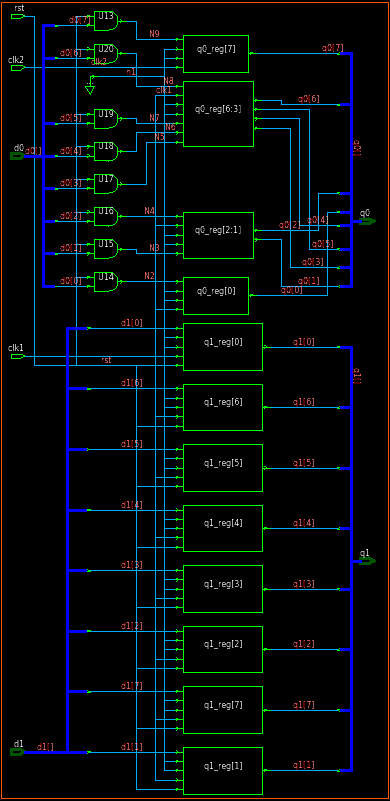

Total 1 Multibit Components例2的综合结果如图8所示。

图8 例2的综合结果

从图8中可以看出,q0_reg[6:3]和q0_reg[2:0]映射为多比特触发器,而q0_reg[0]和q0_reg[7]则映射为单比特触发器,这是因为库中提供的多比特触发器只有八、四、二这三种位宽,综合后report_multibit命令的报告中还列出了部分比特映射失败的原因。

dcnxt_shell> report_multibit

****************************************

Report : multibit

Design : test

Version: W-2024.09-SP2

Date : Thu Dec 18 00:11:17 2025

****************************************

Attributes:

b - black box (unknown)

h - hierarchical

n - noncombinational

r - removable

r14 - register coultn't be packed to multi-bit due to a conflicting pin connection.

r15 - register couldn't be grouped with others for multi-bit packing.

r18 - register is a single-bit cell that was left over from a multi-bit packing solution.

u - contains unmapped logic

Multibit Component : q0_reg

Cell Reference Library Area Width Attributes

--------------------------------------------------------------------------------

q0_reg[6:3] MB4SRLSDFQD1BWP7T35P140

tcbn28hpcplusbwp7t35p140mbffg0p88v0c

7.64 4 n, r

q0_reg[2:1] MB2SRLSDFQD1BWP7T35P140

tcbn28hpcplusbwp7t35p140mbffg0p88v0c

4.12 2 n, r

q0_reg[0] SDFQOPTAD1BWP7T40P140

tcbn28hpcplusbwp7t40p140ffg0p88v0c

2.25 1 n, r18

q0_reg[7] SDFQOPTAD1BWP7T40P140

tcbn28hpcplusbwp7t40p140ffg0p88v0c

2.25 1 n, r14, r15

--------------------------------------------------------------------------------

Total 4 cells 16.27 8

Total 1 Multibit Components手动创建多比特组件流程

用户还可以在读取RTL后使用create_multibit命令显式创建多比特组件,例3展示了该命令的使用方法。

// 例3

module test (d0, d1, rst, clk, q0, q1);

parameter d_width = 8;

input [d_width-1:0] d0, d1;

input clk, rst;

output reg [d_width-1:0] q0, q1;

always @(posedge clk) begin

if (!rst) q0 <= 0;

else q0 <= d0;

end

always @(posedge clk or negedge rst) begin

if (!rst) q1 <= 0;

else q1 <= d1;

end

endmodule

dcnxt_shell> create_multibit "q1_reg[0] q1_reg[2] q1_reg[4] q1_reg[6]"

dcnxt_shell> report_multibit

****************************************

Report : multibit

Design : test

Version: W-2024.09-SP2

Date : Thu Dec 18 16:23:31 2025

****************************************

Attributes:

b - black box (unknown)

h - hierarchical

n - noncombinational

r - removable

u - contains unmapped logic

Multibit Component : q1_reg[6]_multibit

Cell Reference Library Area Width Attributes

--------------------------------------------------------------------------------

q1_reg[6] **SEQGEN** 0.00 1 n, u

q1_reg[4] **SEQGEN** 0.00 1 n, u

q1_reg[2] **SEQGEN** 0.00 1 n, u

q1_reg[0] **SEQGEN** 0.00 1 n, u

--------------------------------------------------------------------------------

Total 4 cells 0.00 4

Total 1 Multibit Components默认情况下,create_multibit命令会按照反向字母和数字顺序来决定每一比特在多比特组件中的顺序,这会影响综合时的映射顺序。如果希望改为正向顺序,可以使用-sort选项;如果希望按照用户指定顺序,可以使用-no_sort选项。

例3的综合结果如图9所示。

图9 例3的综合结果

综合后report_multibit命令的结果如下所示。

dcnxt_shell> report_multibit

****************************************

Report : multibit

Design : test

Version: W-2024.09-SP2

Date : Thu Dec 18 16:24:59 2025

****************************************

Attributes:

b - black box (unknown)

h - hierarchical

n - noncombinational

r - removable

u - contains unmapped logic

Multibit Component : q1_reg[6]_multibit

Cell Reference Library Area Width Attributes

--------------------------------------------------------------------------------

q1_reg[6,4,2,0] MB4SRLSDFCNQD1BWP7T35P140

tcbn28hpcplusbwp7t35p140mbffg0p88v0c

8.43 4 n, r

--------------------------------------------------------------------------------

Total 1 cells 8.43 4

Total 1 Multibit Components如果用户希望保存设计中的多比特组件的信息,则可以使用write_multibit_components命令,该命令可以生成一个Tcl文件,包含create_multibit命令用于重建多比特组件。

如果用户希望移除多比特组件,则可以使用remove_multibit命令,可以指定整个多比特组件,也可以指定单独的单元。需要注意的是,如果设计已综合,移除多比特组件并不能直接将多比特触发器拆分为单比特触发器,要实现这一点,需要进行一次增量综合。

多比特触发器命名规则

在之前的例子中,综合后的多比特触发器的命名有所不同,例1综合后的多比特触发器名为q0_reg[7:0],例2综合后的多比特触发器名为q0_reg[6:3]和q0_reg[2:1],例3综合后的多比特触发器名为q1_reg[6,4,2,0]。

本节将讨论Multibit Banking过程中多比特触发器命名规则。

bus_range_separator_style(默认值为:)

该变量用于决定在实现同一向量连续位的多比特触发器命名时所使用的分隔符,例如当多比特组件中包含q0_reg[7],q0_reg[6],q0_reg[5],q0_reg[4],q0_reg[3],q0_reg[2],q0_reg[1],q0_reg[0]时(假设这也是多比特组件中的顺序),综合后的多比特触发器被命名为q0_reg[7:0]。

bus_multiple_separator_style(默认值为,)

该变量用于决定在实现同一向量非连续位的多比特触发器命名时所使用的分隔符,例如当多比特组件中包含q1_reg[6],q1_reg[4],q1_reg[2],q1_reg[0]时(假设这也是多比特组件中的顺序),综合后的多比特触发器被命名为q1_reg[6,4,2,0]。

bus_multiple_name_separator_style(默认值为,,)

该变量用于决定在实现不同向量的位多比特触发器命名时所使用的分隔符,例如当多比特组件中包含q0_reg[0],q1_reg[1]时(假设这也是多比特组件中的顺序),综合后的多比特触发器被命名为q1_reg[1],,q0_reg[0]。

需要注意的是,如果情况复杂会出现三种变量都使用到的情况,比如多比特触发器的名字为q1_reg[4:3,1],,q0_reg[0],对应的多比特组件中包含了q0_reg[0],q1_reg[1],q1_reg[3],q1_reg[4]。

如果用户为以上三个变量设置了不正确的值(例如两个变量的值相同),工具会恢复使用这些变量的默认值,并给出OPT-916警告。

控制Multibit Banking优化过程

只有在满足以下条件时,多比特组件中的单比特单元才会被替换为多比特单元:

- 单比特单元的类型相同(触发器或锁存器)

- 库中存在与单比特单元功能等价的多比特单元

- 单比特单元由相同的时钟和控制信号驱动

- 单比特单元上没有设置dont_touch属性或size_only属性

- 单比特单元的时钟引脚或控制引脚上没有设置时序例外(如虚假路径、多周期路径)

- 如果单比特单元是保持型(retention)单元,则它们必须使用同一保持策略,由map_retention_cell命令的-lib_cells选项指定。如果用户在set_retention和map_retention_cell命令中使用了-elements选项来指定应用保持策略的单元,需要同时指定单比特和多比特的叶单元

为了指导Design Compiler在综合时如何进行多比特单元替换,可以在综合前使用set_multibit_options命令。

dcnxt_shell> set_multibit_options -mode mode_name其中mode_name可以是以下四种之一:

non_timing_driven(默认)

Design Compiler会在所有可能的地方使用多比特单元,最大化多比特替换比例,使剩余的单比特单元数量最少,允许时序和面积QoR变差。

timing_friendly

多比特推断力度与non_timing_driven类似,但在选择目标多比特库单元时以时序为优先,有助于改善时序,但在Multibit Banking过程中仍可能导致时序变差。

timing_driven

Design Compiler仅在不恶化时序QoR的前提下,才将单比特单元替换为多比特单元,对时序最保守。

none

Design Compiler在综合过程中不进行Multibit Banking优化。

写在最后

拓扑模式的Design Compiler Graphical推出了布局感知的Multibit Banking流程,会将物理位置上彼此接近的单比特单元分组并进行替换,与RTL向量自动推断流程和手动创建多比特组件流程相比更加强大。