**前言:**本文利用VerilogHDL语言,通过Xilinx提供的XDAC IP核实现ZYNC-7000 SOC芯片温度实时读取。

1. XADC概述

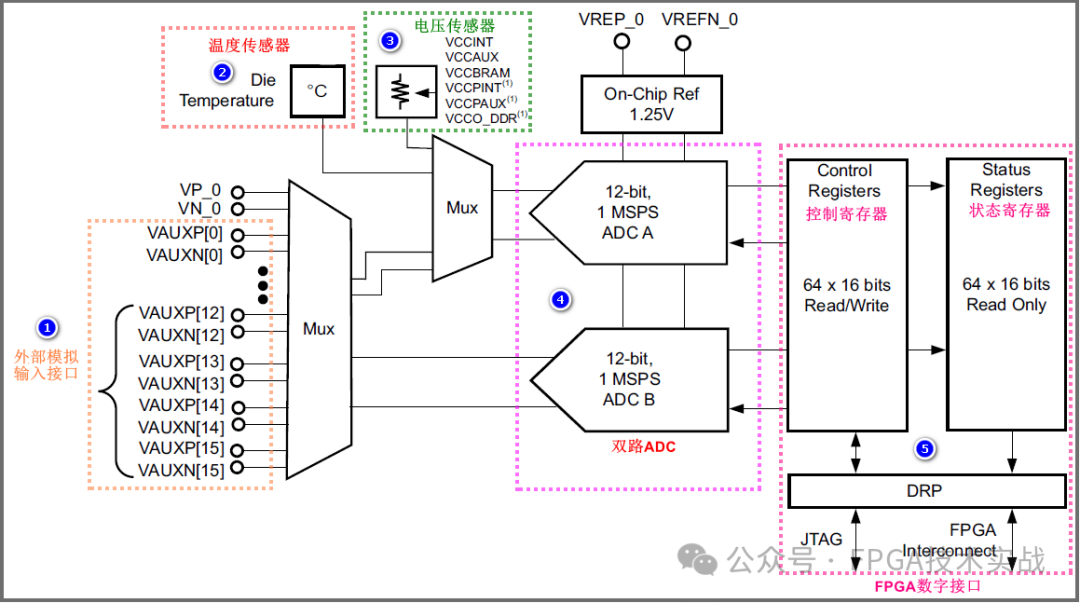

XADC IP核功能框图如下图所示。

图1、XADC IP核功能框图

如图1所示, XADC(7 系列 FPGA 的模数转换模块)核心包含 5 个关键部分:

- 外部模拟输入接口:提供 VP/VN 主通道及 VAUXP/VAUXN 等最多 17 个外部模拟输入通道,通过多路选择器(Mux)接入后续模块。

- 片上传感器:包含温度传感器(监测芯片温度)和电压传感器(监测 VCCINT 等片上电源电压),数据也会接入内部多路选择器。

- 双路 ADC:配备两个 12 位、1MSPS 采样率的 ADC(ADC A 和 ADC B),同时集成 1.25V 片上参考源(On-Chip Ref),负责将模拟信号转换为数字信号。

- 寄存器模块:包含 64×16 位的可读写控制寄存器(配置 XADC 工作),以及 64×16 位的只读状态寄存器(存储 ADC 转换数据)。

- FPGA数字接口:通过 DRP(动态重配置端口)连接 FPGA 互连结构,也支持 JTAG 接口访问,实现对 XADC 的配置与数据读取。

本文重点关注片上温度传感器、寄存器模块以及FPGA数字接口,以实现芯片温度获取。

2. XADC接口及温度解算

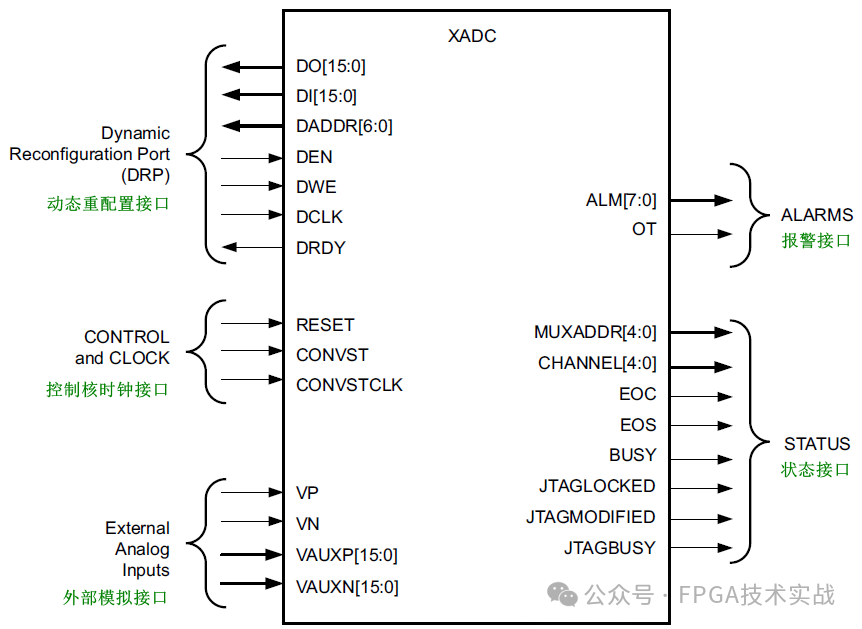

若仅需使用片上监测功能,设计中无需例化 XADC。不过,若未例化 XADC,唯一能获取这些信息的途径是通过 JTAG 测试访问端口(TAP)。若要从 FPGA 逻辑中访问状态寄存器(即测量结果),则必须例化 XADC,XADC原句端口定义如下图所示。

图2、XADC原句端口

| 端口功能分类 | 包含端口 | 说明 |

|---|---|---|

| DRP 接口端口 | DI[15:0]、DO[15:0]、DADDR[6:0]、DEN、DWE、DCLK、DRDY | 用于 XADC 的动态重配置与数据读写,实现 FPGA 逻辑与 XADC 的寄存器交互 |

| 控制类端口 | RESET、CONVST、CONVSTCLK | 负责 XADC 的复位、转换启动(事件 / 时钟触发),控制采样与工作流程 |

| 模拟输入端口 | VP/VN、VAUXP[15:0] VAUXN[15:0] | 接入外部模拟信号(主通道 + 16 个辅助通道),支持差分 / 单端输入模式 |

| 告警输出端口 | ALM[0]~ALM[6] | 输出片上传感器(温度、各电源电压)的告警信号,提示异常状态 |

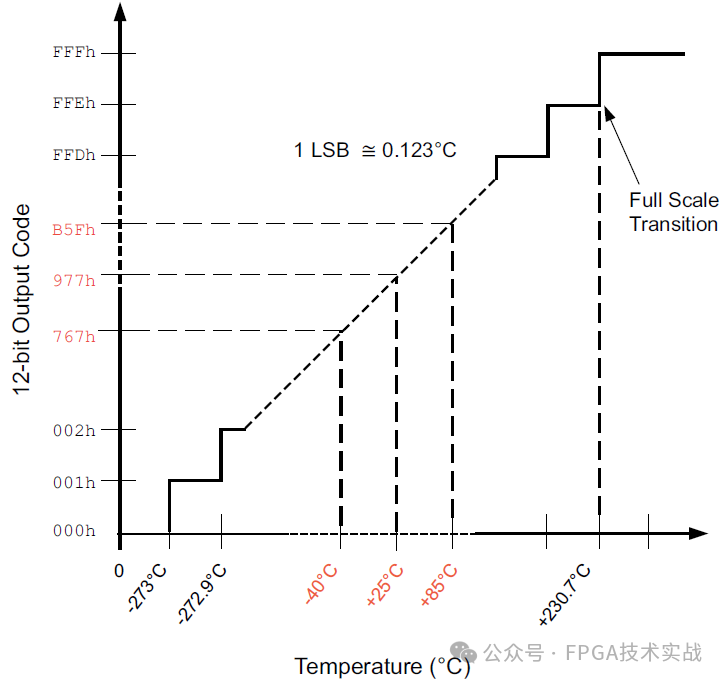

图3、温度传感器传递函数

温度传感器的传递函数由以下公式给出:

例如,当 ADC 编码为 2423(十六进制 977h)时,对应温度为 25°C。

温度测量结果会存储在 DRP 地址 00h 对应的状态寄存器中。通过监控 FPGA 的片上温度,确保不超过关键工作温度,从而避免功能故障和不可逆损坏。

3. XADC温度读取操作时序

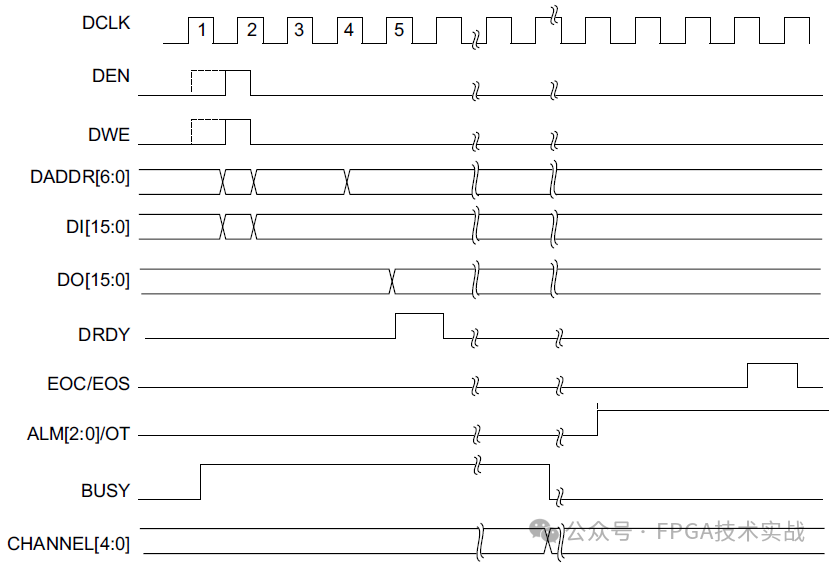

DRP接口操作时序如下图所示,通过该接口实现温度读取。

图4、DRP接口操作时序

图 4 展示了 DRP 的读写操作流程:当 DEN 为高电平时,DRP 地址(DADDR)和写使能(DWE)输入会在 DCLK 的下一个上升沿被捕获,且 DEN 仅需在一个 DCLK 周期内保持高电平。

若 DWE 为低电平,则执行 DRP 读操作:当 DRDY 变为高电平时,DO 总线上的数据有效,因此需通过 DRDY 来捕获 DO 总线的数据。对于写操作,DWE 信号为高电平,DI 总线与 DRP 地址(DADDR)会在 DCLK 的下一个上升沿被捕获;当数据成功写入 DRP 寄存器后,DRDY 信号会变为高电平。在 DRDY 信号变低之前,无法启动新的读写操作。

4. XADC温度读取编程设计

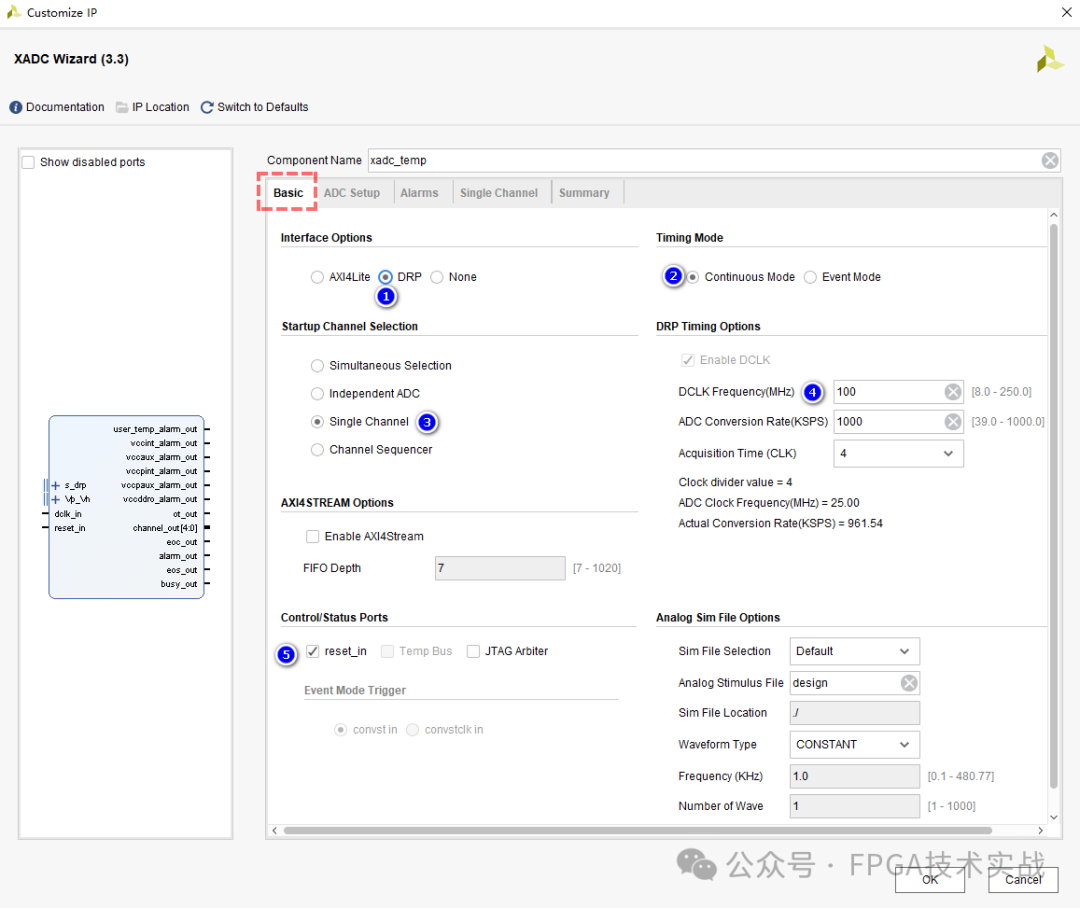

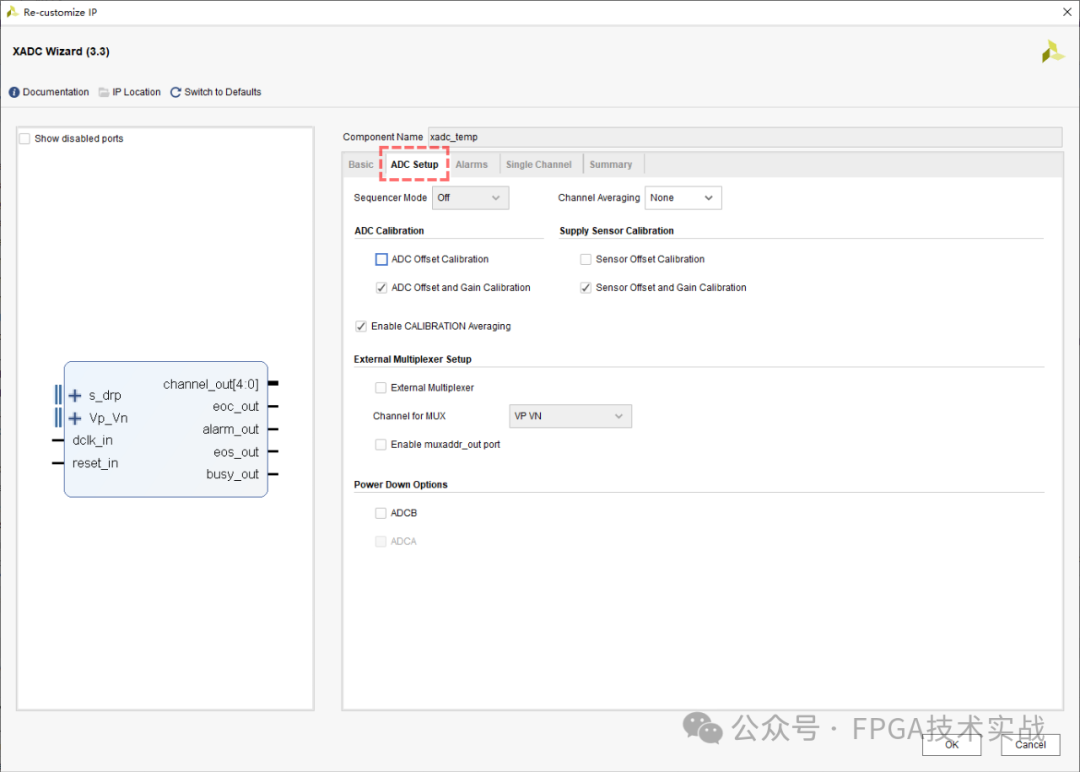

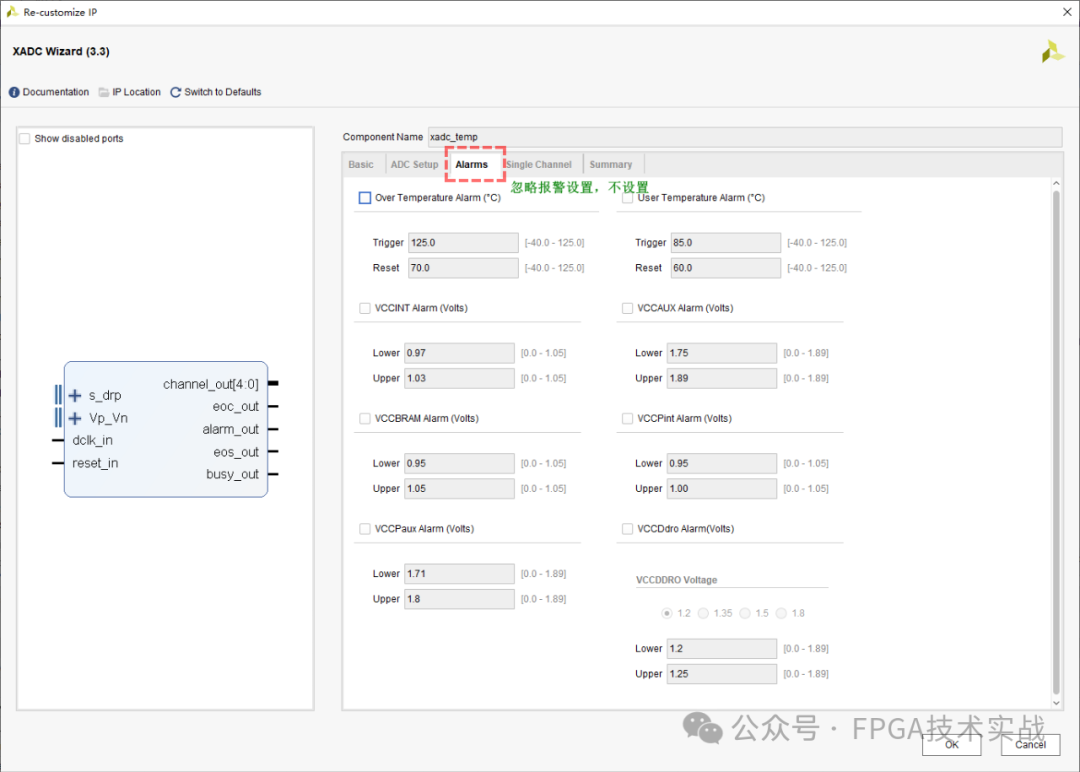

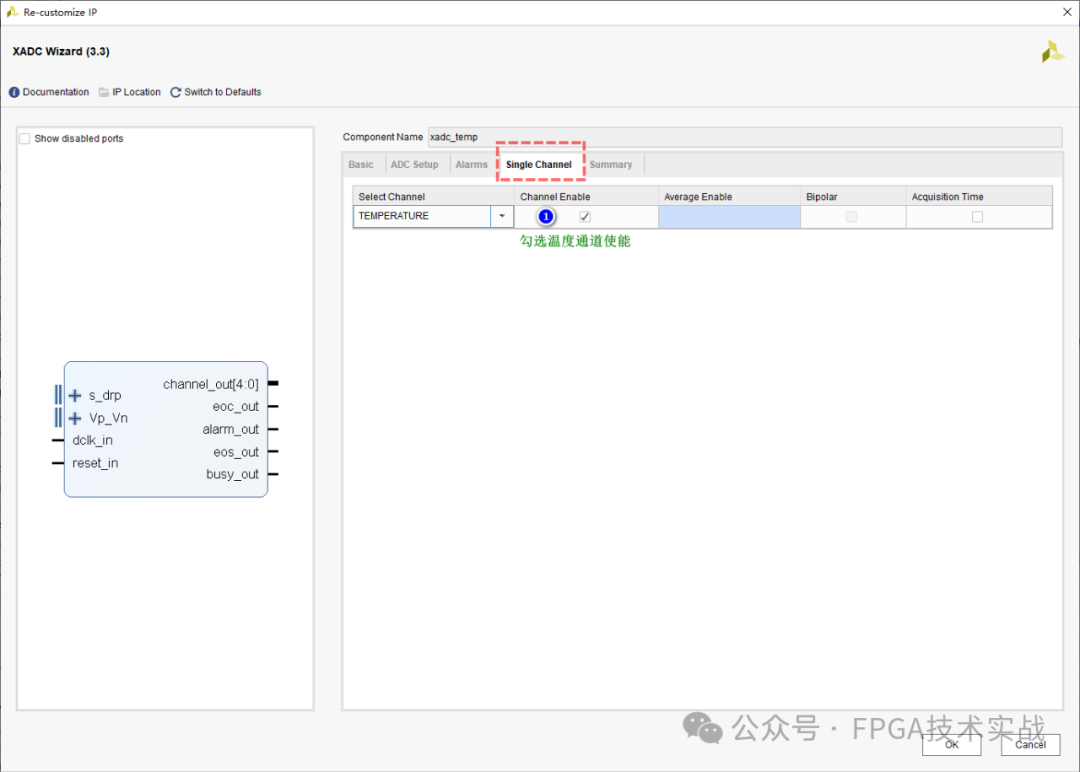

4.1 XADC IP核配置

(1)在Vivado软件 IP Catalog中搜索"XADC",打开XADC Wizard。

(2)XADC IP核配置依次如下图所示。

4.2 代码编写

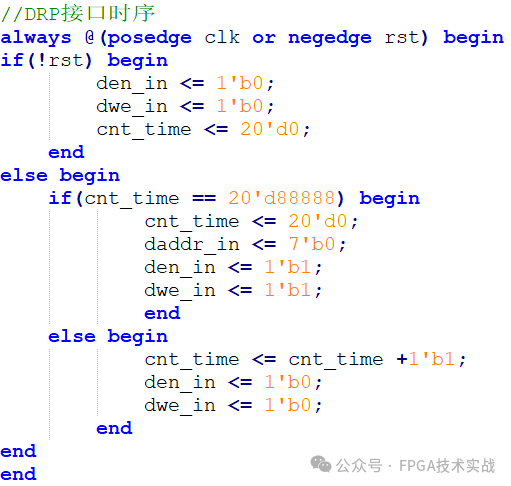

(1) DRP接口时序

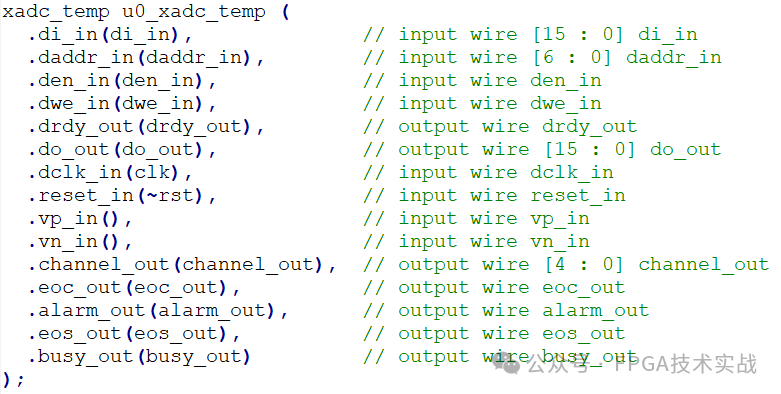

(2) XADC IP例化

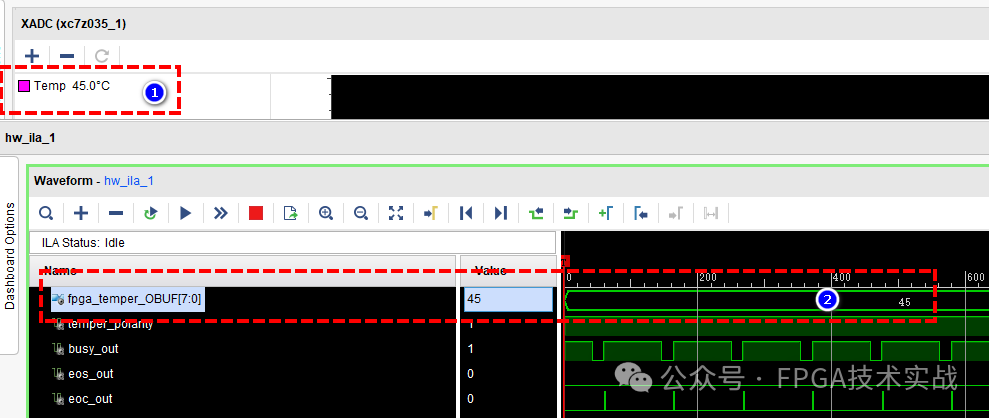

4.3 程序下载实测结果

软件下载至电路板,抓取温度数据,对比JTAG XADC温度数据,验证读出温度数据正确。