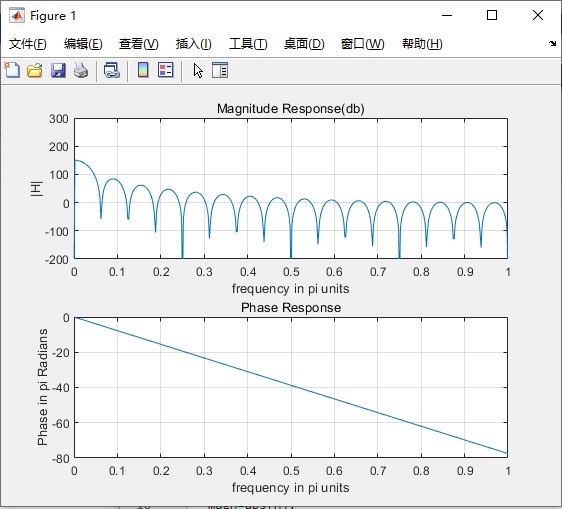

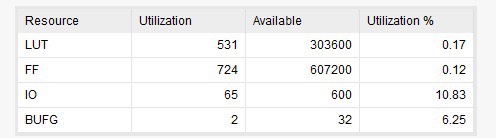

基于FPGA的积分梳状CIC滤波器verilog设计 1.系统概述 这里设计的五级CIC滤波器。 那么其基本结构如上图所示,在降采样的左右都有五个延迟单元。 但是在CIC滤波的时候,会导致输出的位宽大大增加,但是如果单独对中间的处理信号进行截位,这会导致处理精度不够,从而影响整个系统的性能,所以,这里我们首先将输入的信号进行扩展。 由于我们输入的中频信号通过ADC是位宽为14,在下变频之后,通过截位处理,其输出的数据仍为14位,所以,我们将CIC滤波的输入为14位,但是考虑到处理中间的益处情况以及保证处理精度的需要,我们首先将输入位宽扩展为40位,从而保证了处理精度以及溢出的情况。 这里首先说明一下为什么使用的级别是5级。 从硬件资源角度考虑,CIC滤波器的级数太高,会导致最终输出的数据位宽很大,通过简单的验证,当CIC的级数大于5的时候,输出的位宽>50。 这显然会导致硬件资源的大量占用,如果CIC级数太小,比如1,2级。 这在其处理效果上没有任何意义,基本无法达到预计的效果,通过仿真分析,一般情况下,选择4级,5级比较合理,因此,这里我们选择5级的CIC滤波器。 2.系统仿真效果预览 如图所示 3.产品包含:Matalab verilog仿真和代码 演示视频 论文报告 PPT

在数字信号处理的领域中,积分梳状(CIC)滤波器凭借其结构简单、高效等特性,在诸如抽取和插值等应用场景里发挥着重要作用。今儿个咱就唠唠基于FPGA的五级CIC滤波器Verilog设计。

一、系统概述

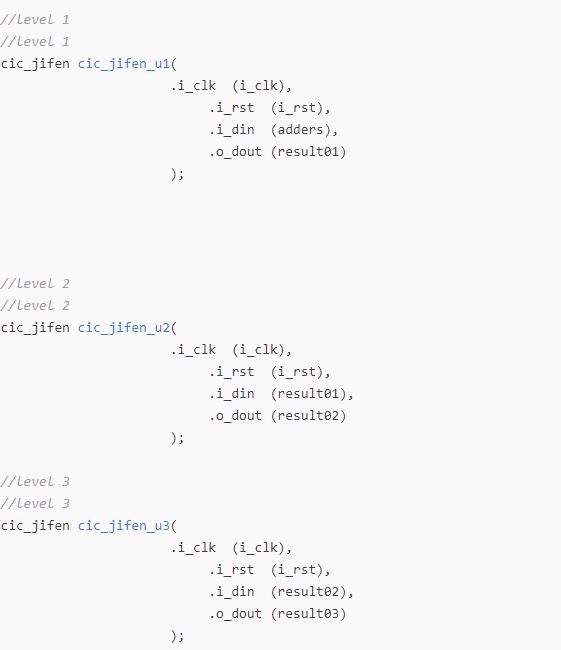

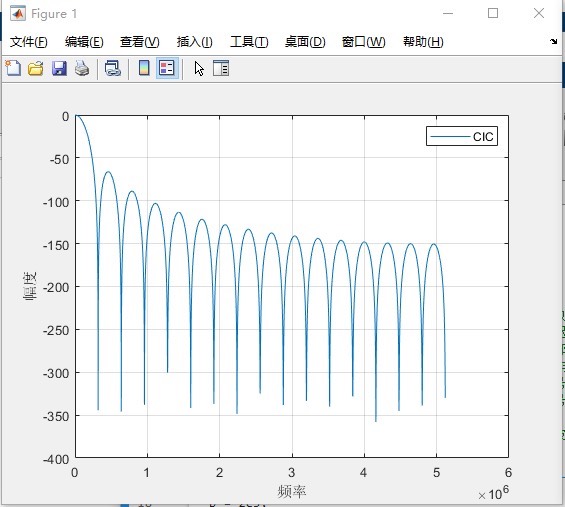

咱设计的可是五级CIC滤波器哦。瞅瞅它的基本结构,降采样的两边都各有五个延迟单元。这CIC滤波过程中有个小麻烦,那就是输出的位宽会大大增加。要是单独对中间处理信号截位,处理精度就不够了,整个系统性能也得受影响。所以呢,咱得先把输入信号扩展一下。

咱输入的中频信号经过ADC,位宽是14位,下变频后截位处理,输出还是14位。但为了处理中间可能出现的溢出情况,同时保证处理精度,就把CIC滤波的输入位宽扩展到40位。这样既能保证精度又不怕溢出啦。

再说说为啥选5级。从硬件资源角度看,CIC滤波器级数要是太高,最终输出数据位宽就大得吓人。简单验证下,级数大于5的时候,输出位宽大于50,这得多占多少硬件资源呐!可要是级数太小,像1级、2级,处理效果基本没啥用,根本达不到预期。通过仿真分析,一般选4级、5级比较靠谱,所以咱就选了5级的CIC滤波器。

Verilog代码示例与分析

verilog

module cic_filter (

input wire clk, // 时钟信号

input wire rst, // 复位信号

input wire [13:0] din, // 14位输入数据

output reg [39:0] dout // 40位输出数据

);

reg [39:0] delay_1 [0:4]; // 延迟单元1

reg [39:0] delay_2 [0:4]; // 延迟单元2

// 这里省略其他延迟单元声明,类似delay_1和delay_2

always @(posedge clk or posedge rst) begin

if (rst) begin

for (int i = 0; i < 5; i = i + 1) begin

delay_1[i] <= 40'd0;

delay_2[i] <= 40'd0;

// 其他延迟单元复位

end

dout <= 40'd0;

end else begin

delay_1[0] <= {{26{din[13]}}, din}; // 输入数据扩展为40位并存入第一个延迟单元

for (int i = 1; i < 5; i = i + 1) begin

delay_1[i] <= delay_1[i - 1]; // 数据在延迟单元1中传递

end

// 积分部分

delay_2[0] <= delay_1[4] + delay_2[4];

for (int i = 1; i < 5; i = i + 1) begin

delay_2[i] <= delay_2[i - 1]; // 数据在延迟单元2中传递

end

// 梳状部分,这里只简单示意,实际更复杂

dout <= delay_2[4];

end

end

endmodule上面这段代码就是简单的五级CIC滤波器Verilog实现。模块定义了输入时钟、复位信号,14位的输入数据以及40位的输出数据。通过两个数组delay1**和delay 2来实现延迟单元。在时钟上升沿或者复位信号有效时,复位延迟单元和输出数据。正常工作时,先将输入数据扩展为40位存入delay1**数组,然后数据在延迟单元1中依次传递,完成积分部分的操作。再在delay 2数组中传递,简单模拟梳状部分操作,最后输出结果。

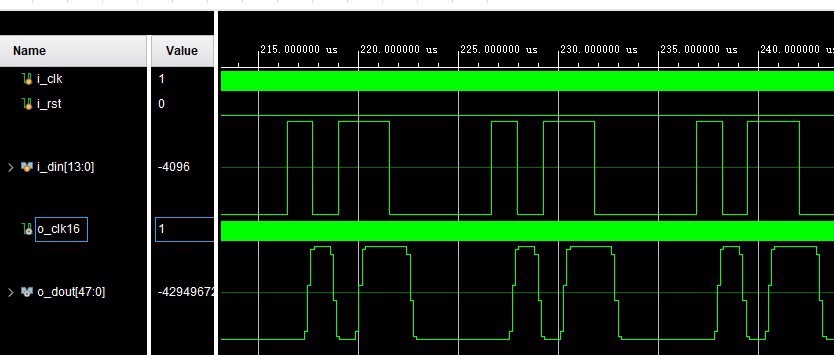

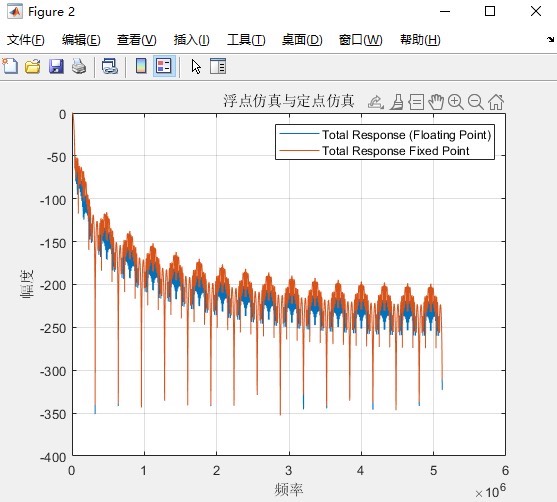

二、系统仿真效果预览

很可惜这里没法直接展示图哈,但在实际仿真中,我们可以看到这个五级CIC滤波器对输入信号的处理效果。通过观察输出信号的频谱等特性,可以验证滤波器是否达到了预期的设计目标,比如是否有效地滤除了不需要的频率成分,是否在抽取过程中保证了信号的完整性等等。

三、产品包含

这次的设计产品那可丰富了,有Matlab Verilog仿真和代码,通过Matlab可以更直观地对滤波器的性能进行分析和验证,和Verilog代码相互配合,能更好地理解设计。还有演示视频,能动态展示滤波器的工作过程。另外论文报告和PPT,详细阐述设计原理、实现过程以及性能分析等内容,方便大家深入研究。

总之,基于FPGA的五级CIC滤波器Verilog设计,通过合理的结构和位宽处理,在保证硬件资源合理利用的同时,实现了高效的数字信号滤波处理。