一个完整的以太网项目,系统级电路 10/100Mbps 10BASE-T ETHERENT-PHY 适合有几年工作经验的或者博士研究生 [1]有两个版本,一份是工艺是Gpdk90nm(主要),一份是Gpdk180nm,都是有版图(TOP,cell都有),Cadence自己家的电路 [2]有两个锁相环,模拟均衡器eq,pi相位差值,flash ADC,带triming bg,LDO,比较器,电平移位,译码电路,数字电路,偏置电流源,运放,trans,DAC,滤波器 [3]有很多仿真tb,非常的详细,两个子模块PLL仿真,ADC仿真,bg ldo 模块仿真,TOP整体ams仿真,有版图,没留片,不是反向电路。 这只适合学习用啊,不适合各位想着拿去直接公司用啊。 也不适合大佬 所有文件有十几份RAK,有四五份 pdf是讲top的,然后有七八份pdf是讲里面的子模块的。

最近接触到一个超有意思的10/100Mbps 10BASE - T ETHERENT - PHY以太网项目,感觉对有几年工作经验的工程师或者博士研究生来说,是个绝佳的学习资源,今天就来和大家唠唠。

工艺与版图

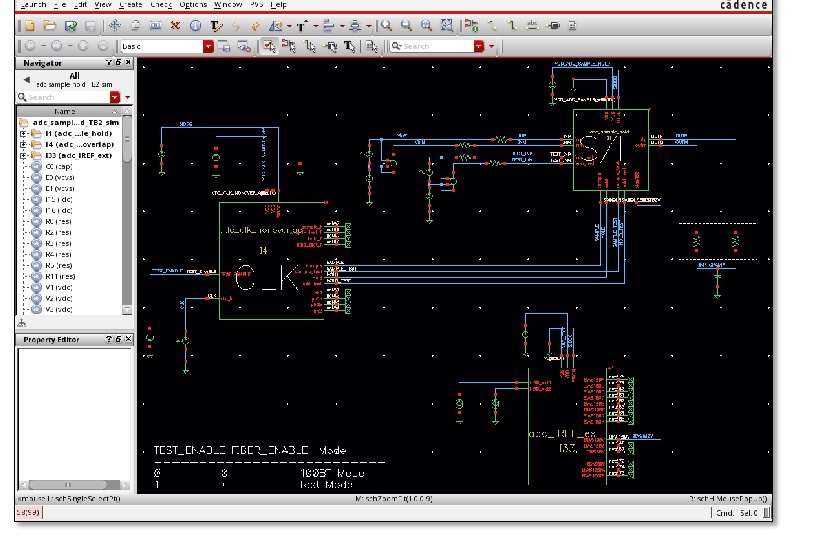

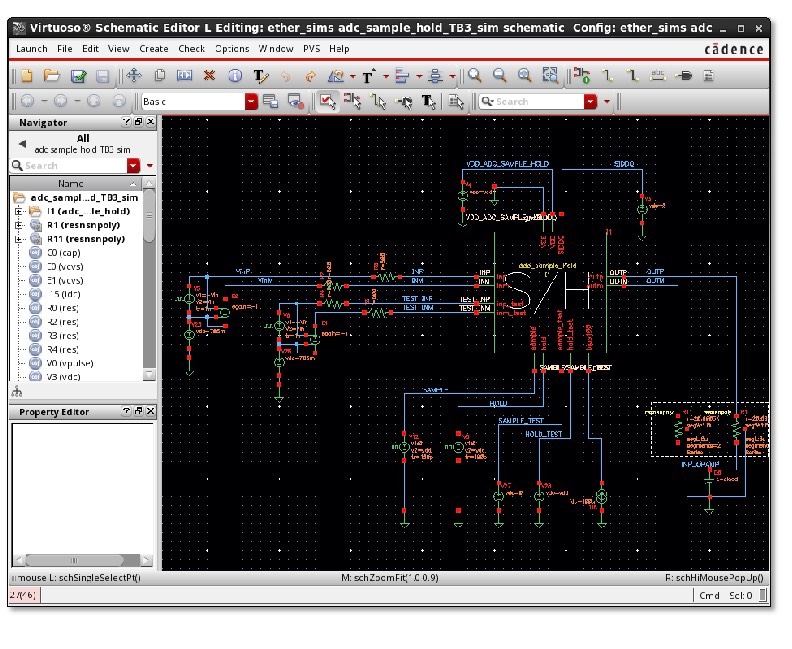

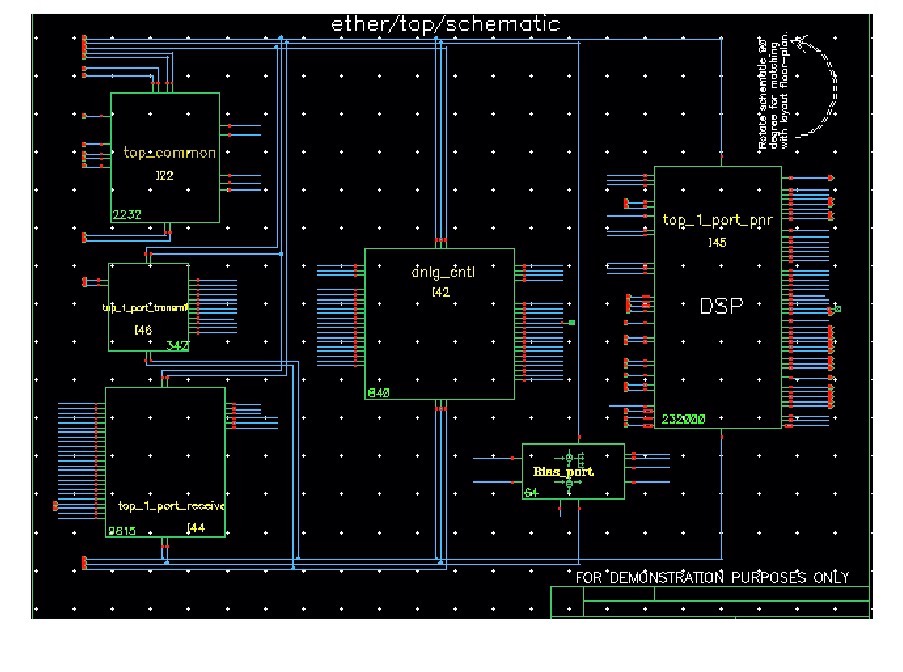

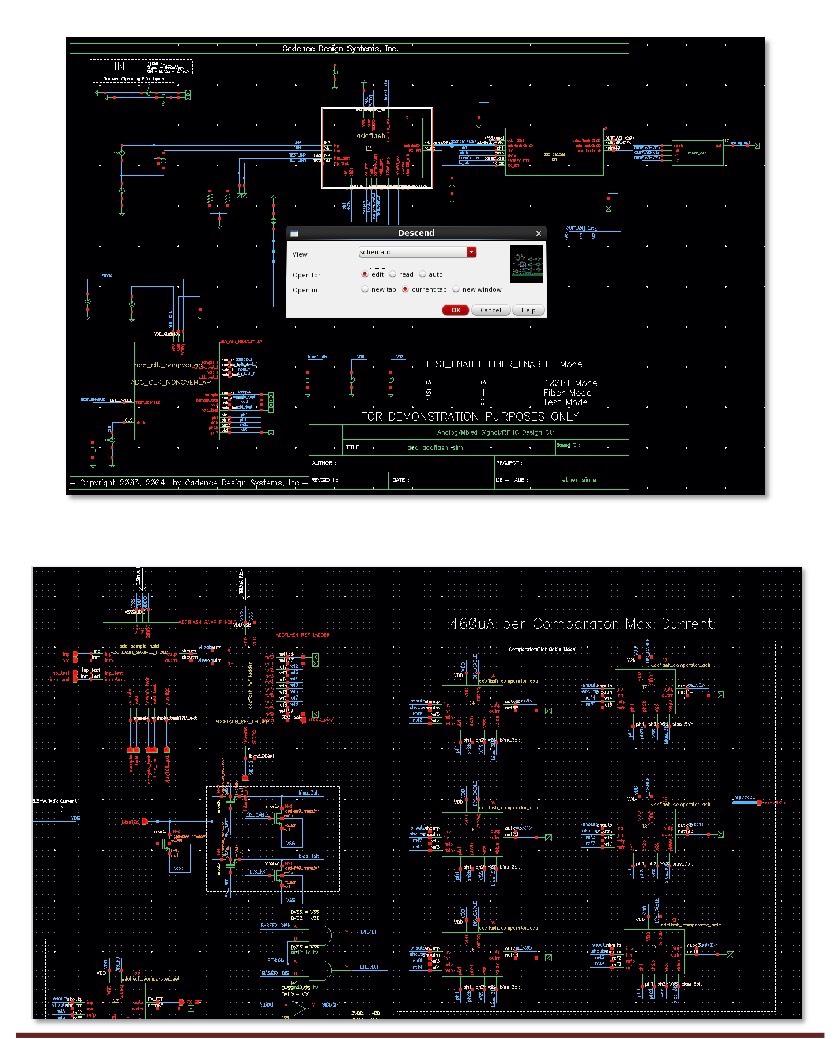

这个项目有两个版本,主要的是Gpdk90nm工艺,另一个是Gpdk180nm工艺 。而且它厉害之处在于,Cadence自家的电路不仅有完整的版图,包括TOP级版图以及各个cell的版图。这对于想要深入了解从电路设计到版图实现整个流程的同学来说,简直是宝藏。想象一下,能看到每个模块从原理图到实际版图的映射,这对理解电路的物理实现以及寄生效应等问题有很大帮助。

丰富的电路模块

锁相环(PLL)

项目中有两个锁相环。锁相环在电路系统里的作用就像一个精准的时钟指挥官,能让各个模块在统一、稳定的时钟信号下有条不紊地工作。简单来说,它通过反馈机制,将输出信号的相位与参考信号的相位进行比较,然后调整输出信号的频率,使其与参考信号同步。在Verilog中,一个简单的PLL模块框架代码可能长这样:

verilog

module simple_pll (

input wire clk_in, // 输入参考时钟

input wire rst, // 复位信号

output reg clk_out // 输出经过调整的时钟

);

reg [31:0] counter; // 计数器,用于频率调整

always @(posedge clk_in or posedge rst) begin

if (rst) begin

counter <= 32'd0;

clk_out <= 1'b0;

end else begin

counter <= counter + 1;

if (counter == 32'd1000) begin // 这里1000只是示例值,实际根据频率需求调整

clk_out <= ~clk_out;

counter <= 32'd0;

end

end

end

endmodule在这个简单代码里,通过计数器对输入时钟进行计数,达到一定值后翻转输出时钟信号,从而实现对频率的调整。当然,实际项目中的PLL要复杂得多,会涉及到更精确的相位比较和控制算法。

模拟均衡器(eq)、pi相位差值等模拟模块

模拟均衡器eq能对信号的幅度和相位进行调整,补偿信号在传输过程中的损耗和失真。而pi相位差值模块则在处理信号相位关系上发挥重要作用。这些模拟模块就像是电路系统里的精细微调师,让信号以最佳状态传输。

数字电路模块

像flash ADC(闪存模数转换器)、译码电路等数字模块也一应俱全。flash ADC可以快速地将模拟信号转换为数字信号,它的工作原理是通过多个比较器同时对输入模拟信号与不同参考电压进行比较,然后经过编码电路输出对应的数字码。译码电路则负责将特定的编码转换为相应的控制信号或数据。

verilog

module flash_adc (

input wire [7:0] analog_in, // 8位模拟输入信号

output reg [3:0] digital_out // 4位数字输出信号

);

always @(*) begin

case (analog_in)

8'd0: digital_out = 4'd0;

8'd1: digital_out = 4'd1;

// 依次列出不同模拟值对应的数字输出

8'd15: digital_out = 4'd15;

default: digital_out = 4'd0;

endcase

end

endmodule这段简单代码展示了一个非常基础的flash ADC转换逻辑,实际的flash ADC会涉及到更多复杂的比较和编码逻辑。

其他模块

还有带triming bg(带微调的带隙基准源)、LDO(低压差线性稳压器)、比较器、电平移位、偏置电流源、运放、trans(可能是晶体管相关模块)、DAC(数模转换器)、滤波器等模块。这些模块各自承担着不同的功能,共同构建起这个复杂而强大的以太网系统。比如LDO能为其他模块提供稳定的低噪声电源,运放则常用于信号放大和处理等。

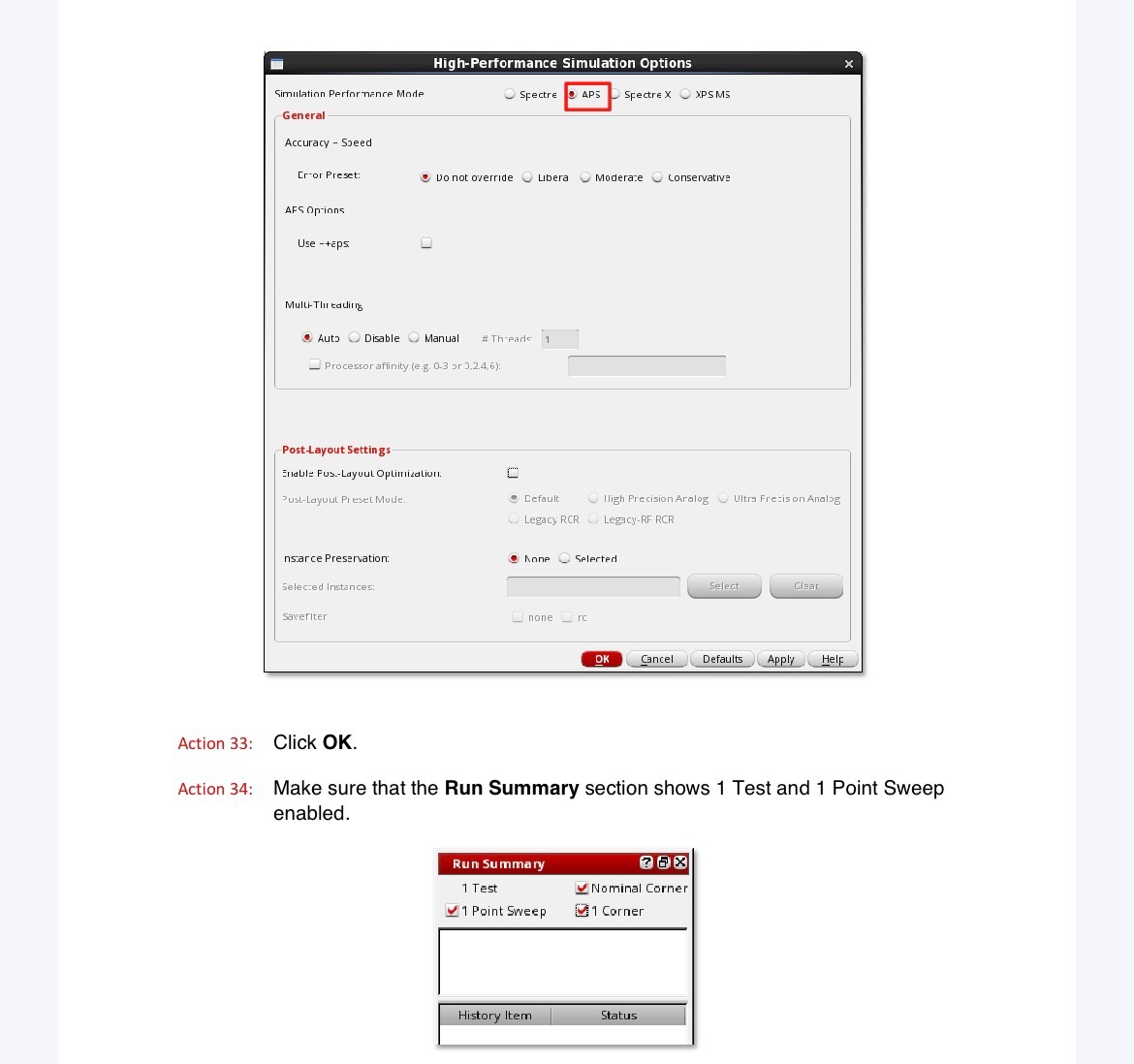

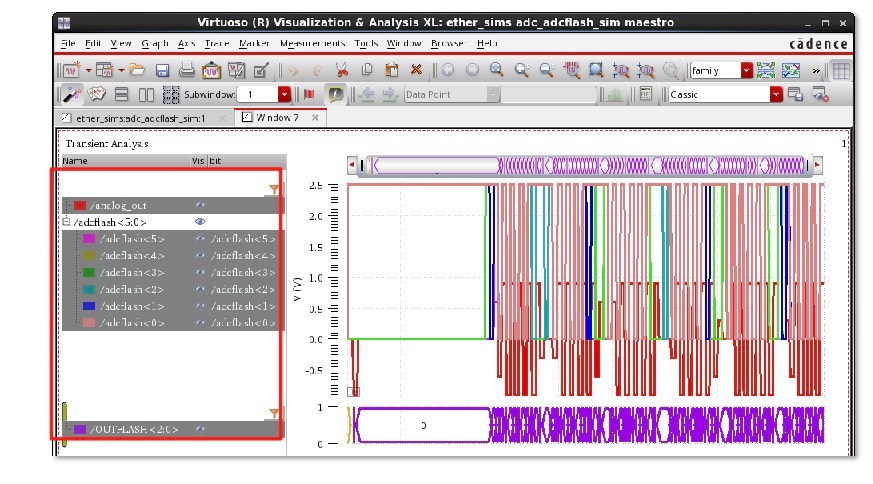

详细的仿真测试

项目里有超多详细的仿真tb(测试平台)。有针对两个子模块PLL的仿真,能验证PLL的频率锁定、相位噪声等性能指标。ADC仿真则可以观察ADC的转换精度、线性度等参数。还有bg ldo模块仿真,测试带隙基准源和低压差稳压器的性能。最厉害的是TOP整体ams(模拟混合信号)仿真,能从系统层面验证整个以太网电路的功能和性能。虽然有版图,但没留片,并且不是反向电路,这也再次强调了它更适合学习研究。

文件构成

所有文件有十几份RAK格式的,估计里面包含了各种源文件、配置文件之类的。还有四五份pdf是讲top级设计的,能让你从整体上把握项目架构。另外有七八份pdf是讲里面子模块的,方便你深入了解每个模块的设计细节。

不过要提醒一下,这个项目只适合学习用啊,各位可别想着拿去直接在公司用,毕竟它可能不完全符合实际项目的各种复杂需求,也不太适合已经是行业大佬级别的人,他们估计早就对这些轻车熟路啦。希望这个分享能让大家对这个以太网项目有更清晰的认识,说不定能给你的学习或研究带来新的启发。