一、寄存器映射

-

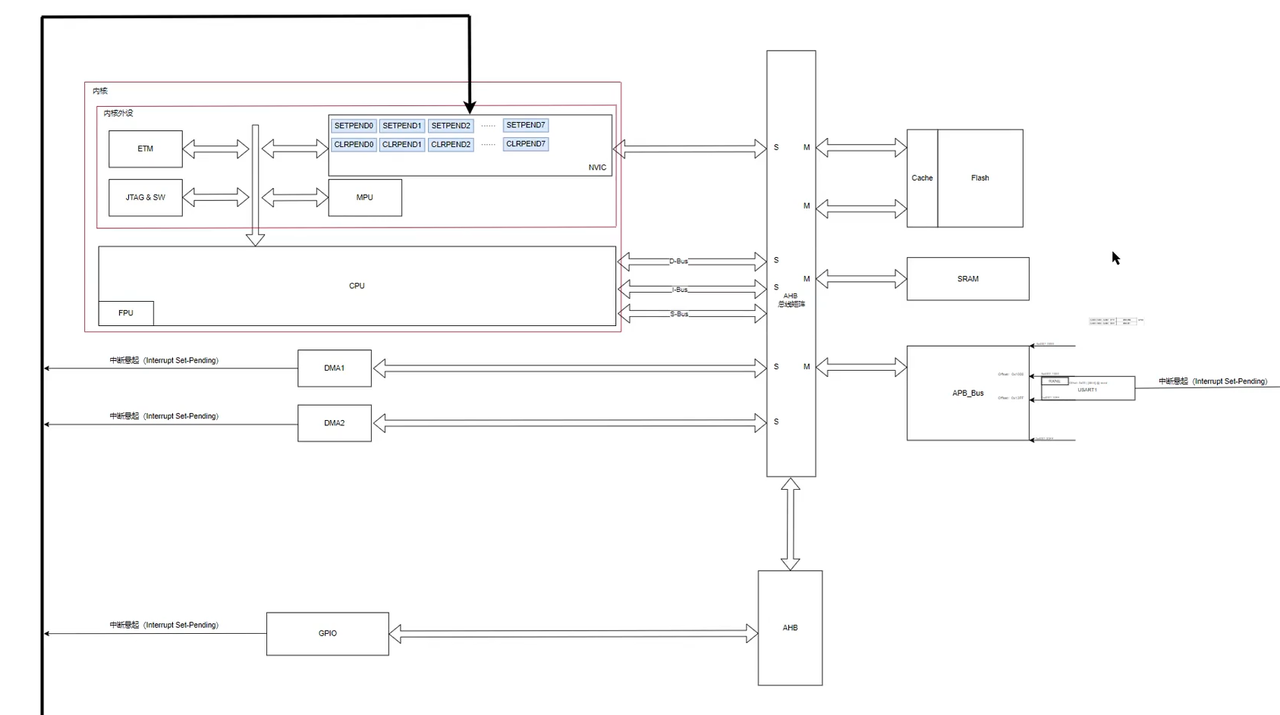

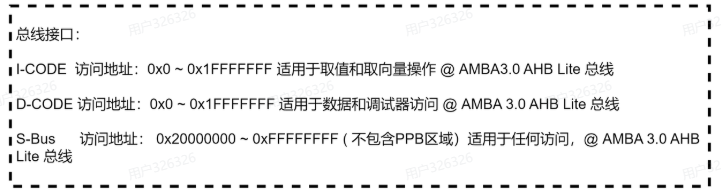

内核里面的cpu主要通过D-Bus,I-Bus,S-Bus与外设沟通,其中S-Bus是主要用来访问外设的

-

当我们访问一个外设地址时,数据会从cpu然后通过S-Bus再到AHB总线矩阵,经过某些处理到达APB(挂载着外设)

-

但APB_BUS也不知道这个地址是什么,只有cpu知道,然后被转译到apb,只知道在自己总线上寻址访问,(后续需要联通从memory map ->图示->bootloadr->再到bus总线->芯片架构)

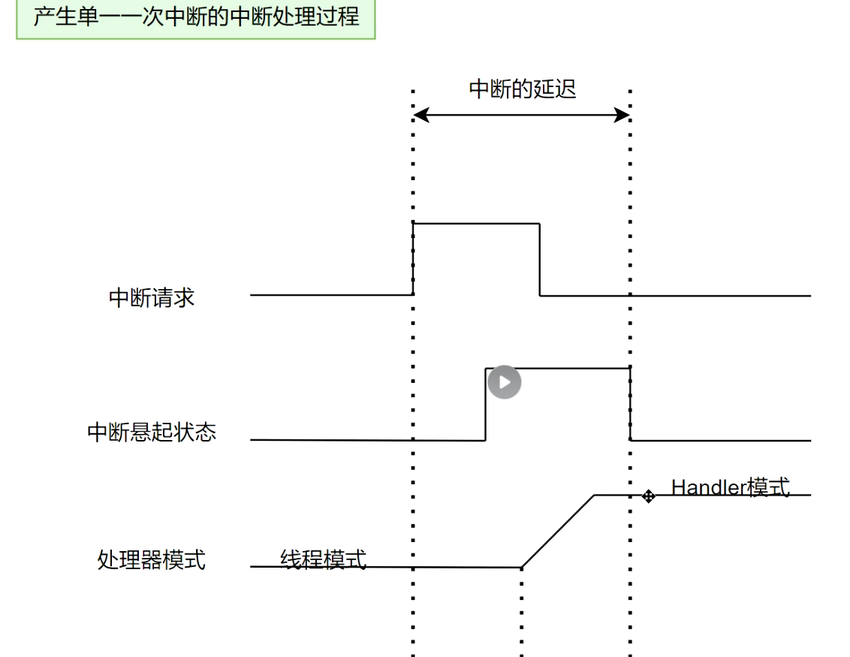

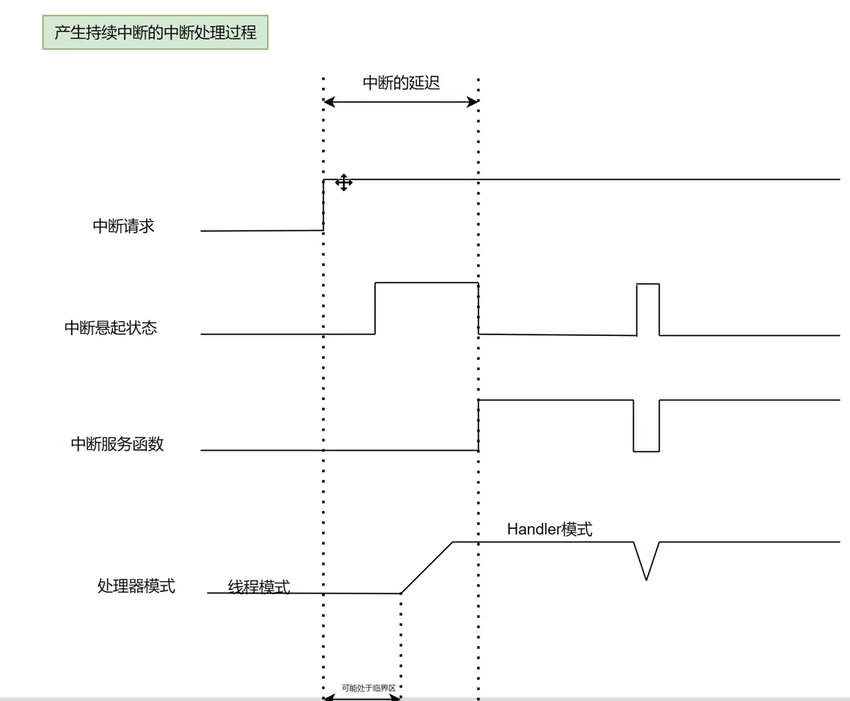

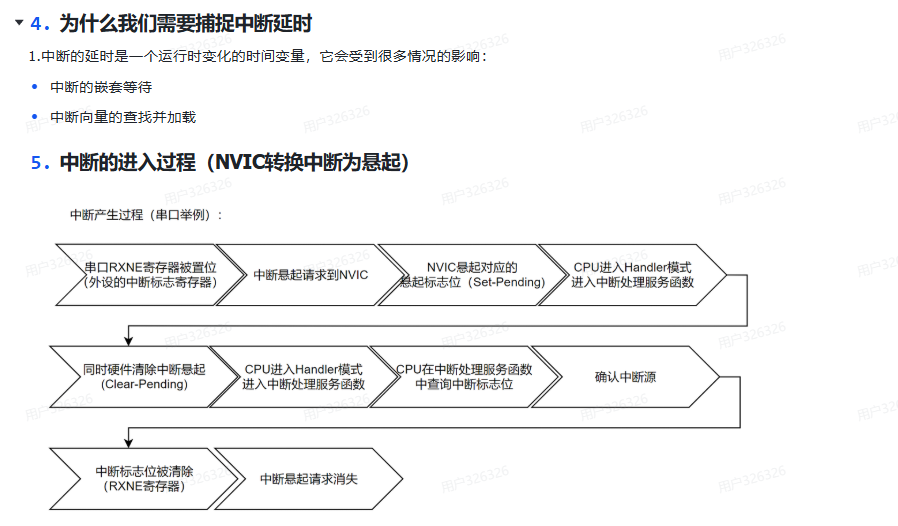

二中断悬起|中断的延迟|中断时怎么被处理的|产生单一一次中断的中断处理过程

1.

-

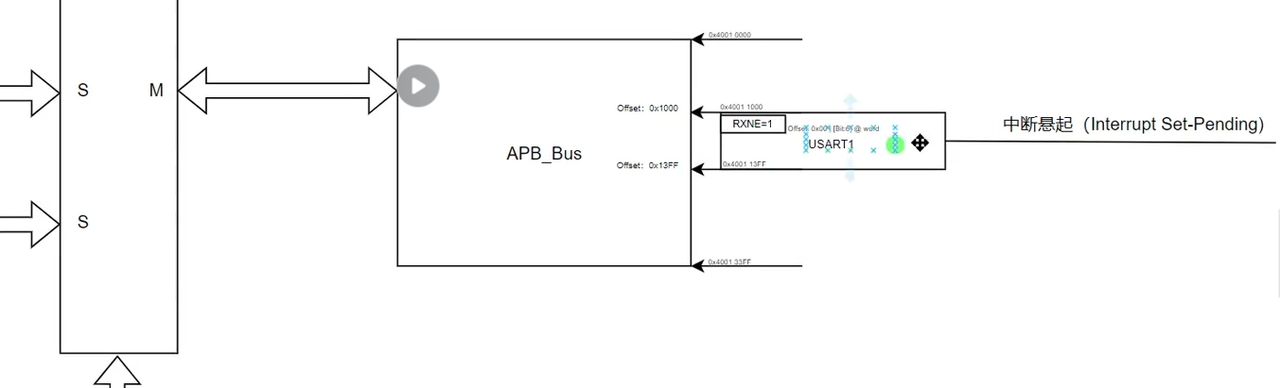

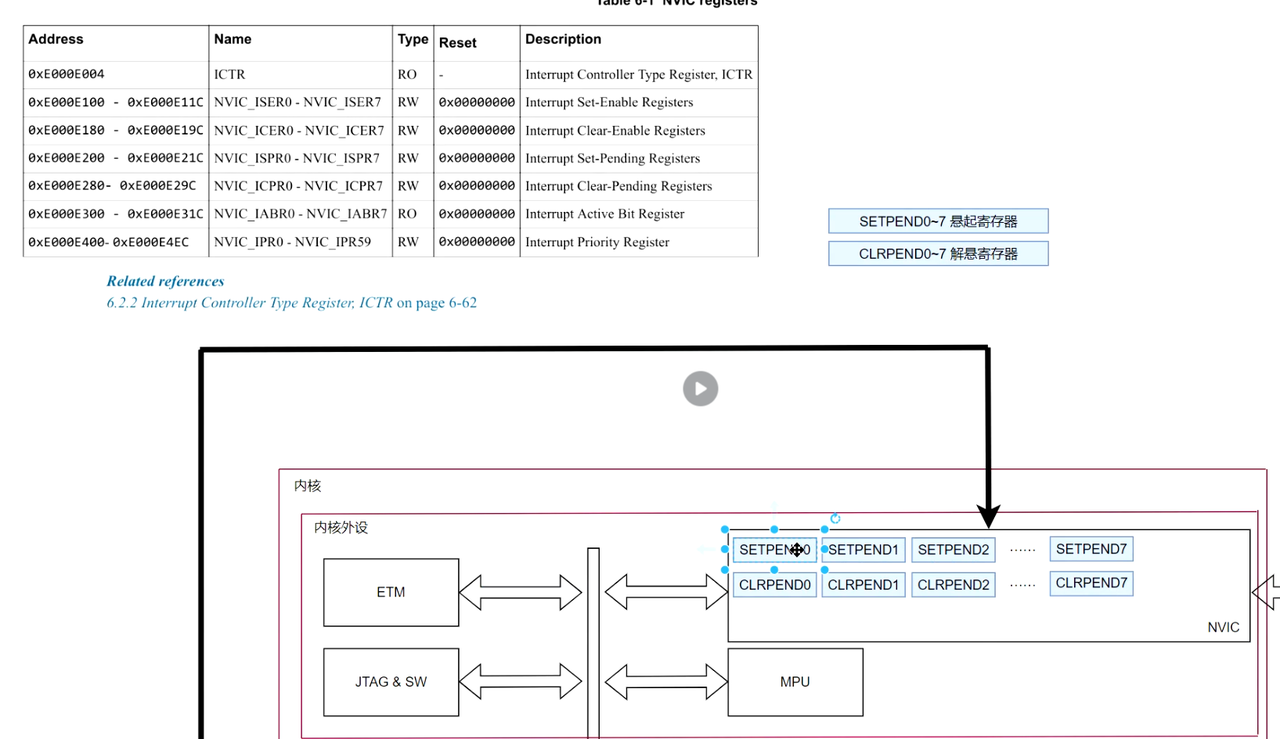

当外设发生了中断,就会在总线上发起一次请求,最后就会传到NVIC,然后将特定的寄存器(此处为悬起寄存器)

-

悬起寄存器会引起内部异常,然后会通知cpu去响应异常

-

处理器此时会从线程模式,转变为handle模式,当检测到有悬起,就会去写解悬寄存器

-

进入了中断函数悬起马上就会解悬

拓展:

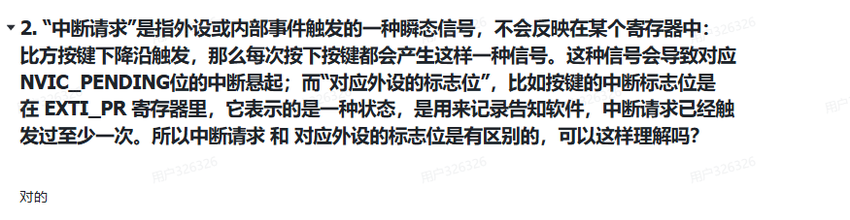

三、了解持续触发中断的中断处理过程

-

与上面只触发一次不同,当有持续的中断到来,第一次处理过程是一样的(当进入了中断服务函数,马上就会清除悬起标志位),但是中断服务函数还没退出的时候,因为写了解悬寄存器,所以悬起寄存器不会悬起

-

当cpu退出中断服务后,当外部中断还再触发,此时悬起寄存器再次挂起,处理器会再次进入handle模式

一个重要的特例:电平触发中断

对于电平触发的中断(如外部GPIO中断),需要特别注意:

-

在进入中断服务程序后,NVIC会清除悬起位。

-

但是,如果中断引脚上的电平在中断服务程序退出前一直没有恢复(比如仍然是高电平),那么NVIC硬件会立即再次置起悬起位。

A:为什么一直触发不会悬起

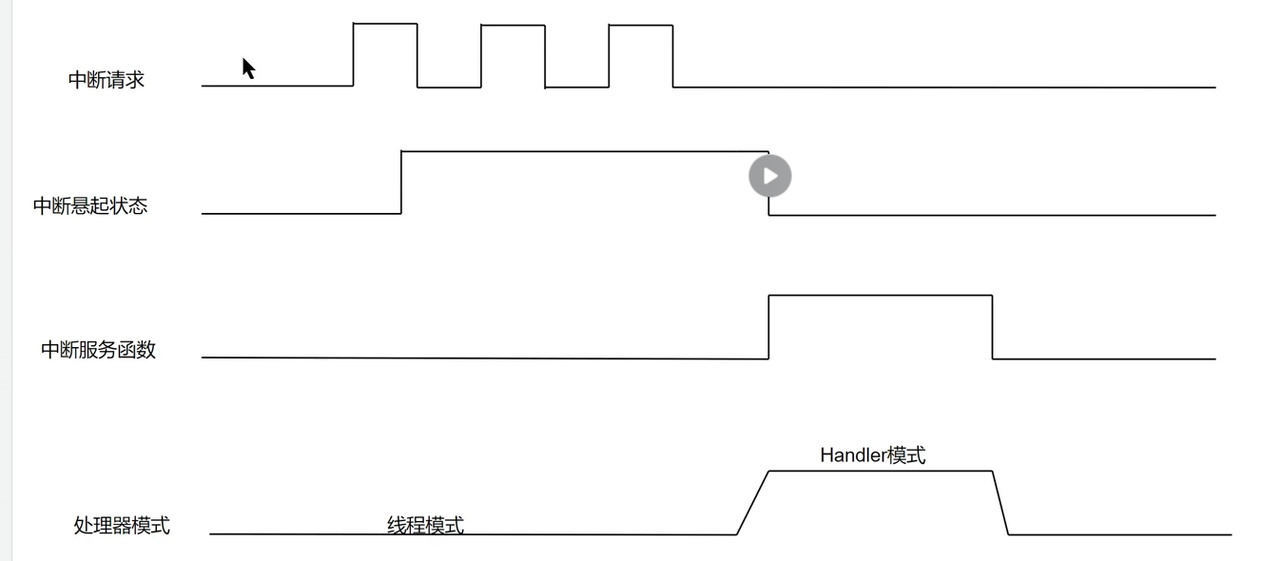

四、产生多次中断脉冲的中断处理过程(脉冲位于中断悬起过程中)

丢中断情况一:中断请求产生于中断悬起过程中

- 如果这种脉冲式中断,因为中断悬起寄存器只有一个,所以在没有解旋之前,都算作一次的中断请求,同时他们都是同一个中断标志位,所以进入中断服务函数后,只会处理一次

丢中断情况二:中断请求产生于中断服务函数(在单核f411不会出现,但在多核可能出现)

此状况就是在中断服务函数的时候,(中断请求只是一个状态,中断请求带来的是中断标志位),在后面时刻,同时把两个标志位同时清除了。(在中断函数进程当中,pending位还是能被置一)

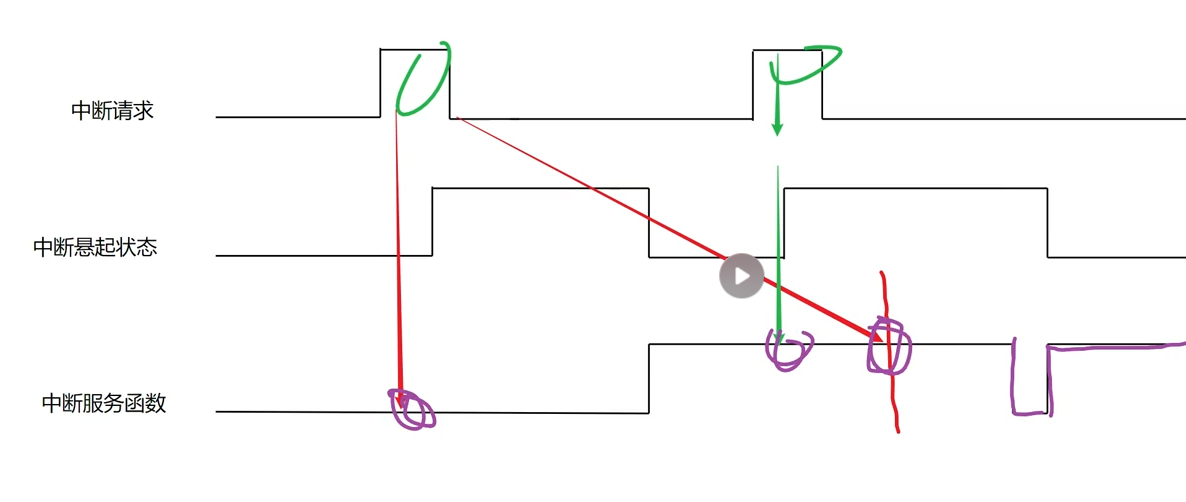

A:为什么在处理中断服务函数时有一个中断 脉冲 触发该中断又可以挂起,他不是屏蔽了吗

拓展与总结:

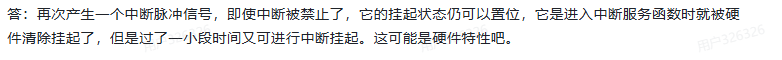

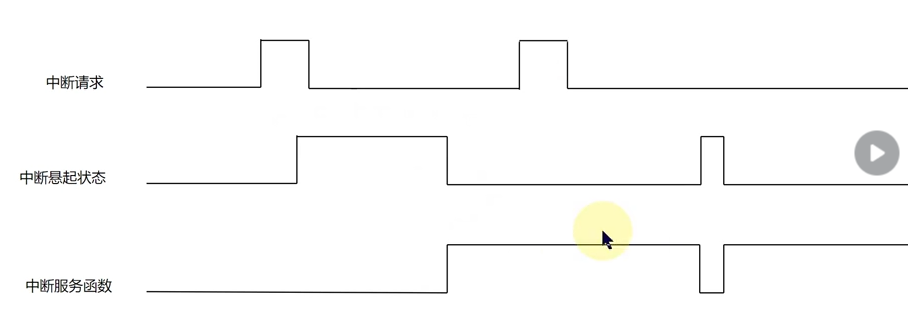

这与我们之前讨论的"标准NVIC行为"有何区别?

您之前的理解和我们之前的讨论,是基于ARM Cortex-M内核NVIC的典型或标准行为。而这张图展示的是一种可能的软件模拟策略或特定硬件控制器的工作方式。

我们将两者对比一下:

结论

所以,回答您的问题:"那这张图为什么有中断请求不能再次悬起?"

因为这张图描述的不是ARM Cortex-M NVIC的标准硬件行为,而是一种特定的、旨在防止中断重入和保证系统稳定性的逻辑模型。 在这种模型下,"悬起位"更像是一个"门锁",门锁一旦打开(悬起位置1),在门被关上之前(悬起位清除),任何试图再次开门(新的中断请求)的动作都是无效的。

若新中断请求是更高优先级

- 能再次置位悬起位,且会嵌套中断:即使在当前中断函数中清除了悬起位,只要新请求的中断优先级更高,硬件会再次置位其悬起位,且 CPU 会打断当前中断函数,优先执行更高优先级的中断服务。

若新中断请求是同优先级或更低优先级

-

分两种情况:

-

若系统允许同优先级中断嵌套(需特殊配置):可再次置位,执行完当前函数后会响应新请求;

-

若系统默认不允许同 / 低优先级嵌套(如 Cortex-M 系列的常规行为):悬起位会被置位,但要等到当前中断函数执行完毕、退出时,才会检测并响应该悬起位。

-

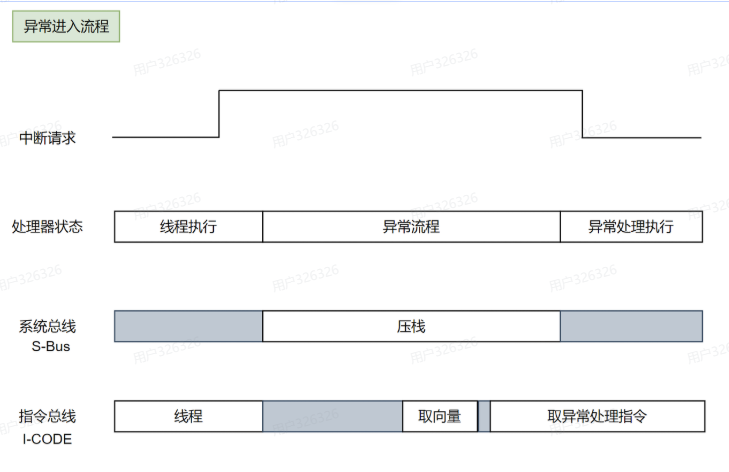

五、异常流程(压栈)

-

当中断请求后,有一段延迟,然后从原先的线程执行到异常流程

-

首先,数据总线他会压栈,会把一些寄存器压入栈中

-

指令总线就回去向量表,取向量,通过向量找到异常处理指令

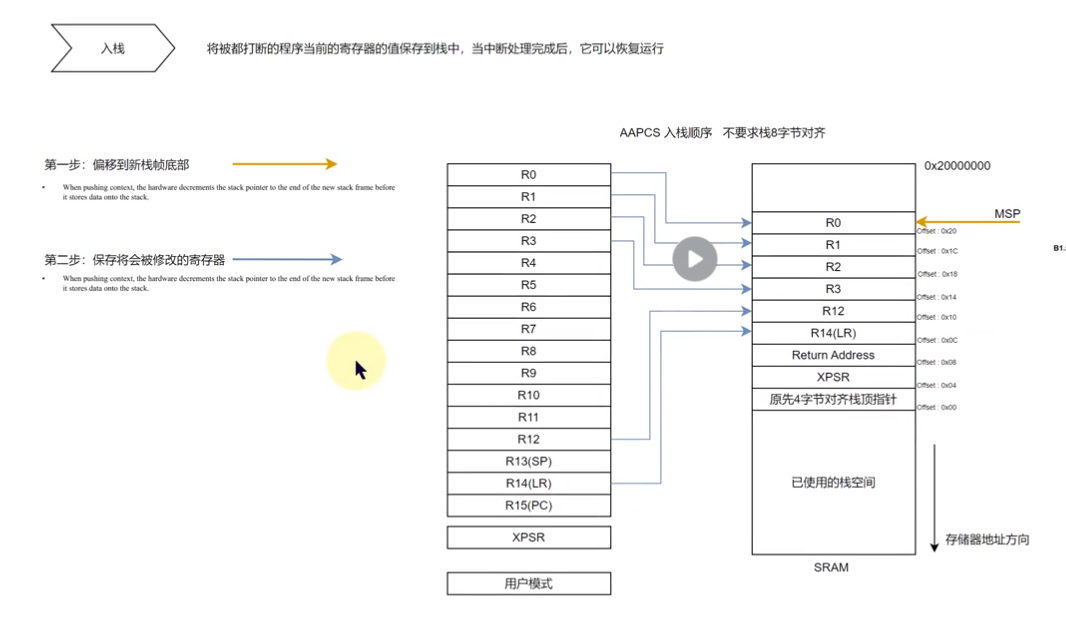

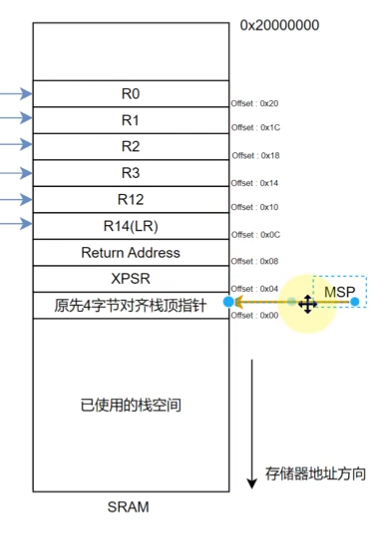

入栈流程

-

当发生中断,当前运行的寄存器会被依次压入栈中

-

假设只有一个主栈帧,现在运行到如图所示地方,来中断后,会直接回到最上边栈底(R0),并存入了R1-R3,R12和R14,因为要回到原来程序,还得保存pc指针。其中LR的值会被考入到栈中,而寄存器里面的lr的值会变为EXC_RETURN,详情可见.调用栈和fault analyzers(快速找到bug)

-

压栈是通过S-Bus进行压栈

-

I-code就可以进行访问对应的flash区,找到对应的异常处理函数

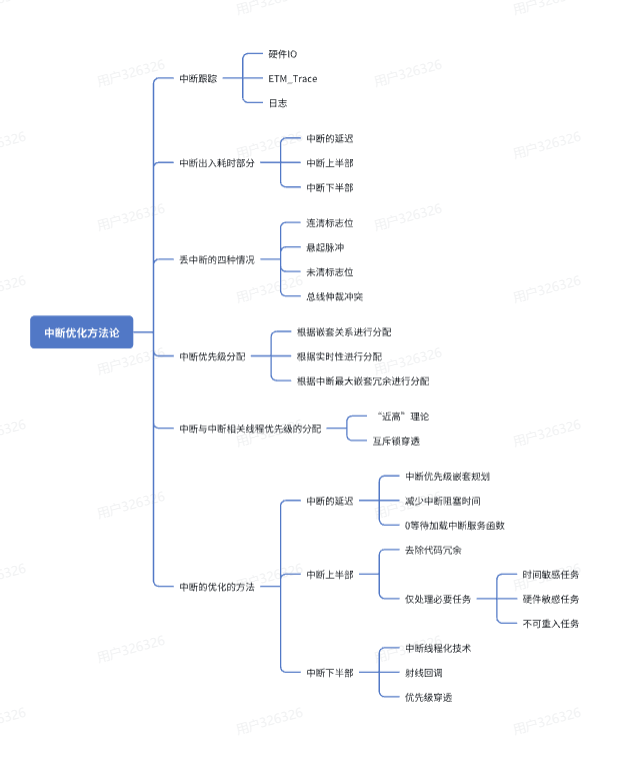

六、中断优化

A:一般来说 进中断后不是要先判断标志位,然后再清楚标志位吗 难道这个标志位有时候是外设自己的挂起寄存器 有些是nvic的标志位

在中断处理流程中,外设自身的挂起寄存器标志位 和NVIC 的 pending 位是两个不同层级的概念,处理逻辑也有所区别,具体可以从以下角度梳理:

一、中断产生的 "两层标志" 逻辑

中断请求的产生是 "外设→NVIC→CPU" 的层级传递:

-

外设层 :外设(如 EXTI、定时器、USART)先产生中断事件,将自身的挂起标志位置 1(如 EXTI_PR 的某一位、TIMx_SR 的 UIF 位)。

-

NVIC 层 :外设的中断请求被传递到 NVIC 后,NVIC 对应通道的pending 位置 1,表示 "该中断已被 NVIC 受理,等待 CPU 响应"。