以下内容主要由AI生成,稍加整理如下:

在 Cortex-M3 中,xPSR(程序状态寄存器)是一个至关重要的32位特殊功能寄存器,它由三个子寄存器组合而成,分别负责记录不同的处理器状态信息。

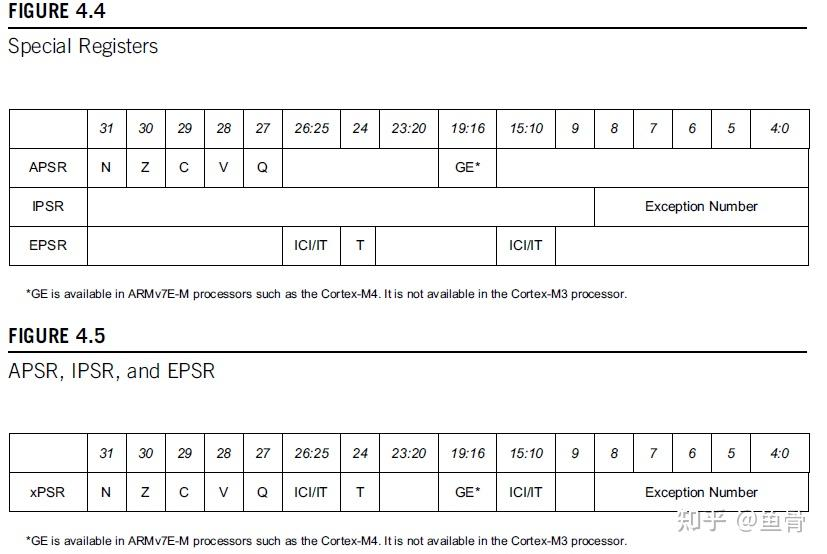

下表清晰地展示了 xPSR 的整体结构和各个位的含义。

| 位域 | 名称 | 功能描述 |

|---|---|---|

| 31 | N (Negative) | 负标志。运算结果为负数时置1。 |

| 30 | Z (Zero) | 零标志。运算结果为零时置1。 |

| 29 | C (Carry) | 进位/借位标志。无符号数加法产生进位或减法未产生借位时置1。 |

| 28 | V (Overflow) | 溢出标志。有符号数运算发生溢出时置1。 |

| 27 | Q (Saturation) | 饱和标志。当DSP指令发生饱和操作时置1。 |

| 26:25, 15:10 | ICI/IT | 中断继续指令/IF-THEN 块状态。用于中断继续执行或条件指令块的状态保存。 |

| 24 | T (Thumb) | Thumb状态位。必须为1,尝试清除此位将引发错误异常。 |

| 8:0 | Exception Number | 异常编号。记录当前正在处理的中断或异常的编号。 |

🔍 深入理解三个子寄存器

xPSR 的三个子寄存器可以单独或组合访问,它们各司其职:

-

算术运算用程序PSR (APSR) :这是程序的"晴雨表",主要包含上表中的 N、Z、C、V、Q 标志位。这些标志位由算术逻辑单元(ALU)根据运算结果自动设置,是条件分支指令(如

BGT,BLE)的判断依据。你可以通过MRS R0, APSR和MSR APSR, R0指令读写此寄存器。 -

中断PSR (IPSR) :这是异常处理的"导航仪",它是只读的。它存储了当前正在处理的中断或异常的编号(例如,复位为1,SysTick为15,IRQ从16开始)。在中断服务程序中,可以通过读取此编号来判断中断源。

-

执行PSR (EPSR) :这是指令执行的"状态锁",它也是只读的,软件无法直接写入。它包含:

-

T位:Cortex-M3 只支持 Thumb-2 指令集,因此该位恒为1。

-

ICI/IT位 :用于复杂场景,例如当一条多周期指令(如多个寄存器的加载/存储)被中断打断时,硬件会利用ICI位记录执行进度,以便中断返回后能继续执行;IT位则用于支持

IF-THEN条件指令块。

-

💻 如何访问xPSR

你可以通过 MRS(读)和 MSR(写)指令来访问xPSR。

; 组合访问整个xPSR

MRS R0, PSR ; 将整个xPSR的值读取到R0中

MSR PSR, R0 ; 将R0的值写入xPSR

; 单独访问子寄存器

MRS R0, APSR ; 读取APSR到R0

MRS R0, IPSR ; 读取IPSR到R0(只读)

MSR APSR, R0 ; 将R0的值写入APSR在C语言中,使用CMSIS-Core库提供的函数(如 __get_IPSR())可以更方便地操作这些寄存器。

为了让你更清晰地理解它的独特设计,下面这个表格详细解析了xPSR的三个组成部分及其分工。

| 子寄存器 | 主要功能 | 关键位域与描述 |

|---|---|---|

| **应用程序PSR (APSR)** | 存储算术逻辑单元(ALU)运算后的状态标志,是程序条件判断(如循环、分支)的直接依据。 | N (负标志)、Z (零标志)、C (进位/借位标志)、V (溢出标志)、Q (饱和标志) |

| **中断PSR (IPSR)** | 只读 寄存器,存储处理器当前正在服务的中断或异常的编号。 | 异常编号 (位域0-8):0=线程模式(无异常),1-15=系统异常(如Reset、SVCall),≥16=外部中断(IRQ)。 |

| **执行PSR (EPSR)** | 只读 寄存器,指示处理器当前的执行状态,软件无法直接写入。 | T位 (位24):Thumb状态位,Cortex-M3必须为1,清除它会引发错误。 ICI/IT位:用于中断继续和IF-THEN指令块的状态保存。 |

💡 深入理解xPSR的特性

除了上述基本结构,理解以下几点能帮助你更好地掌握xPSR:

-

灵活的访问方式 :xPSR的三个子寄存器既可以单独访问 ,也可以组合访问。

-

单独访问 :适用于只需修改或检查特定标志的场景,例如,在C语言中可以使用

__get_APSR()函数来读取APSR中的标志位。 -

组合访问 :使用

MRS R0, PSR指令可以一次性读取整个xPSR的值,这在需要完整保存程序状态时非常高效。

-

-

访问权限限制:这是确保系统稳定性的关键设计。

-

APSR 在特权和非特权(用户)模式下通常均可访问。

-

IPSR 和 EPSR 则通常仅限于在特权模式下访问(例如在操作系统内核或异常处理程序中),这防止了用户应用程序随意修改或读取关键的执行状态。

-

-

与传统PSW的对比 :相比于一些经典架构(如x86或8051)中单一、结构固定的PSW,xPSR的模块化设计是一大进步。这种设计使得状态管理更加清晰,不同功能模块(应用状态、异常处理、执行控制)各司其职,提高了架构的灵活性和可维护性。

💎 总结

简单来说,xPSR就是Cortex-M3的程序状态字 ,它通过APSR、IPSR、EPSR这三个子寄存器的组合,分别承担了传统PSW中结果状态记录、异常处理导航和指令执行控制的核心职能。这种模块化设计是其最显著的特点。