光耦加PNP管驱动继电器

- 1.前言

-

- 1.1 光耦加PNP VS 光耦加NPN

- 1.2 光耦加PNP 驱动原理

-

- 光耦加PNP驱动波形

-

- 2.1分析

- 2.2建议电路

-

- 总结

1.前言

之前都是用NPN管驱动继电器,现在接触到一个项目用光耦加PNP管驱动继电器。那么这样的电路优缺点在哪?

1.1 光耦加PNP VS 光耦加NPN

| 对比维度 | 光耦+PNP | 光耦+NPN |

|---|---|---|

| 驱动电源要求 | 光耦输出侧电源(Vc) ≥ 继电器电源(Vcc) | 光耦输出侧电源(Vc)可独立且任意 |

| 安全性 | 继电器线圈接在集电极和地之间,断电更安全 | 继电器线圈接在集电极和VCC之间 |

| 电路复杂性 | PNP管种类少,复杂 | NPN管种类多,简单 |

| 抗干扰性 | 强 | 弱 |

1.2 光耦加PNP 驱动原理

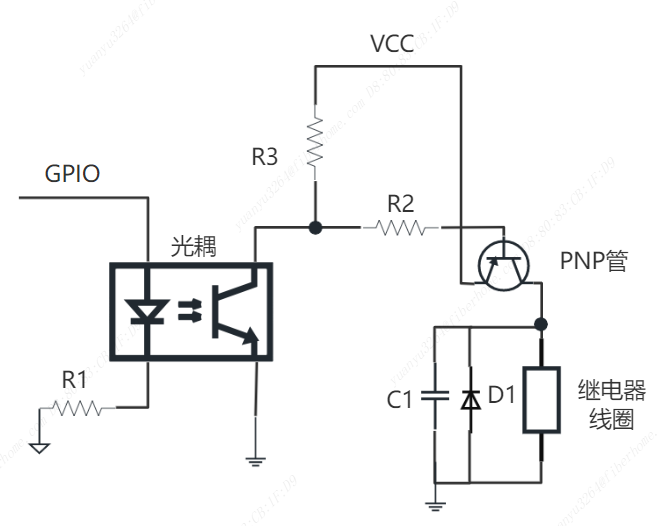

GPIO来自于CPU,光耦以HCPL-653K为例,CTR为20%左右。R1初始值100Ω,R2、R3初始值1K,VCC初始值11V。

原理:GPIO输出高电平3.3V时,光耦里的二极管导通发光,使得光耦三极管导通,PNP管由于基极电压被拉低,发射极为VCC,使得其导通,继电器线圈通电。D1作用是保证线圈断电时,有电流泄放回路。C1的作用是在继电器线圈通断电瞬间,抑制高频噪声,优化EMI,值可以选0.01uf~0.1uF,当要求没那么高时,这个电容不是必须要加的。

2. 光耦加PNP驱动波形

2.1分析

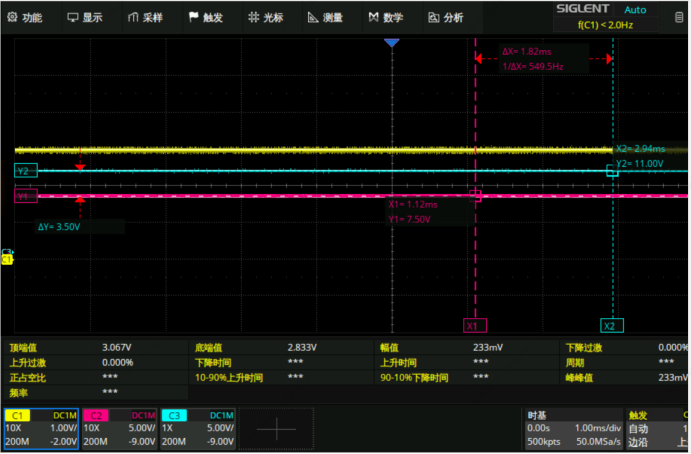

ch1:GPIO(光耦输入)

ch2: 光耦集电极输出

ch3:三极管集电极输出(继电器线圈两端电压)

初始态,光耦输出为7.5V

根据分析,理想情况下,光耦集电极输出为0V,PNP管输出为11V左右,目前,光耦的输出跟理论有差异,那问题到底出现在哪?

第一想法是,光耦的二极管驱动电流不足,但是经计算和测试,电流为15mA,完全满足光耦要求。

然后怀疑上拉电阻R3,是不是太小。

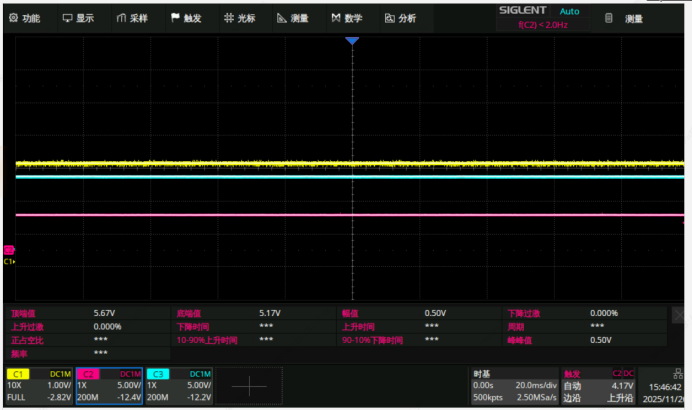

更改上拉电阻至10k,光耦输出5.2V左右,也不能解决问题。

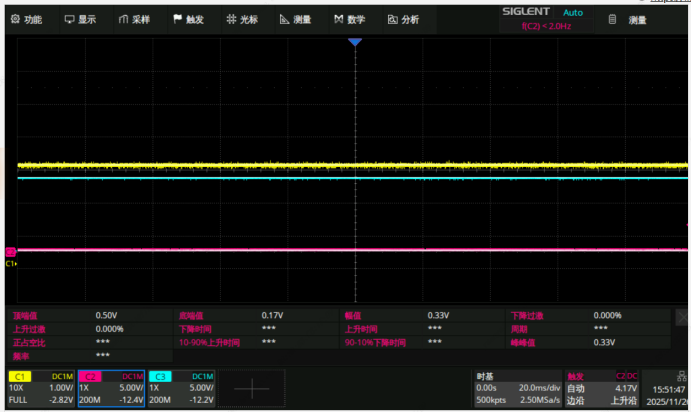

怀疑到光耦坏了,都没怀疑三极管基极电阻的影响。经过仿真发现,同时更改上拉电阻和基极电阻至10k,光耦输出可以将之0.

原因在于,当光耦二极管导通时,电流为15mA,经过CTR计算,光耦三极管饱和导通电流为15mA*20%=3mA,说明光耦最大只能提供3mA电流 。而上拉1k电阻需要11V/1k=11mA电流,和基极电阻常规需要(11V-0.7V)/1k=10.3mA电流,加起来21.3mA电流,跟光耦提供电流能力不匹配,电路只能达到一个平衡,光耦输出一个中间电压7.5V。

当输出7.5V时,R3电阻电流为3.5mA,R2电流为2.8mA,光耦通过电流为6.3mA,这与最大3mA输出有点矛盾,但是我在手册中看到的CTR是有限定条件的,是饱和导通时的值,有可能光耦在非饱和导通时CTR要大,再看手册的传输特性曲线,If一定时,光耦三极管输出电压越大输出电流越大,说明CTR越大。当然图里的VCC电压对应不上,只能这样猜想。

2.2建议电路

建议R3放在R2之后上拉,代替此电路中两个电阻同时接光耦三极管的集电极。

好处是,两个电阻分工明确,R3的作用:仅保证PNP可靠截止R3可以很大(47k-100k),功耗极小

R2的作用:提供基极驱动电流两者分工明确,无矛盾。

而之前电路的坏处是:一方面希望R3大些,减少功耗

但实际R3太大会导致光耦无法可靠拉低,另一方面R3太小会增加光耦电流负担矛盾。

3. 总结

光耦加pnp驱动电路设计时要注意光耦三极管的上拉电阻和pnp基极电阻的设计。

当拿到别人设计的电路图时,很容易想当然的认为应该怎样,实际还是要从理论计算出发。