FPGA教程系列-Vivado AXI4-Lite接口

AXI-Lite

声明:如有雷同,纯属抄袭。

特点

其他的就不赘述了,之前研究过。

AXI4-Lite总线协议的特性如下:

- 事务传输突发长度为1

- 每次传输只能传输一个数据

- 所有访问都是不可修改(Non-modifiable),不可缓冲(Non-bufferable)

- 不支持专属访问(Exclusive access)

AXI4-Lite比起AXI4-Full总线来说,由于每次只传输一个收据,传输效率低了很多。比较适用的场景是单次访问某个寄存器(地址寻址),类似于IIC总线的单次读写。在SOC系统或者 ZYNQ 中比较常用。

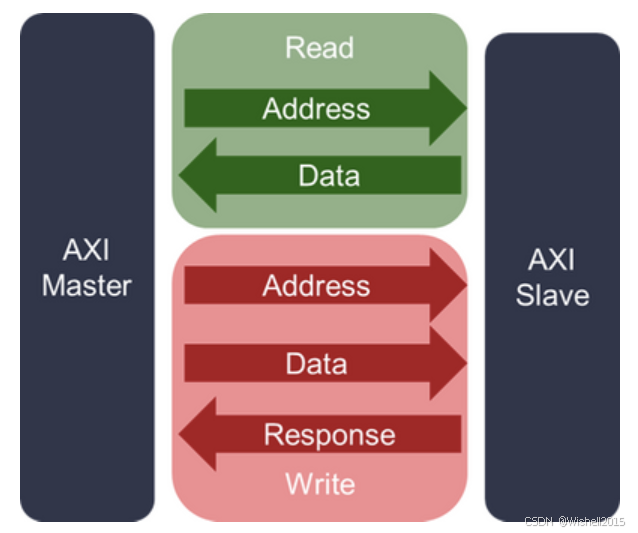

通道

AXI4-Lite定义了 5 条通道:

写操作(3个通道)

- 写地址通道 (Write Address Channel - AW): 告诉从机(Slave)我要写哪个地址。

- 写数据通道 (Write Data Channel - W): 发送实际的数据。

- 写响应通道 (Write Response Channel - B): 从机告诉主机(Master),"我写完了,状态是 OK 还是 Error"。

读操作(2个通道)

- 读地址通道 (Read Address Channel - AR): 告诉从机我要读哪个地址。

- 读数据通道 (Read Data Channel - R): 从机把数据和状态返回给主机。

AXI 是基于通道(Channel) 的协议。可以把通道想象成单行道,数据和控制信号在上面流动。

AXI 读取传输 (Read Transaction)流程: "我要读这个地址" -> "给你数据"

- 发地址 (M -> S): 主机(Master)通过 读地址通道 (AR) 告诉从机(Slave):"我要读地址

0x1000开始的数据"。 - 收数据 (S -> M): 从机通过 读数据通道 ® 把数据传回给主机。

关于"突发 (Burst)":

- AXI4-Lite (无突发): 你告诉店员"我要买苹果",店员给你一个苹果。交易结束。如果你还要买,得再喊一次。

- AXI4-Full (支持突发): 你告诉店员"我要买苹果,来一箱(比如16个)"。你只说了一次地址(请求),店员会连续给你递 16 个苹果。这就是突发。

AXI 写入传输 (Write Transaction)流程: "我要写这个地址" -> "这是数据" -> "写好了"

- 发地址 (M -> S): 主机通过 写地址通道 (AW) 告诉从机:"我要往地址

0x2000写数据"。 - 发数据 (M -> S): 主机通过 写数据通道 (W) 把具体的数据发过去。

- 收回执 (S -> M): 从机写完后,通过 写响应通道 (B) 告诉主机:"任务完成(OKAY)"或者"出错了(ERROR)"。

为什么写需要 3 条通道,读只要 2 条?效率与带宽利用。

-

写操作 (Write): 数据是发往从机的。数据发完了,主机怎么知道从机是不是真的写进去了?所以必须有一个专门的通道(写响应通道 B)来回传一个"回执单"。

-

读操作 (Read): 数据是从从机回来的。

既然从机已经在发数据了,为什么不顺便把"状态(Status)"贴在数据旁边一起发回来呢? 在读数据通道 ® 中,除了

RDATA (数据线),还有一组信号叫RRESP(读响应)。

握手信号:VALID 和 READY, 这是 AXI 的灵魂,所有通道都有这就两根线。

- VALID (我好了): 发送方说"我的数据/地址已经准备好了,放在线上了"。

- READY (我没忙): 接收方说"我有空,可以接收数据了"。

- 机制: 只有当 VALID=1 且 READY=1 的那个时钟上升沿,数据才算真正传输成功。缺一不可。

握手的时序,与AXI-Stream一致,不再赘述。

写数据通道的"STROBE"信号,也与AXI-Stream一致

假设数据总线是 32位(4个字节,Byte 0 ~ Byte 3),地址是对齐的。

如果你只想修改这个 32位整数中的第 3 个字节,而保持其他 3 个字节不变,该怎么办?

-

没有 Strobe: 你必须先读出这 32位,修改第 3 个字节,然后再把 32位全写回去(读-改-写),效率很低。

-

有 Strobe (WSTRB):

WSTRB是一个 4位的信号(对应 4个字节)。- 如果你设

WSTRB = 4'b0100,表示"只写第 3 个字节,其他字节不管"。 - 从机收到后,就只会更新那一个字节。这就是掩码(Mask) 功能。

信号列表详解

假设数据位宽为 32位,地址位宽为 32位,以下是标准信号:

全局信号

ACLK: 时钟信号,所有信号在上升沿采样。ARESETN: 复位信号,低电平有效。

写地址 (Write Address - AW)

| 信号名 | 方向 (M->S) | 描述 |

|---|---|---|

AWVALID |

M -> S | 主机:地址有效 |

AWREADY |

S -> M | 从机:准备好接收地址了 |

AWADDR |

M -> S | 写入的目标地址 (例如 0x4000_0000) |

AWPROT |

M -> S | 保护类型(通常接 0 或忽略) |

写数据 (Write Data - W)

| 信号名 | 方向 (M->S) | 描述 |

|---|---|---|

WVALID |

M -> S | 主机:数据有效 |

WREADY |

S -> M | 从机:准备好接收数据了 |

WDATA |

M -> S | 实际数据 (例如 0x0000_0001) |

WSTRB |

M -> S | 写选通 (Write Strobe) :字节有效位。对于 32位数据,4bit 宽。4'b1111 表示全写,4'b0001 表示只写最低字节。 |

写响应 (Write Response - B)

| 信号名 | 方向 (M->S) | 描述 |

|---|---|---|

BVALID |

S -> M | 从机:响应有效 |

BREADY |

M -> S | 主机:准备好接收响应了 |

BRESP |

S -> M | 响应状态(00=OKAY, 10=SLVERR, 11=DECERR) |

读地址 (Read Address - AR)

| 信号名 | 方向 (M->S) | 描述 |

|---|---|---|

ARVALID |

M -> S | 主机:读地址有效 |

ARREADY |

S -> M | 从机:准备好接收读地址了 |

ARADDR |

M -> S | 读取的源地址 |

ARPROT |

M -> S | 保护类型 |

读数据 (Read Data - R)

| 信号名 | 方向 (M->S) | 描述 |

|---|---|---|

RVALID |

S -> M | 从机:读数据有效 |

RREADY |

M -> S | 主机:准备好接收读数据了 |

RDATA |

S -> M | 读到的数据 |

RRESP |

S -> M | 读响应状态(数据是否读成功) |

在 Zynq 里,用 AXI-Lite 让 ARM 指挥 FPGA (改参数),用 AXI-Stream 让 FPGA 处理数据 (FFT),用 AXI-Full 让 FPGA 存取内存 (DMA)。