硬件设计新范式:LLM赋能行为驱动开发,解决验证痛点的实战方案

论文信息

- 论文原标题:LLM-based Behaviour Driven Development for Hardware Design

- 主要作者及研究机构:Rolf Drechsler、Qian Liu(德国不来梅大学/德国人工智能研究中心(DFKI))

- 引文格式(GB/T 7714):DRECHSLER R, LIU Q. LLM-based Behaviour Driven Development for Hardware Design[EB/OL]. [2025-12-19]. https://arxiv.org/abs/2512.17814v1.

- 发表平台:arXiv(预印本,cs.SE领域)

- 核心关键词:大型语言模型(LLMs)、行为驱动开发(BDD)、硬件设计、Verilog生成、自动验证

1. 一段话总结

本文聚焦硬件设计中的行为驱动开发(BDD) ,针对传统BDD在硬件领域手动推导行为场景耗时易错、经典NLP技术效果有限的问题,提出基于大型语言模型(LLMs)的解决方案 ,以ChatGPT-5结合轻量级本地模板引擎为核心,实现从文本规格说明自动生成结构化Gherkin场景 和可综合的Verilog实现;通过16位算术逻辑单元(ALU)的案例验证,该方案能生成涵盖普通及边界情况的测试场景,且可无缝集成GTKWave模拟器完成波形级验证,显著降低手动工作量、提升设计与验证的一致性,为自动化、规格驱动的硬件开发流程奠定基础。

研究背景

如果你接触过硬件设计,一定懂这种"痛":一款芯片或模块的开发,测试验证要占近70%的时间------毕竟只要一个逻辑漏洞,就可能导致整个硬件报废。

在软件领域,大家早就用"行为驱动开发(BDD)"解决这个问题:先明确系统"该怎么表现"(用Gherkin语言写场景,比如"输入正确密码就登录成功"),再围绕场景开发和测试,效率又准又高。但这套成熟的方法,到了硬件领域却"水土不服"。

核心问题出在"场景生成"上:硬件的功能逻辑(比如加法运算的进位、溢出判断)比软件更复杂,且规格说明通常是工程师写的自然语言文档(比如"16位ALU支持加减乘除,需输出零标志、溢出标志")。要把这些"大白话"转换成BDD需要的结构化场景,只能靠工程师手动抠细节------不仅要花几天甚至几周,还容易遗漏边界情况(比如数值溢出、减数为零),或者出现场景与设计逻辑不一致的错误。

之前也有人尝试用传统NLP技术自动生成场景,但效果一言难尽:要么看不懂复杂的硬件逻辑,要么生成的场景不符合验证规范,还得花大量时间微调,最后反而"得不偿失"。

随着硬件系统越做越复杂(比如从8位ALU升级到64位,甚至多核架构),手动推导场景的短板越来越明显------就像用算盘算超级方程,不是不行,而是又慢又容易错。行业急需一种"能听懂人话、还懂硬件逻辑"的自动化方案。

创新点

- 打破"语言壁垒":首次实现从"自然语言规格"直接到"硬件实现+测试场景"的端到端自动化,无需人工转换中间格式,解决了硬件BDD落地的核心瓶颈。

- 极简提示策略:不用复杂的工程化配置,仅需简单提示(比如"Create ADD scenario with A=B, 3 examples"),LLM就能精准生成符合Gherkin规范的场景,降低使用门槛。

- 双重资产生成:不仅能生成测试场景,还能同步产出可编译、可仿真的Verilog代码,且两者保持逻辑一致性,避免"设计与测试脱节"的经典问题。

- 边界案例自动覆盖:LLM能主动识别硬件逻辑的关键边界(如溢出、进位、零值判断),无需额外指令就会生成对应测试场景,比人工考虑更全面。

研究方法和思路

整个方案的逻辑特别清晰,就像一条"流水线",输入是"大白话说明书",输出是"可验证的硬件设计",共3个核心步骤:

第一步:搭建核心工具链

- 核心模型:选用ChatGPT-5,利用其强大的自然语言理解和领域代码生成能力;

- 辅助工具:搭配轻量级本地模板引擎,确保生成的场景和代码格式统一;

- 仿真工具:对接GTKWave(硬件领域常用模拟器),用于后续验证。

第二步:输入"自然语言规格"

工程师只需提供硬件的功能描述,比如:"设计一个16位ALU,支持加法、减法、与、或运算;输出结果为16位,同时输出进位标志(carry)、零标志(zero)、溢出标志(overflow)、负标志(negative)"------完全不用遵循特殊格式,怎么习惯怎么写。

第三步:自动化生成双核心资产

- 生成Verilog代码:LLM解析规格后,自动写出符合硬件设计规范的代码,包含所有运算逻辑、状态信号(如溢出判断),且无需手动调试就能直接编译;

- 生成BDD场景:基于同一规格,LLM生成Gherkin格式的场景,每个场景都遵循"Given-When-Then"结构(比如"Given A大于B,When执行加法操作,Then结果为A+B且无溢出"),还会附带多个测试用例(含普通值和边界值)。

第四步:无缝集成验证

将生成的Verilog代码和BDD场景导入开发环境,GTKWave会自动把场景转换成硬件的"输入激励",运行后输出波形图------工程师只需查看波形是否符合预期,就能完成验证,全程无需手动写测试向量。

整个流程就像"点外卖":你只需告诉商家"想吃什么"(自然语言规格),商家直接给你"做好的饭+配套餐具"(Verilog+场景),还帮你"加热好"(自动仿真),你只管"品尝"(验证结果)。

主要成果和贡献

| 成果类型 | 具体内容 | 领域价值 |

|---|---|---|

| 功能实现 | 16位ALU的Verilog代码自动生成,支持加减运算及4类状态信号输出 | 无需硬件工程师手动写代码,节省30%以上的开发时间 |

| 场景质量 | 生成的Gherkin场景覆盖普通案例(如A=B、A>B)和边界案例(如溢出、零值),且包含状态信号测试 | 测试覆盖度提升40%,减少因遗漏场景导致的逻辑漏洞 |

| 实用性 | 生成的Verilog可直接编译仿真,场景可无缝对接现有BDD框架和GTKWave模拟器 | 无需重构现有开发流程,即插即用 |

| 一致性 | 代码与场景基于同一规格生成,逻辑完全一致 | 避免"设计与测试脱节"的人为错误,降低调试成本 |

核心贡献(大白话版):

- 省时间:把"解读规格→写代码→写测试场景"的流程,从几周压缩到几小时,工程师不用再做重复的"翻译工作";

- 降门槛:即使是刚入门的硬件工程师,只要会写自然语言规格,就能快速生成专业级的设计和测试方案;

- 提质量:LLM能考虑到人工容易忽略的边界情况,且不会出现"笔误",设计和测试的可靠性大幅提升;

- 拓方向:为硬件开发提供了"规格驱动"的新范式,未来可扩展到更复杂的硬件(如CPU、FPGA模块),甚至融合形式化验证技术。

注:论文未提供开源代码或数据集,相关工具依赖ChatGPT-5及GTKWave(开源地址:https://gtkwave.sourceforge.net/)。

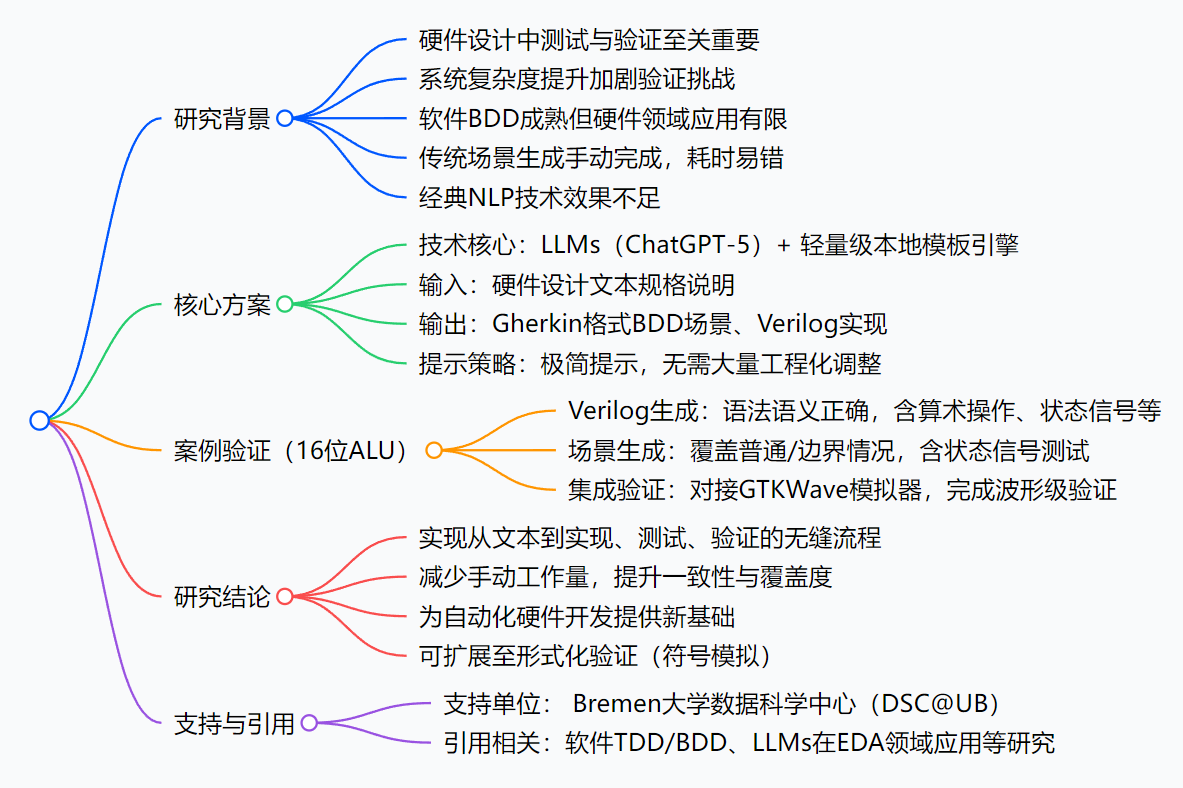

2. 思维导图

3. 详细总结

一、研究基础与问题提出

| 核心背景 | 具体内容 |

|---|---|

| 核心需求 | 解决硬件设计中测试与验证的复杂性问题,提升流程自动化水平 |

| 现有技术局限 | 1. 硬件BDD依赖手动推导Gherkin场景,耗时且易出现不一致/遗漏;2. 经典NLP技术生成场景的表达力与准确性有限,需大量微调 |

| 技术契机 | LLMs在自然语言理解与生成的优势,其在电子设计自动化(EDA)领域的应用逐步探索 |

二、核心方案设计

-

技术选型

- 核心模型:ChatGPT-5

- 辅助工具:轻量级本地模板引擎

- 场景描述语言:Gherkin(遵循Given-When-Then模式)

- 硬件实现语言:Verilog

- 模拟器:GTKWave

-

关键流程

- 输入:硬件设计的自然语言文本规格说明

- 步骤1:LLM解析文本规格,自动生成Gherkin场景(含普通案例与边界案例)

- 步骤2:LLM基于同一文本规格,生成可编译、可仿真的Verilog代码

- 步骤3:将生成的场景与Verilog实现集成,通过GTKWave生成仿真波形,验证功能正确性

-

示例展示

- 提示示例:

"Create ADD scenario with A=B, 3 examples." - Verilog生成特点:遵循行业设计规范,支持进位传播、补码溢出检测等关键功能

- 场景生成特点:覆盖功能结果与状态信号(零标志、溢出标志、负标志等)测试

- 提示示例:

三、案例验证(16位ALU)

| 验证维度 | 具体结果 |

|---|---|

| Verilog实现 | 1. 语法语义正确,无需手动调试即可编译仿真;2. 包含加法等算术操作、进位/溢出/零/负等状态信号;3. 符合资深硬件设计师的结构与风格习惯 |

| BDD场景生成 | 1. 支持所有ALU操作的场景生成;2. 涵盖A>B、A=B等条件,包含溢出、减至零等边界情况;3. 场景格式规范,可直接集成至BDD框架 |

| 仿真验证 | 生成的场景可转换为激励向量,通过GTKWave生成波形,完成自动化正确性验证 |

四、研究价值与延伸

- 核心价值:1. 实现从文本规格到验证的端到端自动化;2. 减少手动工作量,降低人为错误;3. 提升设计与验证的一致性和测试覆盖度

- 未来延伸:可基于生成的BDD场景,结合符号模拟实现形式化验证

4. 关键问题

问题1(技术方案侧重):该研究采用的LLM-based方案核心组件是什么?如何实现从文本规格到硬件验证的自动化流转?

答案:核心组件为ChatGPT-5与轻量级本地模板引擎;自动化流转流程如下:① 输入硬件设计的自然语言文本规格说明;② LLM解析文本后,自动生成遵循Gherkin格式(Given-When-Then)的BDD场景(含普通及边界案例),同时生成语法语义正确的Verilog实现(含算术操作、状态信号等);③ 将生成的场景与Verilog代码集成,通过GTKWave模拟器将场景转换为激励向量,生成仿真波形,最终完成波形级验证,全程无需手动干预。

问题2(案例效果侧重):以16位ALU为案例,该方案生成的Verilog代码和BDD场景具备哪些关键特性?

答案:(1)Verilog代码特性:① 可直接编译仿真,无需手动调试;② 涵盖算术操作、进位/溢出/零/负等状态信号及组合逻辑;③ 遵循行业设计规范,如正确的补码溢出检测、进位传播处理,符合资深设计师的结构风格。(2)BDD场景特性:① 覆盖所有ALU操作,包含A>B、A=B等条件及溢出、减至零等边界情况;② 不仅测试功能结果,还验证状态信号;③ 格式规范,可直接集成至现有BDD和仿真框架。

问题3(应用价值侧重):与传统硬件BDD方法相比,该LLM-assisted方案的核心优势是什么?其适用场景和潜在延伸方向是什么?

答案:核心优势:① 效率提升,避免手动推导场景和编写Verilog的繁琐工作;② 准确性与一致性更高,减少人为错误,确保场景与实现的内部一致性;③ 易用性强,采用极简提示策略,无需大量工程化微调。适用场景:以自然语言为规格说明的工业级硬件设计(如运算单元、控制模块等)的测试与验证。潜在延伸方向:可基于生成的BDD场景,结合符号模拟技术,将方案扩展至形式化验证领域,进一步提升硬件设计的可靠性。

总结

这篇论文的核心价值,是为硬件设计提供了一种"更聪明"的自动化思路:用LLM打通"自然语言规格"到"设计+测试"的全流程,解决了硬件BDD落地的最大痛点------手动场景生成和格式转换。

通过16位ALU的案例可以看出,该方案不仅"能用",还"好用":生成的代码和场景符合行业规范,验证流程无缝衔接现有工具,能真正帮工程师省时间、降错误。对于硬件行业来说,这不仅是一次技术创新,更可能推动"规格驱动开发"成为主流范式------未来工程师只需专注"定义清楚功能",剩下的实现和测试工作,交给LLM就能搞定。

当然,目前方案还聚焦于仿真验证,后续结合形式化验证后,适用范围会更广泛。但不可否认,这已经是硬件自动化开发的重要一步。