FPGA教程系列-Vivado AXI4-Full接口

换换脑子,回过头来再看看AXI-Full协议,概念就不在唠叨了,反正就是AXI有三种,这个是最全乎的。

多出来一个总线的概念:

一般情况下,AXI4-Full总线也被直接简称为AXI4总线。AXI4-Full、AXI4-Lite都是内存映射型总线(需要地址),其是多主多从的拓扑结构,可通过Interconnect(AXI4交换设备)来进行互联。具体到XILINX的AXI4应用,一般使用这两个IP来进行多主多从的AXI接口互联:AXI Interconnect(一般使用这个)、AXI SmartConnect。 拓扑结构图如下:

通道与AXI-Lite一致,其实有个事务的概念比较模糊,所以学习下,为什么读,写都叫做事务。

传输事务

传输事务(Transaction)是指一次完整的、不可分割的读写操作过程。

在 AXI 协议中,仅仅发送一个地址,或者仅仅发送一个数据,都不能算作一个事务。事务是这些步骤的组合。

"Transaction"这个词最初大量用于商业 和数据库领域(比如银行转账),引入到电子工程和总线协议中非常贴切,原因如下:

A. 强调"完整性" (Completeness)

在商业中,一手交钱一手交货才叫一个 Transaction。如果你给了钱(发送了写数据),但对方没给你收据(没有写响应),这笔交易就不算完成。

在 AXI 中,使用"事务"这个词是为了强调:地址、数据、响应虽然是在不同的通道(Channel)上独立传输的,但它们在逻辑上是一个整体。 缺少任何一个环节,这个操作就是失败的。

B. 强调"解耦"与"逻辑关联"

早期的简单总线(如 SPI 或简单的 SRAM 接口),地址线和数据线是绑定在一起的,发地址的同时必须发数据。

而在 AXI 这种高级协议中,通道是独立的。

- 可以先发地址,过一会再发数据。

- 可以连续发 10 个写地址(10 个写事务的开头),然后再慢慢发这 10 个事务的数据。

- 为什么不会乱? 因为这些分散在不同时间、不同通道上的动作,都属于特定的"事务"。系统通过 ID(Transaction ID)把它们关联起来。

C. 区分"一次操作"与"一次传输" (Burst vs Beat)

- Beat (拍/传输): 时钟跳一下,传送一个数据(例如 32-bit)。

- Burst (突发): 一次"事务"可以包含很多个"Beat"。比如我发一个地址,要求读 1KB 的数据,这可能需要传送 256 次数据(Beat)。

- Transaction (事务): = 1 个地址请求 + N 次数据传输 (Burst) + 1 次响应。

什么是突发?

再说个题外话,看到突发,总是不太理解,为什么要用这个词,再理解一下

- 什么是突发(Burst)?用一句话概括: "突发"就是"给一个首地址,连续传一堆数据"。

在没有突发模式(Single mode)的旧式总线中,传输数据是这样的:

- 发送地址 A -> 传输数据 D1

- 发送地址 A+1 -> 传输数据 D2

- 发送地址 A+2 -> 传输数据 D3

...

(发 1 个数据就要喊 1 次地址,非常啰嗦)

而在 AXI 等现代总线的突发模式(Burst mode) 中,传输是这样的:

- 发送首地址 A,并告诉对方:"我要从这里开始,连续拿 4 个数据"。

- 传输数据 D1

- 传输数据 D2

- 传输数据 D3

- 传输数据 D4

(只喊 1 次地址,后面数据就像连珠炮一样发过来,不需要再给地址了)

在 AXI 协议中,Slave(从机)会自动计算下一个地址(比如传完地址 0x00,它知道下一个是 0x04,再下一个是 0x08,以此类推),直到传完指定数量的数据。

基本解释清楚了,就是一个连续的数据的传输,至于为什么叫突发,为了形容数据传输的形态 和速度。类似的比喻是机关枪的连射模式。一顿突突突,对面就挂一大片。

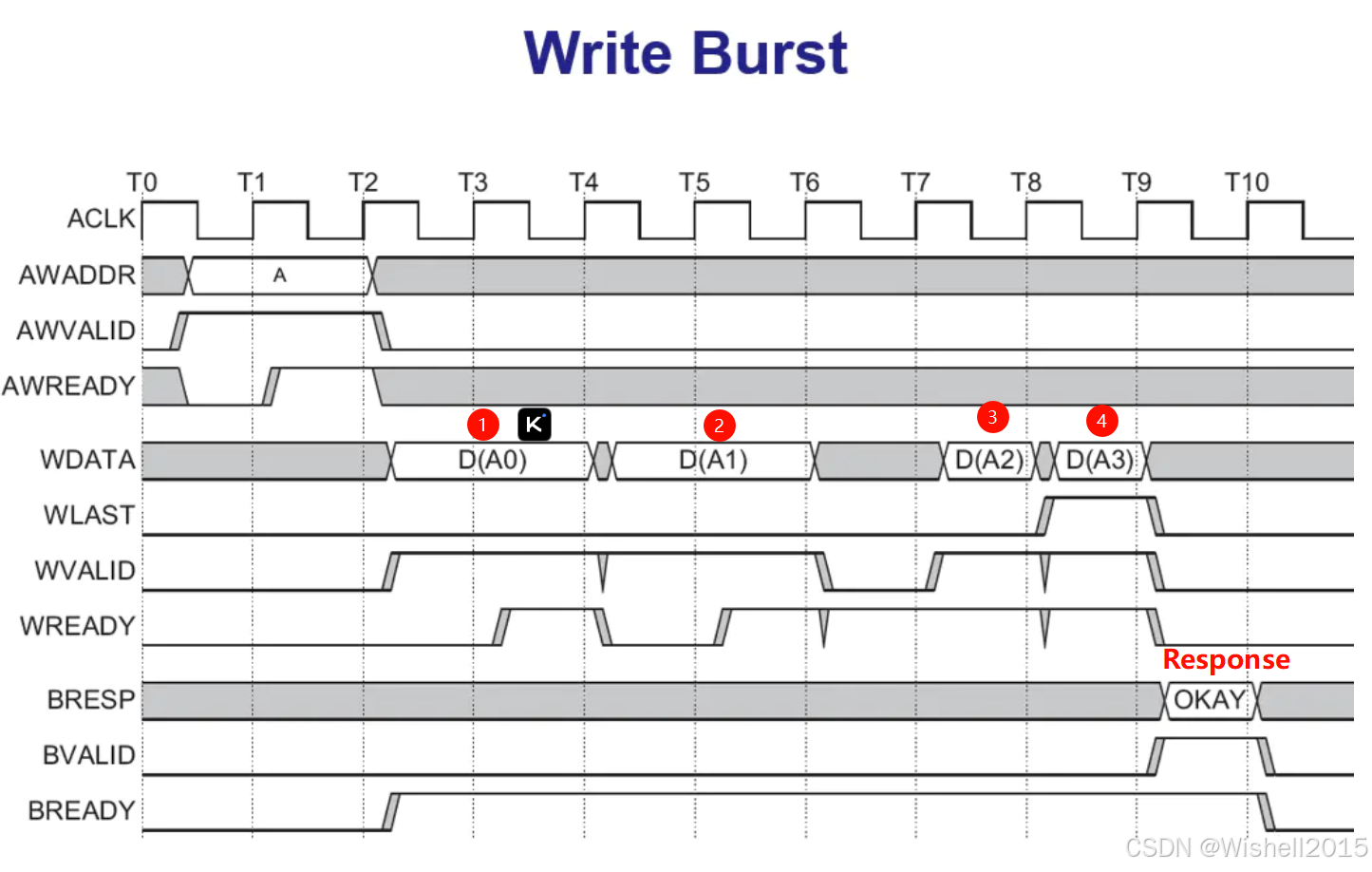

说到突发了,下面看下时序,可以理解为这次机关枪发了4发子弹写入。

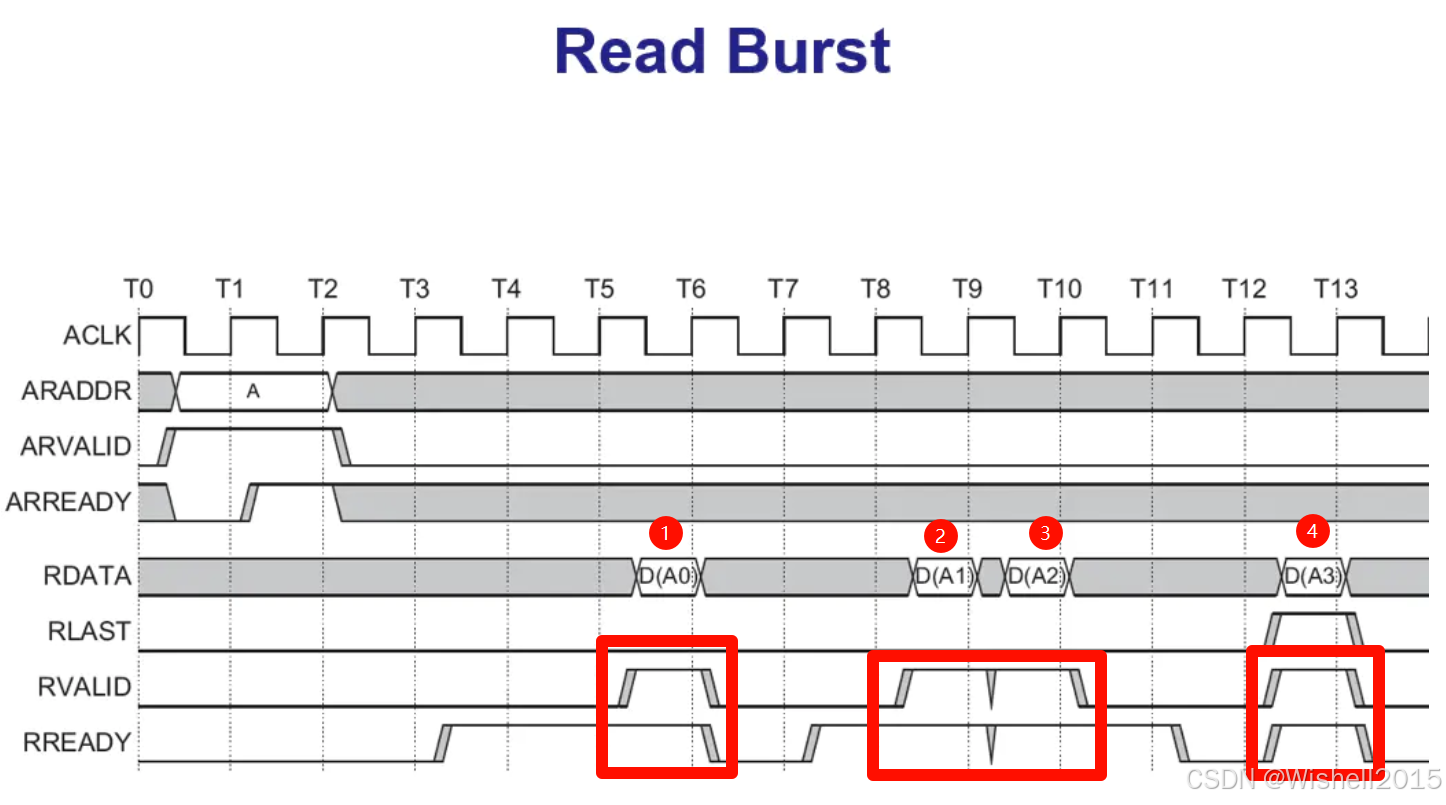

读也一样,而且是在握手成功后。不懂握手的话,再去练习stream模式吧,Full不适合你。

突发长度与宽度(Length & Size)这部分定义了"一梭子子弹"有多少发,以及每一发有多大。

AxLEN (Length): 协议为了省资源,用 0 表示 1 次传输。

- 如果

ARLEN= 0,代表突发长度为 1。 - 如果

ARLEN= 15,代表突发长度为 16。 - 公式:

实际传输次数 = AxLEN + 1。

AxSIZE (Size): 用 2 的幂次方表示数据宽度。

000= 202^020 = 1 字节 (8-bit)010= 222^222 = 4 字节 (32-bit)011= 232^323 = 8 字节 (64-bit)

三种突发类型(Burst Type)

A. FIXED (固定模式):地址行为: 地址始终不变 。例如:首地址是 0x100,突发 4 次。地址序列:0x100 -> 0x100 -> 0x100 -> 0x100

B. INCR (Increment - 递增模式):地址行为: 地址线性增加 。增加的步长等于数据宽度(Size)。例如:首地址 0x100,突发 4 次,每次 4 字节。地址序列:0x100 -> 0x104 -> 0x108 -> 0x10C

C. WRAP (回环/回卷模式):地址行为: 地址线性增加,但一旦到了 "边界" ,就会回跳(Wrap) 到低地址,形成一个循环。限制: 长度只能是 2, 4, 8, 16(必须是 2 的幂)。

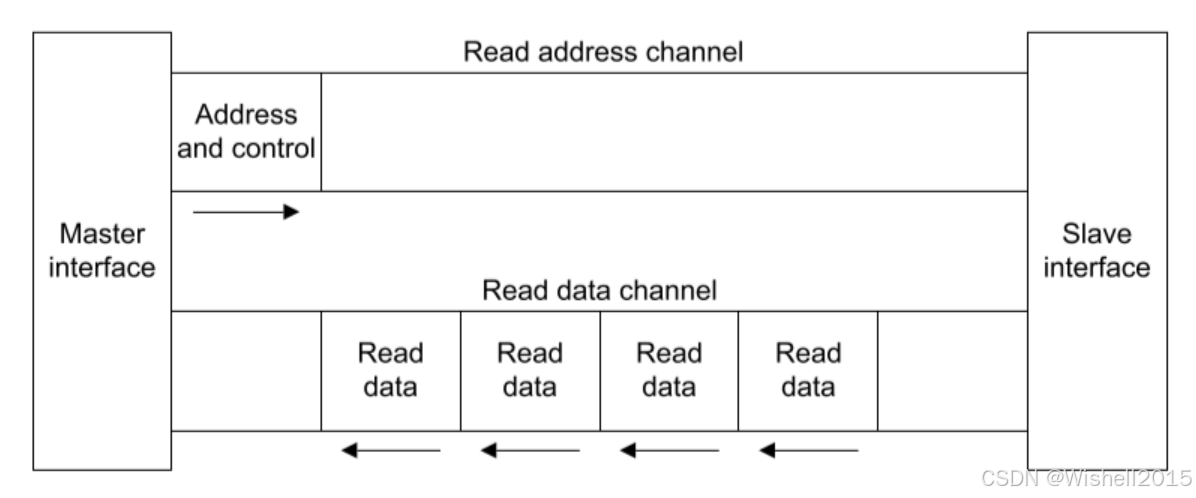

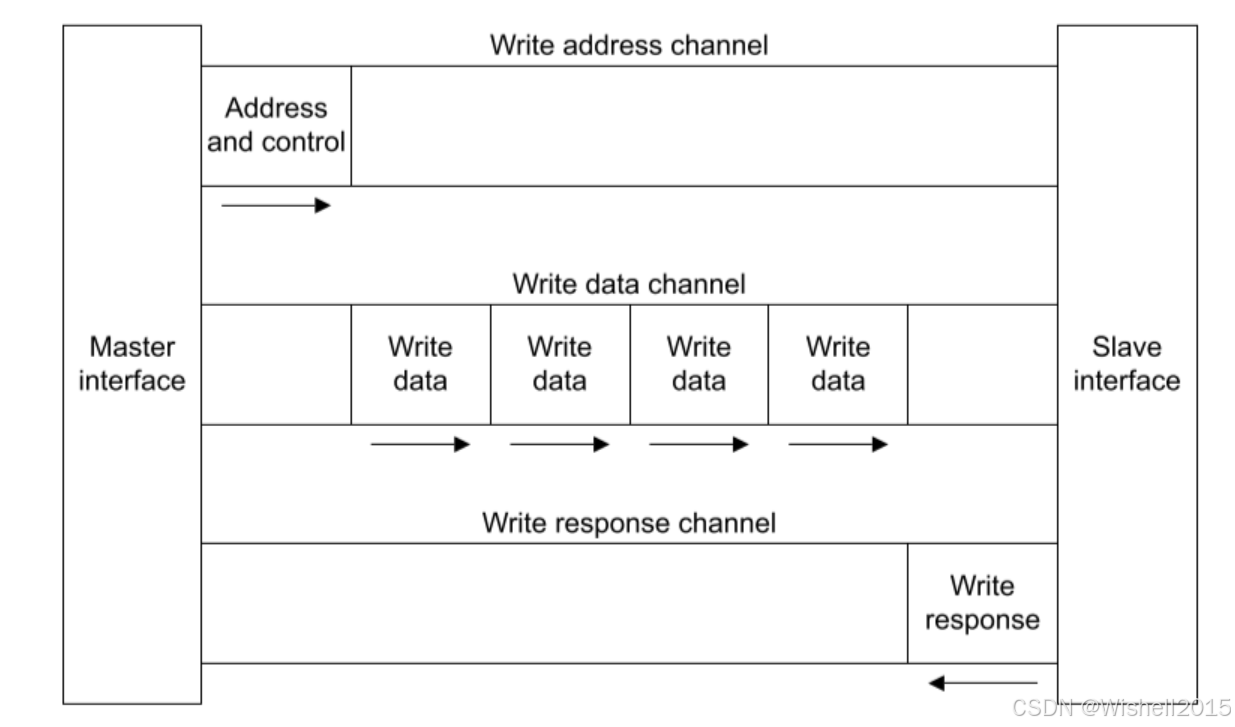

读取与写入事务

这个看图说话,对应了5个通道。

写响应通道 (Write Response Channel) 上可能的响应值包括:

- OKAY (0b00):正常访问成功。表示已成功完成正常访问

- EXOKAY (0b01):专属访问成功。

- SLVERR (0b10):从设备错误。已成功访问从设备,但从设备希望向发端主设备返回错误条件(例如,数据读取无效)。

- DECERR (0b11):解码器错误。通常由互连组件生成,用于指示传输事务地址处没有任何从设备

信号

就看几个常用的信号即可:

全局信号(不属于任何通道):

-

ACLK: 全局时钟线(所有信号都在上升沿采样)。 -

ARESETn : 全局复位线(低电平有效 ,所以带个n)。

写地址通道 (Write Address Channel) - 前缀 AW :

-

AWADDR: 写地址(你要写到哪里)。 -

AWLEN: 突发长度(Burst Length)。告诉 Slave:"我要连着写多少个数据"。(实际传输次数 = AWLEN + 1)。 -

AWSIZE: 突发大小。每一个数据有多宽(1字节?4字节?)。 -

AWBURST: 突发类型(固定地址写、递增地址写等)。 -

AWID: 事务 ID(给这个订单贴个号,用于乱序处理)。 -

AWVALID / AWREADY : 握手信号(Master 说地址有效,Slave 说我准备好收地址了)。

写数据通道 (Write Data Channel) - 前缀 W

-

WDATA: 写数据(真正的货物)。 -

WSTRB: 写选通(Write Strobe)。像个掩码,比如 32位数据中,我只想改写其中某 8位,就靠它标记。 -

WLAST : 最后一个数据标记。告诉 Slave:"这是本次突发的最后一包数据,发完这包就结束了"。 -

WVALID / WREADY : 握手信号。

写响应通道 (Write Response Channel) - 前缀 B

这个通道负责 "签收回执" 。注意,这里的前缀是 B(代表 Back 或 Buffer)。

-

BRESP: 写响应状态。告诉 Master:"写成功了 (OKAY)"还是"写失败了 (ERROR)"。 -

BID : 响应 ID。必须和AWID对应,证明是哪笔订单的回执。 -

BVALID / BREADY : 握手信号。

读地址通道 (Read Address Channel) - 前缀 AR

-

ARADDR: 读地址。 -

ARLEN: 读突发长度(我要连着读多少个)。 -

ARSIZE: 读数据宽度。 -

ARBURST: 读突发类型。 -

ARID: 读事务 ID。 -

ARVALID / ARREADY : 握手信号。

读数据通道 (Read Data Channel) - 前缀 R

-

RDATA: 读回来的数据。 -

RRESP: 读响应状态(数据是否读取成功)。注意:读操作的状态是跟数据一起回来的,不像写操作有单独的响应通道。 -

RLAST : 最后一个数据标记。Slave 告诉 Master:"这是你要的最后一个数了"。 -

RID : 读 ID。对应ARID。 -

RVALID / RREADY : 握手信号。

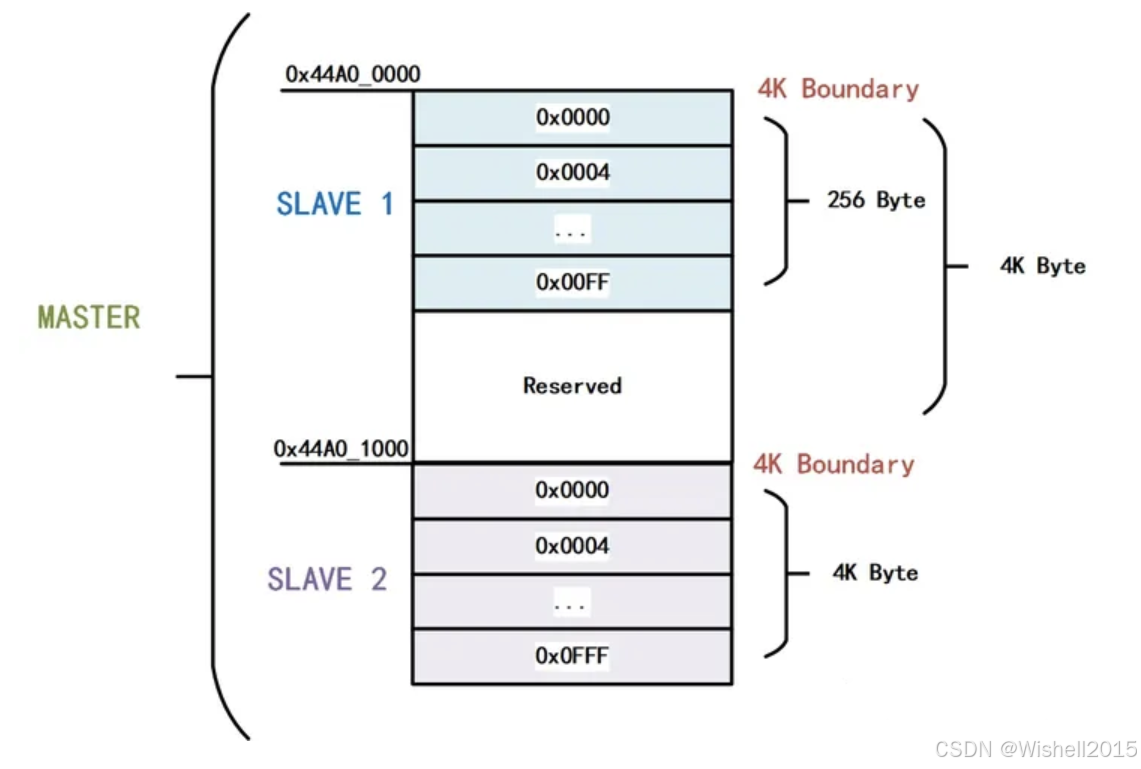

4K边界

AXI4协议规定主机上寄存器块的最小分块单元为4K Byte,每个从机的开始映射地址都是4KB的边界。这也影响了AXI4的一个读写规则,那就是一个burst传输不能跨越4KB的界限,否则就会引入将数据错误写入其他从机的风险。注意这个4KB的界限指的是MASTER的地址界限,例如一个burst中不能越过0xXXXX_X000的地址位。

举个例子:数据位宽m_axi_wdata=128bit,突发长度为100。可以计算出突发长度的字节数量:128÷8×100 =1600。

- 第1次:突发开始的地址是0,结束地址(最后一个字节的地址)是1599。

- 第2次:突发开始的地址是1600,结束地址(最后一个字节的地址)是3199。

- 第3次:突发开始的地址是3200,结束地址(最后一个字节的地址)是4799。这就有问题了,因为地址超过了4096(即4k边界)

协议就看到这里,具体用的时候再细说吧,主打一个了解。