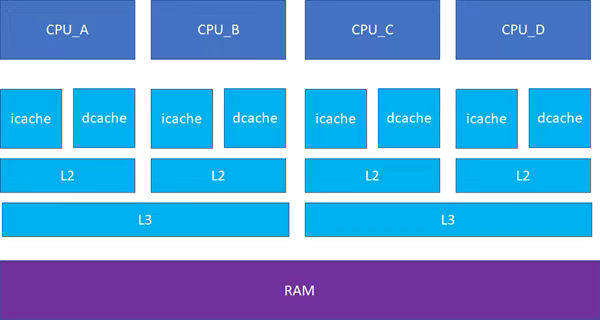

这个系统是一个4核处理器的多级缓存架构,属于典型的多核CPU内存层次结构。

一、系统架构分析

该系统的内存层次从"CPU核心"到"主存"分为4层,各组件的作用:

- CPU核心层(4个独立核心:CPU_A~CPU_D)

每个核心是独立的计算单元,负责执行指令、处理数据。 - L1缓存层(每个核心独享iCache+dCache)

iCache(指令缓存):缓存当前核心执行的指令,加速指令读取;dCache(数据缓存):缓存当前核心处理的数据,加速数据读写;- 特点:每个核心独享L1缓存(物理上独立),速度最快、容量最小。

- L2缓存层(每个核心独享L2)

每个核心绑定独立的L2缓存,容量比L1大、速度比L1稍慢,用于缓存L1未命中的数据/指令,降低对更高层级缓存的访问频率。 - L3缓存层(2个共享L3,CPU_A+B共享1个,CPU_C+D共享1个)

L3缓存是"局部共享"的:CPU_A和CPU_B共享一个L3,CPU_C和CPU_D共享另一个L3;容量比L2大、速度更慢,用于缓存L2未命中的数据,同时减少跨核心访问主存的开销。 - 主存层(RAM)

所有核心共享的全局内存,容量最大、速度最慢,是缓存未命中时的最终数据来源。

二、Cache的同步问题

在多核系统中,多个核心的缓存可能同时缓存同一份主存数据 ,当其中一个核心修改了该数据时,其他核心的缓存数据会变成"脏数据",导致数据不一致 ,这就是Cache的同步问题(即"缓存一致性问题")。

结合本系统的架构,缓存同步的具体场景与问题:

- L1/L2缓存的私有性导致的不一致

例如:CPU_A的dCache缓存了主存地址0x1000的数据(值为10),CPU_B的dCache也缓存了0x1000的数据(值为10)。若CPU_A修改该数据为20,此时CPU_B的dCache中0x1000的值仍为10,与主存(或CPU_A的缓存)不一致,后续CPU_B读取该地址会得到错误数据。 - L3缓存的局部共享性放大的不一致

本系统中CPU_A+B共享L3、CPU_C+D共享L3:若CPU_A修改了L1/L2中的数据,该数据会同步到"CPU_A+B的共享L3",但"CPU_C+D的共享L3"不会感知到这个修改;若CPU_C也缓存了同一份数据,就会出现跨L3区域的不一致。

三、缓存同步问题的解决方式

为了解决缓存不一致,多核系统会通过缓存一致性协议实现Cache同步,常见协议如MESI(Modified/Exclusive/Shared/Invalid):

- Modified(已修改):缓存数据被修改,与主存不一致,且仅当前核心持有该数据;

- Exclusive(独占):缓存数据与主存一致,且仅当前核心持有该数据;

- Shared(共享):缓存数据与主存一致,多个核心同时持有该数据;

- Invalid(无效):缓存数据已过期,需重新从主存/其他缓存加载。

协议的核心逻辑:当一个核心修改缓存数据时,会通过总线广播"修改通知",其他核心收到通知后,将自己缓存中对应的"共享数据"标记为"Invalid";后续其他核心读取该数据时,会先检查缓存有效性,若无效则从修改后的核心(或主存)重新加载最新数据。

总结

该系统是4核+三级缓存(L1独享、L2独享、L3局部共享的多核架构,Cache同步的核心问题是"多核心缓存同一份数据时的不一致",需通过MESI等缓存一致性协议,结合总线广播机制实现缓存数据的同步,保证各核心访问数据的正确性。