Renesas RH850-U2A Load Instructions

- [1 Load Instructions](#1 Load Instructions)

-

- [1.1 LD Instructions](#1.1 LD Instructions)

- [2 LD Instructions](#2 LD Instructions)

-

- [2.1 LD.B](#2.1 LD.B)

-

- [2.1.1 LD.B Instruction format and Operation](#2.1.1 LD.B Instruction format and Operation)

- [2.1.2 LD.B Instruction Opcode](#2.1.2 LD.B Instruction Opcode)

- [2.2 LD.BU](#2.2 LD.BU)

-

- [2.2.1 LD.BU Instruction format and Operation](#2.2.1 LD.BU Instruction format and Operation)

- [2.2.2 LD.BU Instruction Opcode](#2.2.2 LD.BU Instruction Opcode)

- [2.3 LD.DW](#2.3 LD.DW)

-

- [2.3.1 LD.DW Instruction format and Operation](#2.3.1 LD.DW Instruction format and Operation)

- [2.3.2 LD.DW Opcode](#2.3.2 LD.DW Opcode)

- [2.4 LD.H](#2.4 LD.H)

-

- [2.4.1 LD.H Instruction format and Operation](#2.4.1 LD.H Instruction format and Operation)

- [2.4.2 LD.H Opcode](#2.4.2 LD.H Opcode)

- [2.5 LD.HU](#2.5 LD.HU)

- [2.6 LD.W](#2.6 LD.W)

-

- [2.5.1 LD.W Instruction format and Operation](#2.5.1 LD.W Instruction format and Operation)

- [2.5.2 LD.W Opcode](#2.5.2 LD.W Opcode)

1 Load Instructions

Execute data transfer from memory to register. The following instructions (mnemonics) are provided.

1.1 LD Instructions

− LD.B: Load byte

− LD.BU: Load byte unsigned

− LD.DW: Load double word

− LD.H: Load halfword

− LD.HU: Load halfword unsigned

− LD.W: Load word

2 LD Instructions

2.1 LD.B

2.1.1 LD.B Instruction format and Operation

c

[Instruction format]

(1) LD.B disp16[reg1], reg2

adr ← GR[reg1] + sign-extend (disp16)

CheckException (MDP)

GR[reg2] ← sign-extend (Load-memory (adr, Byte))

(2) LD.B disp23[reg1], reg3

adr ← GR[reg1] + sign-extend (disp23)

CheckException (MDP)

GR[reg3] ← sign-extend (Load-memory (adr, Byte))

(3) LD.B [reg1]+, reg3

adr ← GR [reg1]Note 1

CheckException (MDP)

GR [reg3] ← sign-extend (Load-memory (adr, Byte))

GR [reg1] ← GR [reg1] + 1

(4) LD.B [reg1]−, reg3

adr ← GR [reg1]Note 1

CheckException (MDP)

GR [reg3] ← sign-extend (Load-memory (adr, Byte))

GR [reg1] ← GR [reg1] -- 1

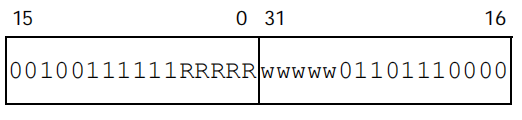

2.1.2 LD.B Instruction Opcode

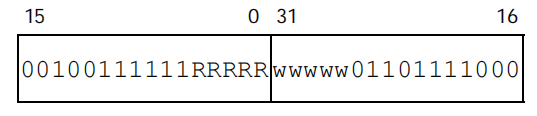

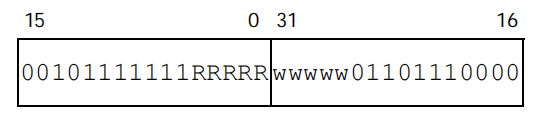

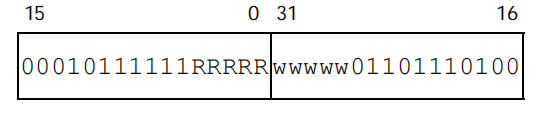

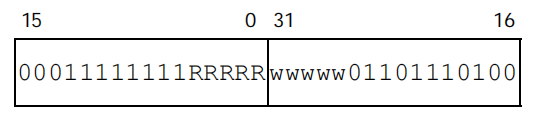

(1) LD.B disp16[reg1], reg2

c

rrrrr = reg2

Where RRRRR = reg1, wwwww = reg3.

ddddddd is the lower 7 bits of disp23.

DDDDDDDDDDDDDDDD is the higher 16 bits of disp23.(2) LD.B disp23[reg1], reg3

shell

Where RRRRR = reg1, wwwww = reg3.

ddddddd is the lower 7 bits of disp23.

DDDDDDDDDDDDDDDD is the higher 16 bits of disp23.(3) LD.B [reg1]+, reg3

(4) LD.B [reg1]−, reg3

2.2 LD.BU

2.2.1 LD.BU Instruction format and Operation

c

[Instruction format]

(1) LD.BU disp16[reg1], reg2

adr ← GR[reg1] + sign-extend (disp16)

CheckException(MDP)

GR[reg2] ← zero-extend (Load-memory (adr, Byte))

(2) LD.BU disp23[reg1], reg3

adr ← GR[reg1] + sign-extend (disp23)

CheckException (MDP)

GR[reg3] ← zero-extend (Load-memory (adr, Byte))

(3) LD.BU [reg1]+, reg3

adr ← GR[reg1]Note 1

CheckException(MDP)

GR[reg3] ← zero-extend (Load-memory (adr, Byte))

GR[reg1] ← GR[reg1] + 1

(4) LD.BU [reg1]−, reg3

adr ← GR[reg1]

CheckException(MDP)

GR[reg3] ← zero-extend (Load-memory (adr, Byte))

GR[reg1] ← GR[reg1] − 12.2.2 LD.BU Instruction Opcode

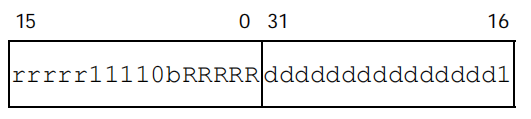

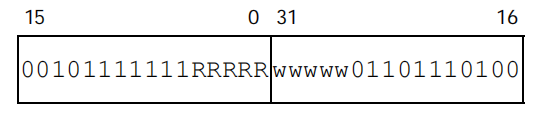

(1) LD.BU disp16[reg1], reg2

c

ddddddddddddddd is the higher 15 bits of disp16, and b is bit 0 of disp16.

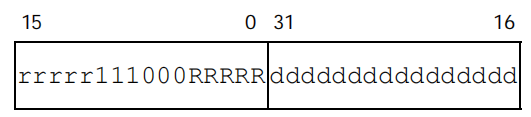

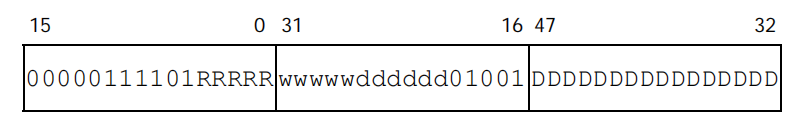

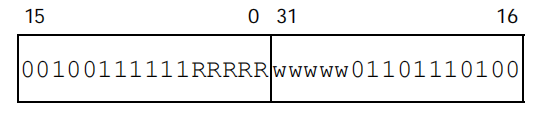

rrrrr ≠ 00000 (Do not specify r0 for reg2.)(2) LD.BU disp23[reg1], reg3

c

Where RRRRR = reg1, wwwww = reg3.

ddddddd is the lower 7 bits of disp23.

DDDDDDDDDDDDDDDD is the higher 16 bits of disp23.(3) LD.BU [reg1]+, reg3

(4) LD.BU [reg1]−, reg3

2.3 LD.DW

2.3.1 LD.DW Instruction format and Operation

c

[Instruction format]

LD.DW disp23[reg1], reg3

[Operation]

adr ← GR[reg1] + sign-extend (disp23)

CheckException (MAE)

CheckException (MDP)

data ← Load-memory (adr, Double-word)

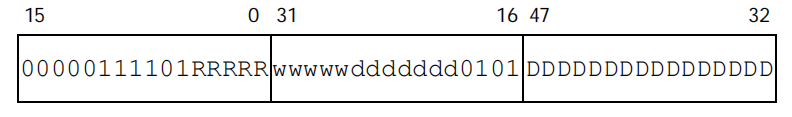

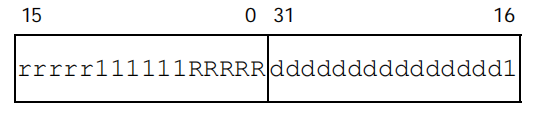

GR[reg3 + 1] || GR[reg3] ← data2.3.2 LD.DW Opcode

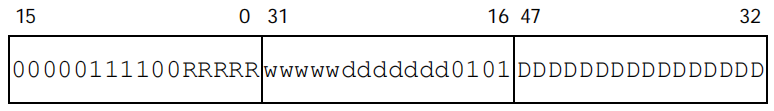

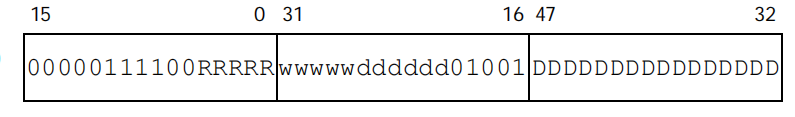

c

Where RRRRRR = reg1, wwwww = reg3.

dddddd is the lower side bits 6 to 1 of disp23.

DDDDDDDDDDDDDDDD is the higher 16 bits of disp23.2.4 LD.H

2.4.1 LD.H Instruction format and Operation

c

[Instruction format]

(1) LD.H disp16[reg1], reg2

adr ← GR[reg1] + sign-extend (disp16)

CheckException (MAE)

CheckException (MDP)

GR[reg2] ← sign-extend (Load-memory (adr, Halfword))

(2) LD.H disp23[reg1], reg3

adr ← GR[reg1] + sign-extend (disp23)Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg3] ← sign-extend (Load-memory (adr, Halfword))

(3) LD.H [reg1]+, reg3

adr ← GR [reg1]Note 1

CheckException (MAE)

CheckException (MDP)

GR [reg3] ← sign-extend (Load-memory (adr, Halfword))

GR [reg1] ← GR [reg1] + 2

(4) LD.H [reg1]−, reg3

adr ← GR [reg1]Note 1

CheckException (MAE)

CheckException (MDP)

GR [reg3] ← sign-extend (Load-memory (adr, Halfword))

GR [reg1] ← GR [reg1] -- 2

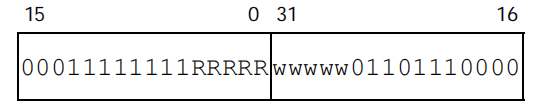

2.4.2 LD.H Opcode

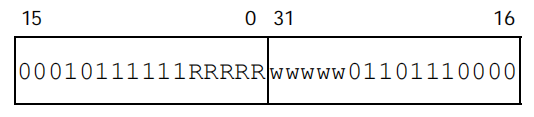

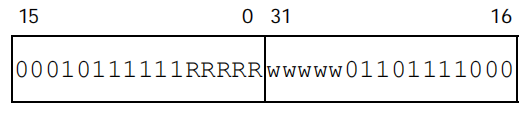

(1) LD.H disp16[reg1], reg2

c

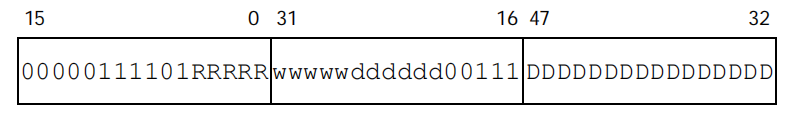

Where ddddddddddddddd is the higher 15 bits of disp16(2) LD.H disp23[reg1], reg3

c

Where RRRRR = reg1, wwwww = reg3.

dddddd is the lower side bits 6 to 1 of disp23.

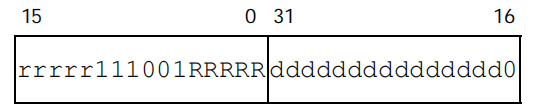

DDDDDDDDDDDDDDDD is the higher 16 bits of disp23.(3) LD.H [reg1]+, reg3

(4) LD.H [reg1]−, reg3

2.5 LD.HU

2.5.1 LD.HU Instruction format and Operation

c

[Instruction format]

(1) LD.HU disp16[reg1], reg2

adr ← GR[reg1] + sign-extend (disp16)Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg2] ← zero-extend (Load-memory (adr, Halfword))

(2) LD.HU disp23[reg1], reg3

adr ← GR[reg1] + sign-extend (disp23)Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg3] ← zero-extend (Load-memory (adr, Halfword))

(3) LD.HU [reg1]+, reg3

adr ← GR[reg1]Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg3] ← zero-extend (Load-memory (adr, Halfword))

GR[reg1] ← GR[reg1] + 2

(4) LD.HU [reg1]−, reg3

adr ← GR[reg1]Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg3] ← zero-extend (Load-memory (adr, Halfword))

GR[reg1] ← GR[reg1] − 2

2.5.2 LD.HU Opcode

(1) LD.HU disp16[reg1], reg2

c

Where ddddddddddddddd is the higher 15 bits of disp16.

rrrrr ≠ 00000 (Do not specify r0 for reg2.)(2) LD.HU disp23[reg1], reg3

c

Where RRRRR = reg1, wwwww = reg3.

dddddd is the lower side bits 6 to 1 of disp23.

DDDDDDDDDDDDDDDD is the higher 16 bits of disp23.(3) LD.HU [reg1]+, reg3

(4) LD.HU [reg1]−, reg3

2.6 LD.W

2.5.1 LD.W Instruction format and Operation

c

[Instruction format]

(1) LD.W disp16[reg1], reg2

adr ← GR[reg1] + sign-extend (disp16)Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg2] ← Load-memory (adr, Word)

(2) LD.W disp23[reg1], reg3

adr ← GR[reg1] + sign-extend (disp23)Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg3] ← Load-memory (adr, Word)

(3) LD.W [reg1]+ , reg3

adr ← GR[reg1]Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg3] ← Load-memory (adr, Word)

GR[reg1] ← GR [reg1] + 4

(4) LD.W [reg1]-- , reg3

adr ← GR[reg1]Note 1

CheckException (MAE)

CheckException (MDP)

GR[reg3] ← Load-memory (adr, Word)

GR[reg1] ← GR[reg1] − 4

2.5.2 LD.W Opcode

(1) LD.W disp16[reg1], reg2

c

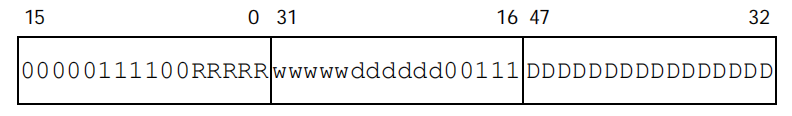

Where ddddddddddddddd is the higher 15 bits of disp16.(2) LD.W disp23[reg1], reg3

c

Where RRRRR = reg1, wwwww = reg3.

dddddd is the lower side bits 6 to 1 of disp23.

DDDDDDDDDDDDDDDD is the higher 16 bits of disp23.(3) LD.W [reg1]+ , reg3

(4) LD.W [reg1]-- , reg3