Renesas RH850-U2A Basic Instructions

- [1 Overview of Common Basic Instructions](#1 Overview of Common Basic Instructions)

-

- [1.1 Load Instructions](#1.1 Load Instructions)

-

- [1.1.1 LD Instructions](#1.1.1 LD Instructions)

- [1.1.2 SLD instructions](#1.1.2 SLD instructions)

- [1.2.1 ST Instructions](#1.2.1 ST Instructions)

- [1.2.2 SST instructions](#1.2.2 SST instructions)

- [1.3 Arithmetic Instructions](#1.3 Arithmetic Instructions)

- [1.4 Logical Instructions](#1.4 Logical Instructions)

- [2 Basic Instruction Set](#2 Basic Instruction Set)

-

- [2.1 Conventions of Instruction Format](#2.1 Conventions of Instruction Format)

- [2.2 Conventions of Operation](#2.2 Conventions of Operation)

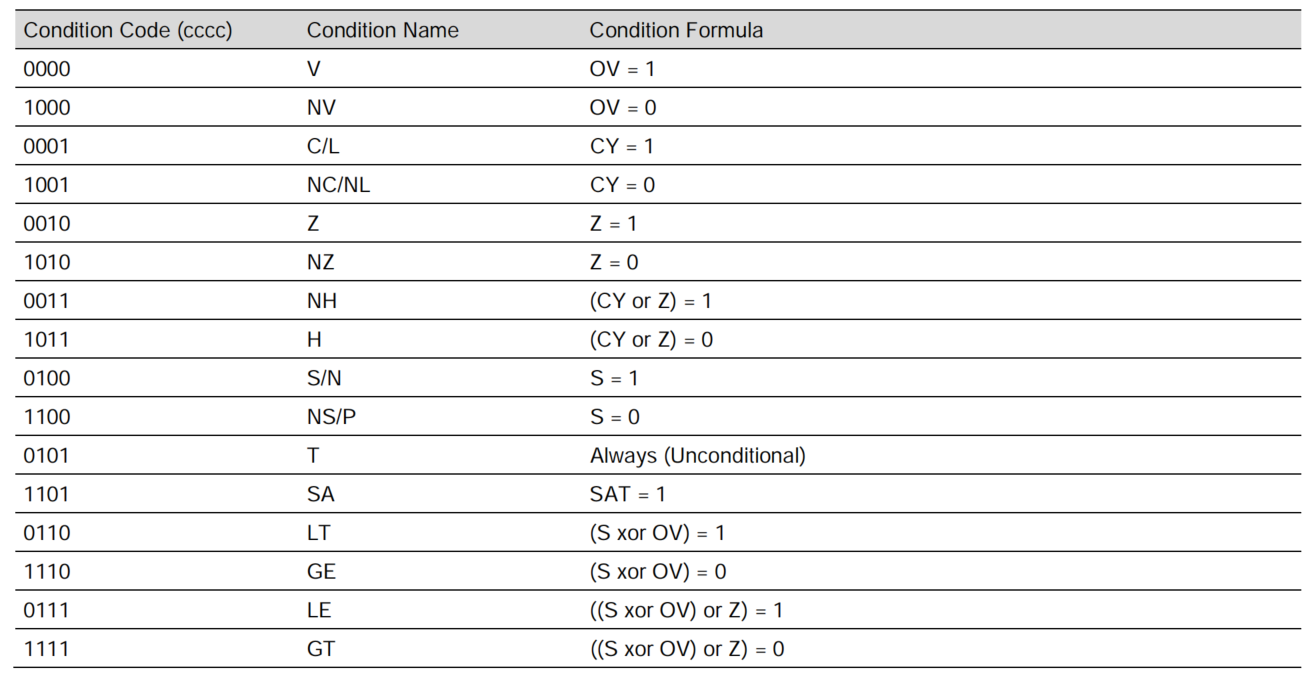

- [3 Condition Codes](#3 Condition Codes)

1 Overview of Common Basic Instructions

1.1 Load Instructions

Execute data transfer from memory to register. The following instructions (mnemonics) are provided.

1.1.1 LD Instructions

− LD.B: Load byte

− LD.BU: Load byte unsigned

− LD.DW: Load double word

− LD.H: Load halfword

− LD.HU: Load halfword unsigned

− LD.W: Load word

1.1.2 SLD instructions

− SLD.B: Short format load byte

− SLD.BU: Short format load byte unsigned

− SLD.H: Short format load halfword

− SLD.HU: Short format load halfword unsigned

− SLD.W: Short format load word

1.2 Store Instructions

Execute data transfer from register to memory. The following instructions (mnemonics) are provided.

1.2.1 ST Instructions

− ST.B: Store byte

− ST.DW: Store double word

− ST.H: Store halfword

− ST.W: Store word

1.2.2 SST instructions

− SST.B: Short format store byte

− SST.H: Short format store halfword

− SST.W: Short format store word

1.3 Arithmetic Instructions

Add, subtract, transfer, or compare data between registers. The following instructions (mnemonics) are provided.

● ADD: Add

● ADDI: Add immediate

● CMP: Compare

● MOV: Move

● MOVEA: Move effective address

● SUB: Subtract

1.4 Logical Instructions

Include logical operation instructions. The following instructions (mnemonics) are provided.

● AND: AND

● ANDI: AND immediate

● NOT: NOT

● OR: OR

● ORI: OR immediate

2 Basic Instruction Set

2.1 Conventions of Instruction Format

| Symbol | Meaning |

|---|---|

| reg1 | General-purpose register (as source register) |

| reg2 | General-purpose register (primarily as destination register with some as source registers) |

| reg3 | General-purpose register (primarily used to store the remainder of a division result and/or the higher 32 bits of a multiplication result) |

| imm × | ×-bit immediate data |

| disp × | ×-bit displacement data |

| regID | System register number |

| selID | System register selection ID |

| cond | Condition code |

| cccc | 4-bit data to specify condition code |

| sp | Stack pointer (r3) |

| ep | Element pointer (r30) |

| list12 | Lists of registers |

| rh-rt | Indicates multiple general-purpose registers, from the general-purpose register indicated by rh to the generalpurpose register indicated by rt. |

| eh-et | Indicates multiple system registers of MPU entry (MPLA, MPUA, MPAT), from the entry number indicated by eh to the entry number indicated by et. |

2.2 Conventions of Operation

| Symbol | Meaning |

|---|---|

| ← | Assignment |

| GR [a] | Value stored in general-purpose register a |

| SR [a, b] | Value stored in system register (RegID = a, SelID = b) |

| (n:m) | Bit selection. Select from bit n to bit m. |

| CheckException(a) | Checks the conditions for generating the exception "a" and, if one is detected, suspends the instruction execution and performs exception processing |

| zero-extend (n) | Zero-extends "n" to word |

| sign-extend (n) | Sign-extends "n" to word |

| load-memory (a, b) | Reads data of size b from address a |

| store-memory (a, b, c) | Writes data b of size c to address a |

| result | Outputs results on flag |

| Byte | Byte (8 bits) |

| Half word | Halfword (16 bits) |

| Word | Word (32 bits) |

| R | 1-bit data of code specifying reg1 or regID |

| r | 1-bit data of code specifying reg2 |

| w | 1-bit data of code specifying reg3 |

| D | 1-bit data of displacement (indicates higher bits of displacement) |

| d | 1-bit data of displacement |

| I | 1-bit data of immediate (indicates higher bits of immediate) |

| i | 1-bit data of immediate |

| cccc | 4-bit data for condition code specification |

| L | 1-bit data of code specifying general-purpose register in register list |

| S | 1-bit data of code specifying EIPC/FEPC, EIPSW/FEPSW in register list |

| P | 1-bit data of code specifying PSW in register list |

3 Condition Codes