Renesas RH850-U2A Arithmetic Instructions

- [1 Arithmetic Instructions](#1 Arithmetic Instructions)

-

- [1.1 Overview of Arithmetic Instructions](#1.1 Overview of Arithmetic Instructions)

- [2 Arithmetic Instructions](#2 Arithmetic Instructions)

-

- [2.1 ADD](#2.1 ADD)

-

- [2.1.1 ADD Instruction format and Operation](#2.1.1 ADD Instruction format and Operation)

- [2.1.2 ADD Instruction Opcode](#2.1.2 ADD Instruction Opcode)

- [2.2 ADDI](#2.2 ADDI)

-

- [2.2.1 ADDI Instruction format and Operation](#2.2.1 ADDI Instruction format and Operation)

- [2.2.2 ADDI Instruction Opcode](#2.2.2 ADDI Instruction Opcode)

- [2.3 CMP](#2.3 CMP)

-

- [2.3.1 CMP Instruction format and Operation](#2.3.1 CMP Instruction format and Operation)

- [2.3.2 CMP Instruction Opcode](#2.3.2 CMP Instruction Opcode)

- [2.3.3 CMP Instruction Flags](#2.3.3 CMP Instruction Flags)

- [2.4 MOV](#2.4 MOV)

-

- [2.4.1 MOV Instruction format and Operation](#2.4.1 MOV Instruction format and Operation)

- [2.4.2 MOV Instruction Opcode](#2.4.2 MOV Instruction Opcode)

- [2.5 MOVEA](#2.5 MOVEA)

-

- [2.5.1 MOVEA Instruction format and Operation](#2.5.1 MOVEA Instruction format and Operation)

- [2.5.2 MOVEA Instruction Opcode](#2.5.2 MOVEA Instruction Opcode)

- [2.6 SUB](#2.6 SUB)

-

- [2.6.1 SUB Instruction format and Operation](#2.6.1 SUB Instruction format and Operation)

- [2.6.2 SUB Instruction Opcode](#2.6.2 SUB Instruction Opcode)

- [2.6.3 SUB Instruction Flags](#2.6.3 SUB Instruction Flags)

1 Arithmetic Instructions

1.1 Overview of Arithmetic Instructions

Add, subtract, transfer, or compare data between registers. The following instructions (mnemonics) are provided.

● ADD: Add

● ADDI: Add immediate

● CMP: Compare

● MOV: Move

● MOVEA: Move effective address

● MOVHI: Move high halfword

● SUB: Subtract

2 Arithmetic Instructions

2.1 ADD

2.1.1 ADD Instruction format and Operation

c

[Instruction format]

(1) ADD reg1, reg2

GR[reg2] ← GR[reg2] + GR[reg1]

(2) ADD imm5, reg2

GR[reg2] ← GR[reg2] + sign-extend (imm5)2.1.2 ADD Instruction Opcode

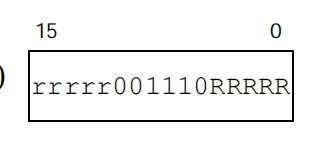

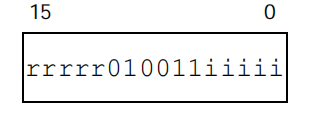

(1) ADD reg1, reg2

(2) ADD imm5, reg2

2.2 ADDI

2.2.1 ADDI Instruction format and Operation

c

[Instruction format]

ADDI imm16, reg1, reg2

[Operation]

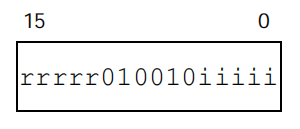

GR [reg2] ← GR [reg1] + sign-extend (imm16)2.2.2 ADDI Instruction Opcode

2.3 CMP

2.3.1 CMP Instruction format and Operation

c

[Instruction format]

(1) CMP reg1, reg2

result ← GR[reg2] − GR[reg1]

(2) CMP imm5, reg2

result ← GR[reg2] − sign-extend (imm5)

2.3.2 CMP Instruction Opcode

(1) CMP reg1, reg2

(2) CMP imm5, reg2

2.3.3 CMP Instruction Flags

c

CY "1" if a borrow occurs from MSB; otherwise, "0".

OV "1" if overflow occurs; otherwise, "0".

S "1" if the operation result is negative; otherwise, "0".

Z "1" if the operation result is "0"; otherwise, "0".2.4 MOV

2.4.1 MOV Instruction format and Operation

c

[Instruction format]

(1) MOV reg1, reg2

GR[reg2] ← GR[reg1]

(2) MOV imm5, reg2

GR[reg2] ← sign-extend (imm5)

(3) MOV imm32, reg1

GR[reg1] ← imm32

2.4.2 MOV Instruction Opcode

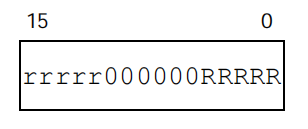

(1) MOV reg1, reg2

rrrrr ≠ 00000 (Do not specify r0 for reg2.)

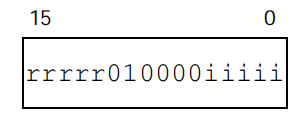

(2) MOV imm5, reg2

rrrrr ≠ 00000 (Do not specify r0 for reg2.)

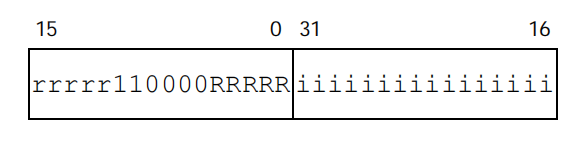

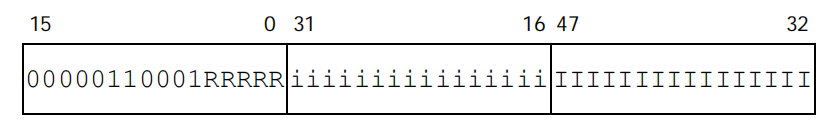

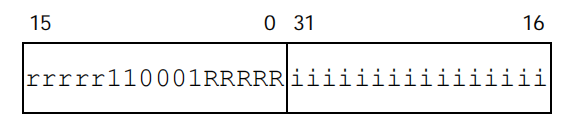

(3) MOV imm32, reg1

c

i (bits 31 to 16) refers to the lower 16 bits of 32-bit immediate data.

I (bits 47 to 32) refers to the higher 16 bits of 32-bit immediate data.2.5 MOVEA

2.5.1 MOVEA Instruction format and Operation

c

[Instruction format]

MOVEA imm16, reg1, reg2

[Operation]

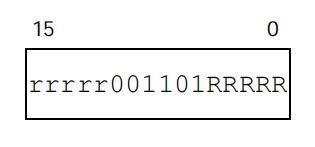

GR[reg2] ← GR[reg1] + sign-extend (imm16)2.5.2 MOVEA Instruction Opcode

rrrrr ≠ 00000 (Do not specify r0 for reg2.)

2.6 SUB

2.6.1 SUB Instruction format and Operation

c

[Instruction format]

SUB reg1, reg2

[Operation]

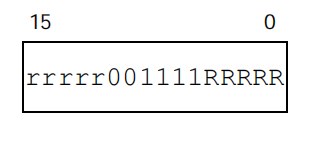

GR[reg2] ← GR[reg2] − GR[reg1]2.6.2 SUB Instruction Opcode

2.6.3 SUB Instruction Flags

c

CY "1" if a borrow occurs from MSB; otherwise, "0".

OV "1" if overflow occurs; otherwise, "0".

S "1" if the operation result is negative; otherwise, "0".

Z "1" if the operation result is "0"; otherwise, "0".

SAT ---