force命令将指定对象设置为给定值,并强制其保持该值,直到通过release、force -release、deposit -release命令释放,或被新的force覆盖。

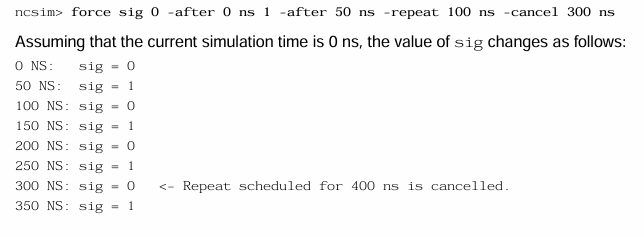

默认情况下新值立即生效;可通过-after选项延迟指定时长赋值。对于 Verilog 线网、VHDL 信号和端口,新值会在命令返回前通过整个层次结构传播。

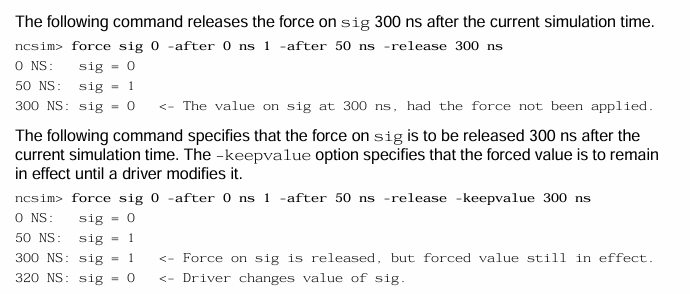

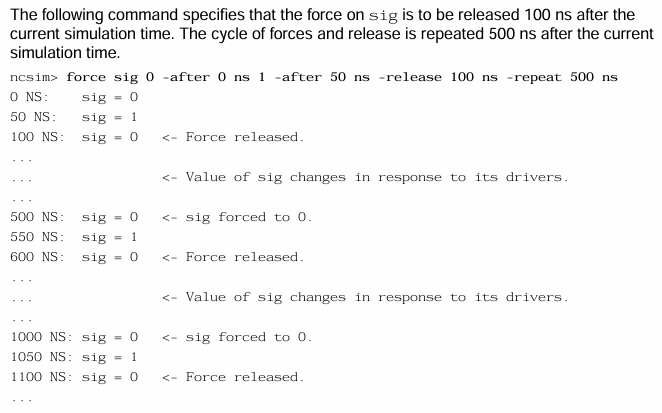

默认释放force后,对象值会立即恢复为无强制时的状态;若包含-keepvalue选项(force -release -keepvalue time_spec),强制值会保持到指定时间后再释放。

被强制的对象必须具备写权限,否则仿真器会报错

以下对象不支持force操作:

Verilog 存储器

Verilog 存储元件

Verilog 寄存器的位选 / 部分选

未展开 Verilog 线网的位选 / 部分选

VHDL 变量

之前有次仿真中尝试对reg的Q端进行force值,查看波形发现没有force上,以上就是可能的原因。

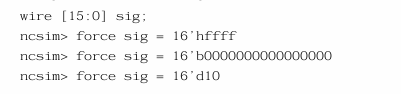

向量的force可以使用十六进制,二进制和十进制

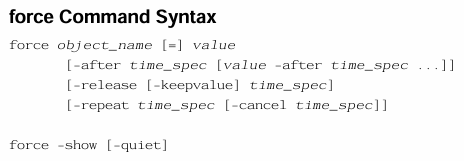

force命令的语法如下:

一些例子