知识星球(星球名:芯片制造与封测技术社区,星球号:63559049)里的学员问:为什么在芯片互连中,介质的k值一直在降低?有哪些低k的介质?

互连介质的k值为什么在降低?

随着 CMOS 技术进入 45nm 及以下节点 ,互连 RC 延迟成为关键瓶颈,RC延迟见文章:

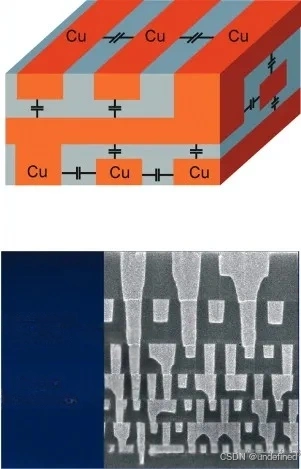

如上图,金属线与金属线之间夹着介质层,类似于一个电容,而寄生电容是RC延迟的主要来源。

而电容的表达式为:

C=ε*A/d

C:电容值

ε:介电常数

A:电极面积 (互连金属线的宽度)

d:金属线之间的距离

如表达式可以看出,介电常数越大,电容越大,RC延迟越严重。

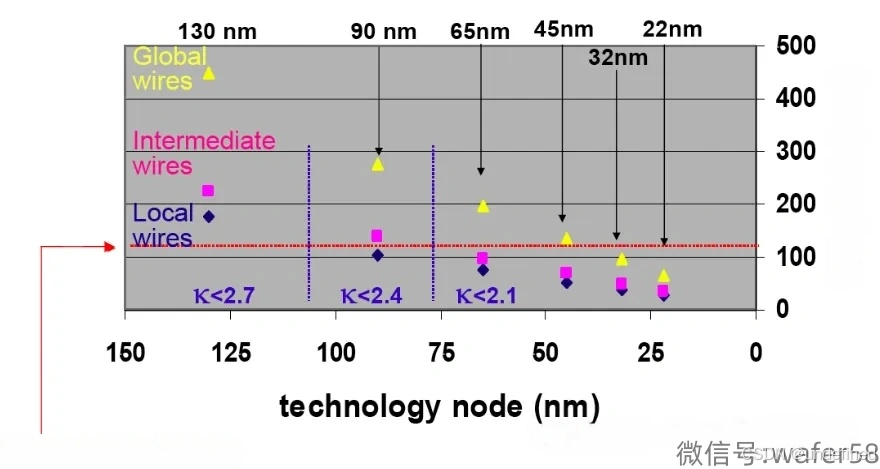

芯片节点与k值的关系? 如上图,k值逐渐由小于2.7降到小于2.1,

如上图,k值逐渐由小于2.7降到小于2.1,

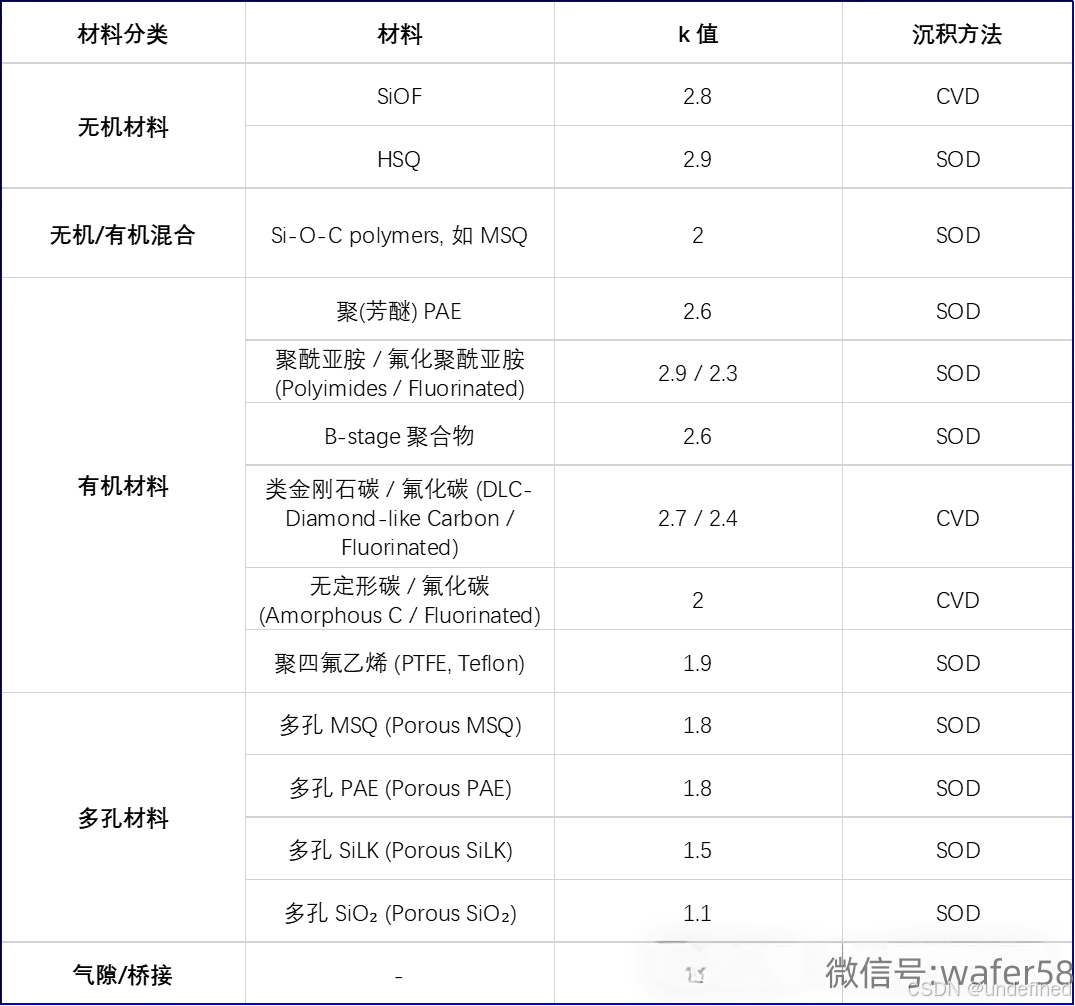

各类低k介质有哪些?