注:本文为 " SerDes" 相关合辑。

图片清晰度受引文原图所限。

略作重排,未整理去重。

如有内容异常,请看原文。

What is SerDes (Serializer/Deserializer)?

什么是 SerDes(串行器/解串器)?

Definition

定义

SerDes is a functional block that Serializes and Deserializes digital data used in high-speed chip-to-chip communication. Modern SoCs for high-performance computing (HPC), artificial intelligence (AI), automotive, mobile, and Internet-of-Things (IoT) applications implement SerDes that can support multiple data rates and standards like PCI Express (PCIe) \text{PCI Express (PCIe)} PCI Express (PCIe), MIPI \text{MIPI} MIPI, Ethernet \text{Ethernet} Ethernet, USB \text{USB} USB, USR/XSR \text{USR/XSR} USR/XSR.

SerDes 是一个功能模块,用于对高速芯片间通信中使用的数字数据进行串行化和反串行化处理。面向高性能计算(HPC)、人工智能(AI)、汽车、移动和物联网(IoT)应用的现代片上系统(SoC)会集成 SerDes,它可支持多种数据速率及 PCI Express (PCIe) \text{PCI Express (PCIe)} PCI Express (PCIe)、 MIPI \text{MIPI} MIPI、 Ethernet \text{Ethernet} Ethernet、 USB \text{USB} USB、 USR/XSR \text{USR/XSR} USR/XSR 等标准。

A SerDes implementation includes parallel-to-serial (serial-to-parallel) data conversion, impedance matching circuitry, and clock data recovery functionality. The primary role of SerDes is to minimize the number of I/O interconnects.

SerDes 的实现包含并行转串行(串行转并行)数据转换、阻抗匹配电路,以及时钟数据恢复功能。SerDes 的主要作用是减少 I/O 互连的数量。

SerDes (serializer/deserializer) Figure 1

SerDes(串行器/解串器)图 1

Why Do We Need SerDes?

为什么需要 SerDes?

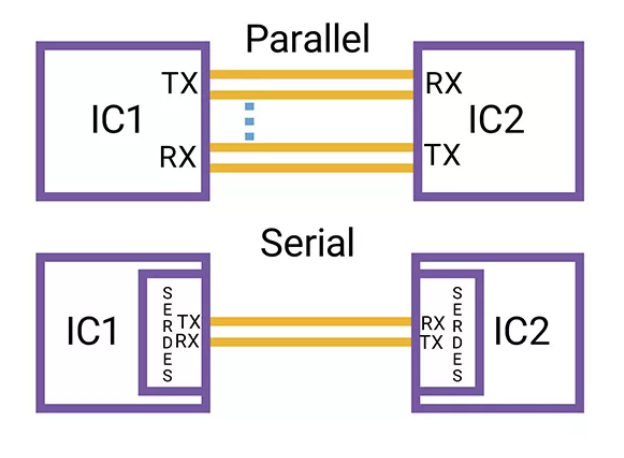

Distributed data processing in integrated circuits (ICs) need high speed data transfer between the ICs. Parallel and serial are the two options to transfer data between chips. Parallel data transfer requires multiple connections between ICs compared to serial data transfer that only needs one pair of connection.

集成电路(IC)中的分布式数据处理需要 IC 之间进行高速数据传输。芯片间数据传输有并行和串行两种方式:并行传输需要在 IC 之间建立多条连接,而串行传输仅需一对连接。

SerDes (serializer/deserializer) Figure 2

SerDes(串行器/解串器)图 2

As shown in the table above, serial data transfer can be an ideal option due to its advantages, such as low-power consumption, robust EMI performance, and easy package design.

如上述表格所示,串行数据传输因具备低功耗、强电磁干扰(EMI)性能、封装设计简便等优势,可作为理想选择。

SerDes Applications

SerDes 的应用

SerDes is the most fundamental building block of a physical layer for chip-to-chip interconnect systems:

SerDes 是芯片间互连系统物理层最基础的构建模块:

SerDes + Physical Coding Sublayer (PCS) = PHY or Physical Layer

SerDes + 物理编码子层(PCS)= PHY 或物理层

The Open Systems Interconnection (OSI) model defines physical layer, or PHY, as an abstraction layer responsible for transmission and reception of the data. It is the lowest layer in the OSI model, which also includes:

开放系统互连(OSI)模型将物理层(PHY)定义为负责数据收发的抽象层,它是 OSI 模型的最底层,该模型还包括:

- Application layer

应用层 - Presentation layer

表示层 - Session layer

会话层 - Transport layer

传输层 - Network layer

网络层 - Datalink layer

数据链路层

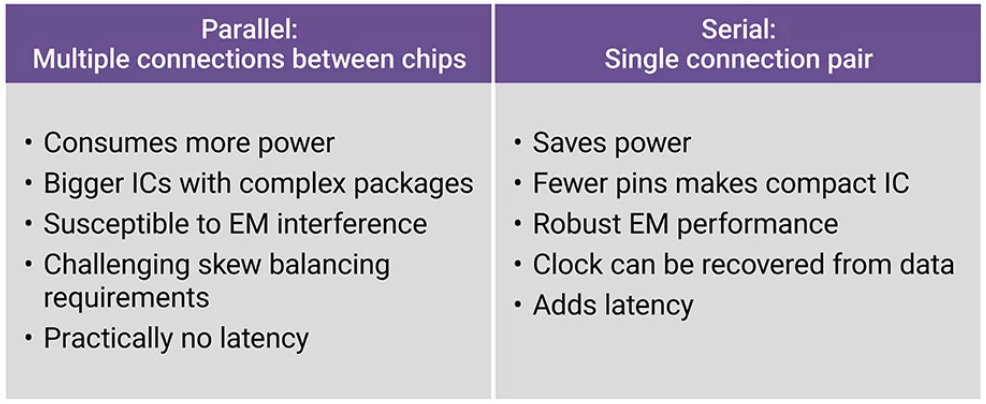

Different protocols suggest various abstraction division for a PHY. For example, 100G PHY defined by IEEE 802.3 \text{IEEE 802.3} IEEE 802.3 has the following abstraction layers:

不同协议对 PHY 的抽象分层有所不同。例如, IEEE 802.3 \text{IEEE 802.3} IEEE 802.3 定义的 100G PHY 包含以下抽象层:

SerDes (serializer/deserializer) Figure 3

SerDes(串行器/解串器)图 3

In this model SerDes will implement PMA/PMD sublayers, which is the logical sub-block responsible for interface initialization, encoding decoding, and clock alignment.

在此模型中,SerDes 会实现 PMA/PMD 子层------这是负责接口初始化、编解码及时钟对齐的逻辑子模块。

一文读懂 SerDes 技术

沱江一苇 原创已于 2022-08-28 21:44:50 修改

本文深入探讨 SerDes 技术,从串行接口技术的发展历程展开论述,详细解析 SerDes 的工作原理,涵盖时钟数据恢复 (CDR)、均衡技术 (Equalization)、时钟生成等内容,并介绍 SerDes 在不同应用场景中的表现。

SerDes Technology

1. Serial Interface Technique Development

串行接口技术发展

1.1 Parallel/Serial Interface

1.1 并行/串行接口

数据传输最初采用低速串行接口(Serial Interface,简称串口),为提升数据总带宽,技术路线转向并行接口(Parallel Interface,简称并口),该接口形式逐步取代传统低速串口成为主流技术方案。随着并口技术的持续发展,其自身存在的局限性逐渐凸显。高速串行(High Speed Serial, HSS)接口技术凭借自身特性,呈现出取代现有并口的发展趋势。

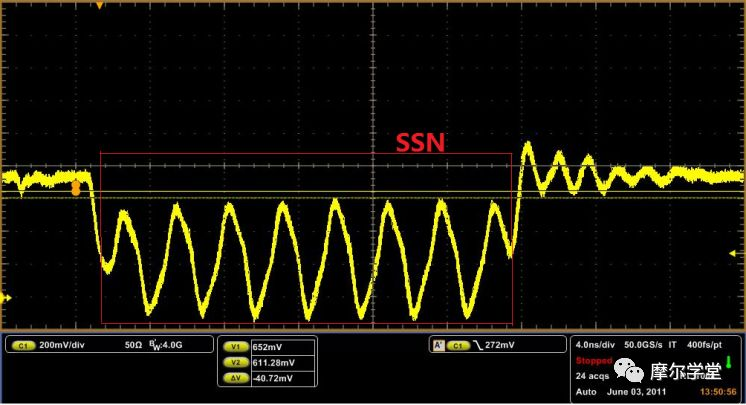

并口技术发展面临的局限性体现在以下方面:芯片 IO 口数量资源紧张;并口数据率提升过程中产生的串扰(Cross-talk)与同步切换噪声(SSN,其表达式为 SSN = L ⋅ N ⋅ d i / d t \text{SSN}=L \cdot N \cdot \text{d}i/\text{d}t SSN=L⋅N⋅di/dt,其中 L L L 代表芯片封装电感, N N N 代表数据位宽, d i / d t \text{d}i/\text{d}t di/dt 代表电流变化斜率),导致数据同步难度增大。

串口与并口的技术演进呈现交替发展的特征。串口技术的典型应用为消费电子领域广泛采用的通用串行总线(Universal Serial Bus, USB);并口技术的典型应用包括 DDR SDRAM 内存接口,即通常所说的 DDRx 系列接口。

针对串口与并口的速率指标,从线速率(line rate)维度分析,以 DDR3-1600 为例,其最大线速率为 1600 Mbps(即 1.6 Gbps);从总数据带宽维度分析,64 bit DDR3-1600 的最大数据带宽超过 100 Gbps(计算方式为 64 × 1.6 Gbps 64 \times 1.6 \ \text{Gbps} 64×1.6 Gbps)。SerDes 同样支持多通道并行工作模式,例如 PCIe 协议定义的 x4、x8、x16 等通道配置模式,该工作模式下需解决多通道间的对齐问题。

高速串口技术的未来发展方向为单通道速率提升与多通道并行应用相结合。在此技术发展趋势下,串口与并口的技术概念界定将进一步模糊,最终达成的数据传输效果为持续优化升级的数据总带宽。

1.2 Chip-Chip Synchronization Technique

1.2 芯片间同步技术

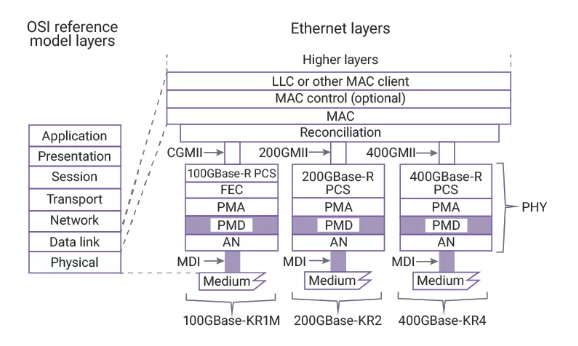

当前主流数字电路系统普遍采用同步电路架构,该架构的核心特征为系统内设置统一时钟信号,用于实现对各类信号的采样操作。芯片间同步接口通信存在三种时序模型,分别为系统同步、源同步与自同步。

在接口速率处于较低水平的阶段,采用系统同步模型即可满足数据传输的时序要求。随着接口速率的提升,更为严苛的时序要求促使技术方案转向数据与时钟同步传输的源同步方式,例如 DDR 接口中,数据线 dq 需与时钟线 dqs 保持同步传输。

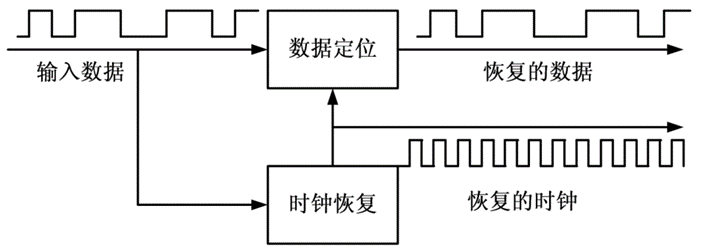

当前 SerDes 技术采用自同步工作方式,接口传输的数据帧中内嵌时钟信息,接收端(Rx)通过时钟数据恢复(Clock Data Recovery, CDR)电路,完成接收数据的时钟提取与数据重采样操作,最终实现正确数据的恢复。

相较于源同步接口,SerDes 接口具备以下技术优势:

(1)数据帧中内嵌时钟信息,无需单独布设时钟信号走线;

(2)通过预均衡/均衡技术,可实现高速信号的长距离传输,典型应用场景包括背板传输;

(3)所需芯片引脚数量更少。

2. SerDes Introduction

2. 串行解串器技术概述

SerDes 技术适用于高速串行链路(High Speed Serial Link)的数据传输场景,其中 Ser 与 Des 分别为串化器(Serializer)与解串器(Deserializer)的缩写形式。该技术的基本功能为将低速并行信号转换为高速低压差分信号(LVDS),并通过串行链路完成信号发送;同时接收串行输入的 LVDS 信号,将其还原为低速并行信号,简言之,SerDes 技术实现并行信号与串行信号之间的双向转换。

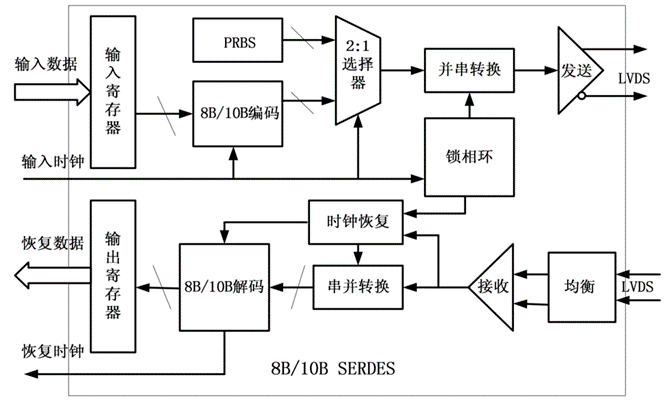

一套完整的 8B/10B SERDES 模块,其 Serializer 单元由 8B/10B 编码器、PRBS 码生成器、并串转换电路、差分信号发送器、PLL 等子模块构成;Deserializer 单元则包含差分信号接收器、CDR(时钟数据恢复电路)、串并转换电路及 8B/10B 解码器。SerDes 技术的典型结构如下图所示。

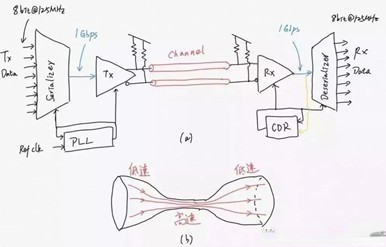

SerDes 接口的简化电路如下图所示。图 (a) 中,时钟速率为 125 MHz 的 8 bit 并行数据(单个时钟周期为 8 ns,对应传输 8 bit 数据),经过 Mux(复用器)芯片的时分复用处理后,转换为 1 Gbps 的 1 bit 串行数据(单个 UI 时长为 1 ns,对应传输 1 bit 数据);该串行数据经发送器与传输通道传输至接收器,接收器输出信号速率仍为 1 Gbps;信号经解串处理后,还原为时钟速率 125 MHz 的 8 bit 并行数据。

SerDes 属于典型的数模混合系统,其研发与设计工作需依托数字电路、模拟电路、信号与系统、通信原理、微波与射频电路、电磁场、信号完整性与电源完整性等多学科理论知识,对技术人员的综合知识储备要求较高,是当前点到点(point-to-point)有线(wireline)通信领域的研究热点。

SerDes 技术的技术要点体现在以下方面:

2.1 Clock generation (high frequency and low jitter)

2.1 时钟生成(高频低抖动)

以 10 Gpbs 数据传输速率为例,系统内部需产生至少 10 GHz 的时钟信号(对应 Single Date Rate, SDR 工作模式)或 5 GHz 的时钟信号(对应 Double Date Rate, DDR 工作模式)。随着 SerDes 技术的发展,系统内部 PLL 的输出时钟频率持续提升,Ring PLL 与 LC tank PLL 成为不可或缺的时钟生成模块。时钟信号的抖动(Jitter)等参数对系统误码率(BER)的影响,需纳入系统设计的考量范畴。

2.2 Equalizer

2.2 均衡器

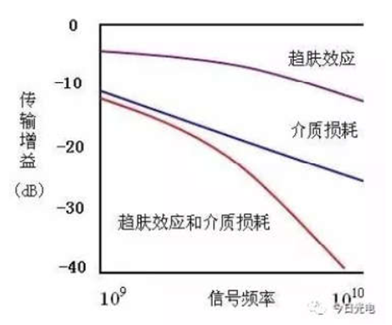

随着信号传输速率的提升与传输链路长度的增加,高速信号传输过程中产生的趋肤效应与传输线介质损耗,导致信号能量在传输过程中出现显著衰减。发送端(Tx)输出的数据信号,因码间干扰(ISI)的影响,到达接收端(Rx)时已发生严重畸变。

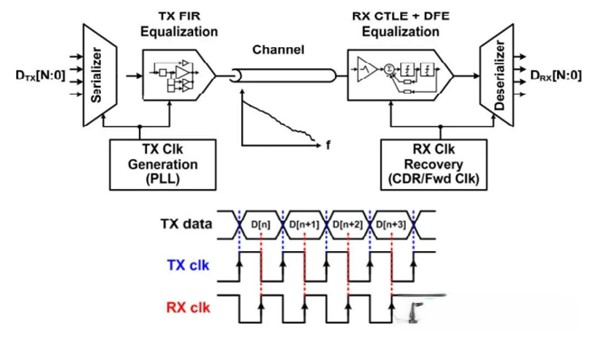

为实现接收端对数据的正确恢复,需通过均衡器(Equalizer)补偿信道衰减与数据码间干扰。发送端(Tx)采用的预均衡器(Pre-Equalizer),通常采用前馈均衡(FFE)架构,需注意预均衡器的参数需与信号传输通道的损耗特性相匹配,方可实现理想的信号改善效果。接收端(Rx)采用连续时间线性均衡(CTLE)与判决前馈均衡(DFE)等技术手段,实际应用中一般采用 CTLE 与 DFE 串联的架构形式。

2.3 Self-Adaptive Algorithm

2.3 自适应算法

接收端(Rx)的均衡器需适配不同材质、不同长度的信道特性,对信号不同频率成分的衰减进行针对性补偿。CTLE 与 DFE 通常搭载自适应算法(Self-Adaptive Algorithm),通过实时动态调整参数,以应对信道特性的变化。

2.4 CDR

2.4 时钟数据恢复

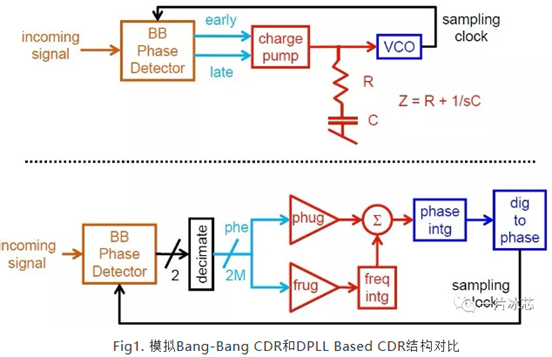

除均衡器(EQ)外,接收端(Rx)的另一项技术难点为时钟数据恢复(Clock and Data Recovery, CDR)环路,该环路存在多种实现架构。CDR 环路通常包含大量数字电路模块,例如 PLL 等。CDR 技术的简化结构如下图所示。

2.5 Timing constraint

2.5 时序约束

随着数据传输速率的提升,系统对 DFE 判决反馈回路的时序设计提出更高要求。以 50 Gbps 传输速率的 SerDes 为例,单个 UI 的时长仅为 20 ps,该时长与逻辑门的延迟时间处于同一量级,这就要求 DFE 反馈回路的逻辑设计需尽可能简化。单纯依靠提升时钟速率的技术路径面临瓶颈,采用 PAM-4 或 PAM-8 等多电平信号调制方式,成为具有发展前景的技术方向。

SerDes 作为复杂的数模混合系统,其内部包含大量数字电路实现模块,例如 8B/10B 编解码模块、PRBS 码生成与校验模块、环回测试模块、自适应算法模块、系统状态控制模块等。

3. SerDes Application

3 串行解串器技术的应用

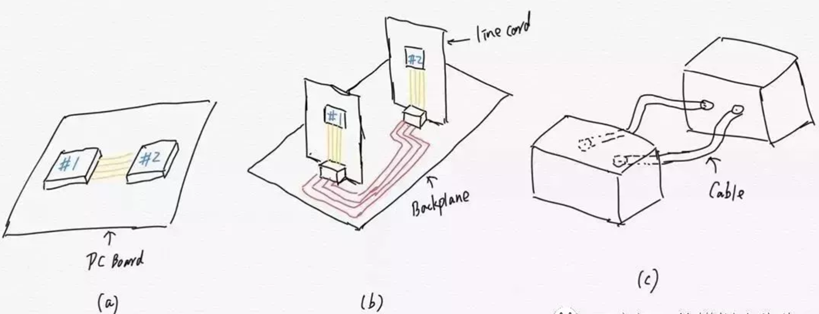

当前 SerDes 技术的应用形式主要包括 Chip-to-Chip、Board-to-Board、Box-to-Box 等,具体应用架构示意图如下图 (a/b/c) 所示。该技术已在大型数据中心、通信骨干网络、消费电子等领域实现广泛应用。

4. SerDes Technical Details

4. 串行解串器技术细节

4.1 SerDes Equalization

4.1 串行解串器均衡技术

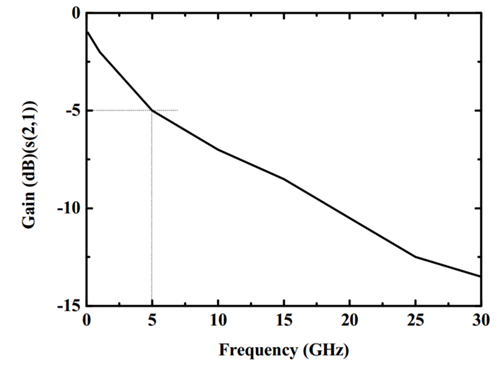

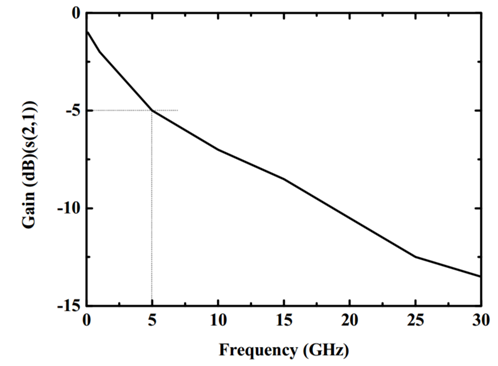

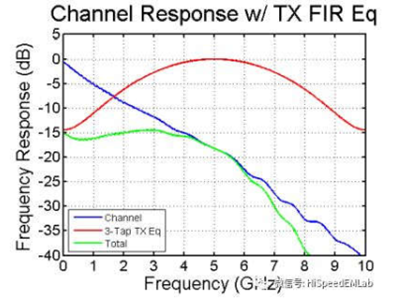

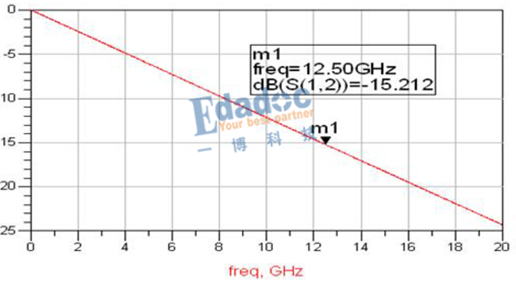

SerDes 信号从发送端传输至接收端所经过的路径,被称为信道(channel)或传输线,其组成部分包括芯片封装、PCB 走线、过孔、电缆、连接器等元件。某类传输线的路径损耗特性如下图所示。

在高速信号传输场景中,信号高频分量的衰减程度远大于低频分量。从频域角度分析,信道对高速信号呈现出低通滤波器(LFP)的特性。当 SerDes 信号传输速率超过信道的截止频率时,信号将发生一定程度的畸变(distort)。均衡器(Equalization)的作用为补偿信道对信号造成的畸变,其频域特性表现为高通滤波器。

均衡技术按照激励源的类型,可划分为无源均衡与有源均衡两大类。

- 无源均衡:其技术原理类似于无源滤波器,通过调整频率响应特性,衰减 SerDes 调制信号 Nyquist 频段内的低频传输损耗,从而实现带宽内的信号均衡。

- 有源均衡:通过有源放大器补偿 SerDes 调制信号 Nyquist 频段内的高频传输损耗,或衰减低频传输损耗,以达成带内信号均衡的目标。

有源均衡技术按照电路架构类型,可分为模拟电路均衡(CTLE)与数字电路均衡(FFE、DFE);按照传递函数的特性,可分为线性均衡(CTLE、FFE)与非线性均衡(DFE)。

搭载均衡器的 SerDes 数据传输链路工作流程如下:

发送端(TX)内部首先完成并行信号至串行信号的转换,同步通过 PLL 生成 Nyquist 频率的时钟信号,将数据调制为 SerDes 信号;根据传输通道的损耗特性,选择适配的 FFE 均衡策略;信号经无源传输通道传输至接收端(RX);接收端内部对 SerDes 信号依次进行线性 CTLE 均衡与非线性 DFE 均衡处理,使信号满足 SerDes 协议一致性要求;随后通过 CDR 内部的 PLL 完成时钟与数据的恢复,并将串行数据转换为并行数据。

4.1.1 Linear EQ & Non-Linear EQ

4.1.1 线性均衡与非线性均衡

对于高速(传输速率 > 5 Gbps)SerDes 系统,信号抖动(例如与码间干扰(ISI)相关的确定性抖动)的幅度可能达到或接近单个符号间隔(UI, Unit Interval),此时单纯采用线性均衡器已无法满足系统性能要求。线性均衡器在放大信号的同时,会同步放大噪声,无法实现信噪比(SNR)或误码率(BER)的改善。针对高速 SerDes 系统,采用判决反馈均衡器(DFE)这类非线性均衡器,可实现更为理想的信号均衡效果。DFE 通过跟踪过去多个 UI 周期内的数据(history bits),预测当前比特的采样门限,其技术优势为仅对信号进行放大,不会放大噪声,可有效提升系统信噪比(SNR)。

4.1.2 TX Equalizer

4.1.2 发送端均衡器

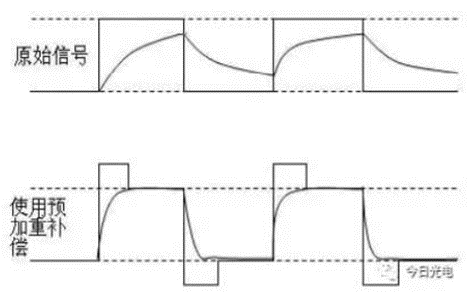

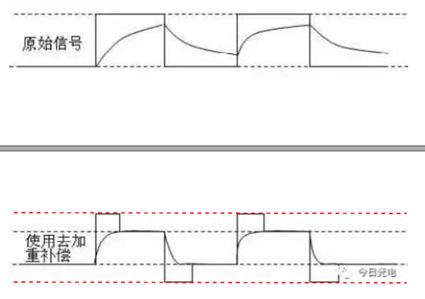

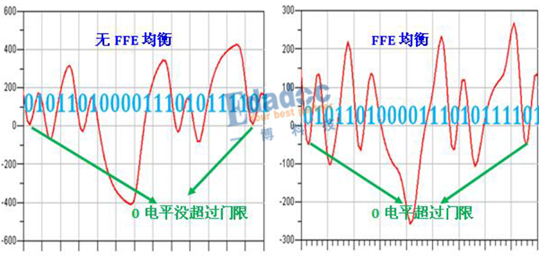

发送端均衡器(TX-EQ)又被称为预均衡器或加重器(emphasis)。加重技术(Emphasis)分为预加重(pre-emphasis)与去加重(de-emphasis)两种类型。

预加重(pre-emphasis)的技术原理为在传输线始端增强信号的高频分量,以补偿高频分量在传输过程中的过度衰减。其技术实现方式为增大差分信号在上升沿与下降沿处的摆幅。

去加重(de-emphasis)与预加重(pre-emphasis)技术原理类似,其技术特点为保持信号上升沿与下降沿处的幅度不变,降低信号在中频频段的摆幅(swing)。FPGA 设备的 SerDes 模块大多采用去加重技术方案,加重程度越高,信号的平均幅度越小。

实际工程应用中,去加重技术的应用更为广泛,原因在于去加重补偿后的信号摆幅更小,眼图高度更低,系统功耗与电磁兼容性(EMC)辐射水平也随之降低。

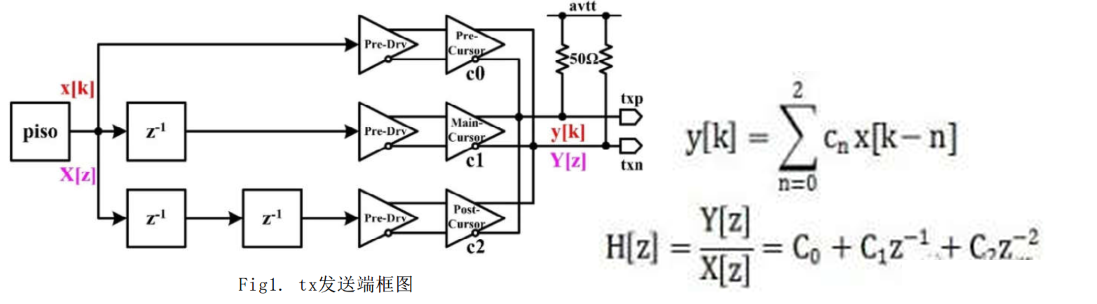

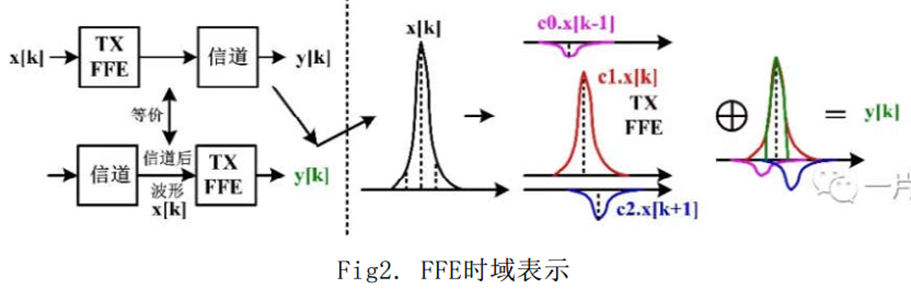

发送端均衡器(TX EQ)采用前馈均衡(FFE)架构,该架构存在多种技术实现方式。FFE 模块部署于发送端,其技术原理为利用信号波形本身对接收信号进行校正,而非通过波形的判决阈值(逻辑 1 或 0)进行校正。

均衡器 FFE 的技术原理类似于离散型多抽头数字有限长单位冲激响应滤波器(Finite Impulse Response, FIR)。该模块在校正当前比特电压时,利用前一比特与当前比特的电压电平,结合校正因子(抽头系数,包含 pre cursor、main cursor、post cursor),实现对当前比特电压电平的校正。简言之,FFE 均衡器通过对实际采集的信号波形执行均衡算法,实现信号改善。当前主流发送端预均衡器的增益水平约为 10 dB。下图为发送端(TX)的系统框图,包含并串转换(piso)、预驱动(Pre-Drv)、均衡器、阻抗匹配等模块,同时标注了时域与 Z 域的数学表达式。

从时域表达式分析,当抽头系数 C 0 C_0 C0 或 C 2 C_2 C2 为负值时,可抑制主信号(main cursor)上的码间干扰(ISI)分量。为实现信号补偿效果, C 0 C_0 C0 与 C 2 C_2 C2 可同时为负值,或一正一负,但不可同时为正值,且三个抽头系数的绝对值之和需等于 1。举例说明:当 C 0 = − 0.1 C_0=-0.1 C0=−0.1、 C 1 = 0.7 C_1=0.7 C1=0.7、 C 2 = − 0.2 C_2=-0.2 C2=−0.2 时,对应去加重工作模式;当 C 0 = − 0.1 C_0=-0.1 C0=−0.1、 C 1 = 1.3 C_1=1.3 C1=1.3、 C 2 = 0.2 C_2=0.2 C2=0.2 时,对应预加重工作模式。

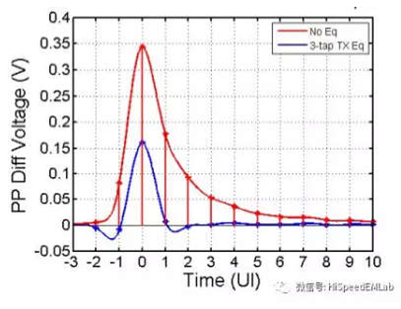

发送端(TX)FIR 滤波器的时域与频域冲击响应如下图所示。左图中蓝色曲线为搭载 EQ 的 TX 信号响应曲线,可清晰观察到在 -1 UI 与 +1 UI 时刻存在校正(加权)因子的作用,相较于红色曲线更为陡峭,体现出高频分量增强的特性。在 0 UI 时刻,信号幅值低于原始信号,表明该技术方案采用去加重模式。

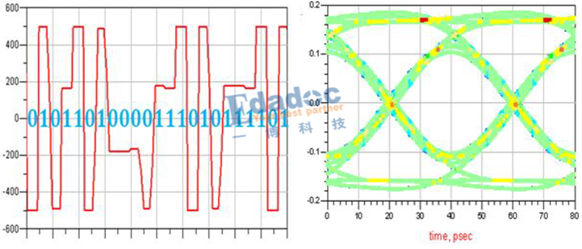

均衡器 FFE 对接收端眼图质量的改善效果,可通过仿真实验进行验证。设定信号传输速率为 25 Gbps,根据下图中传输通道的 S 参数曲线,可读取该通道的损耗值为 -15 dB。

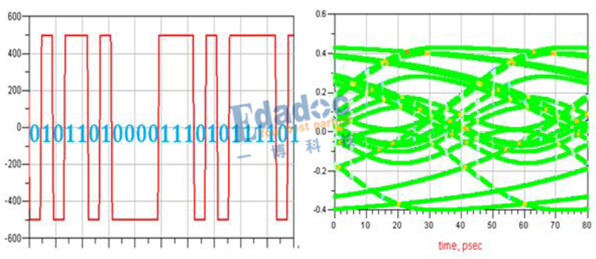

未启用 FFE 均衡器时,发送端波形与接收端眼图如下图所示。

FFE 均衡器在发送端起到高通滤波器的作用,启用 FFE 均衡器后,发送端波形与接收端眼图如下图所示。

启用 FFE 均衡器与未启用 FFE 均衡器两种条件下的接收端波形如下图所示。

在连续传输逻辑 0 或逻辑 1 之后,下一个发生跳变的比特信号,在启用 FFE 均衡器的条件下,更容易被接收端识别。

4.1.3 RX Equalizer

4.1.3 接收端均衡器

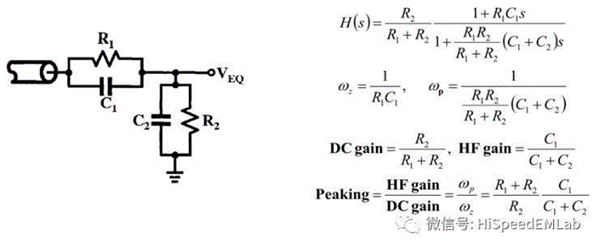

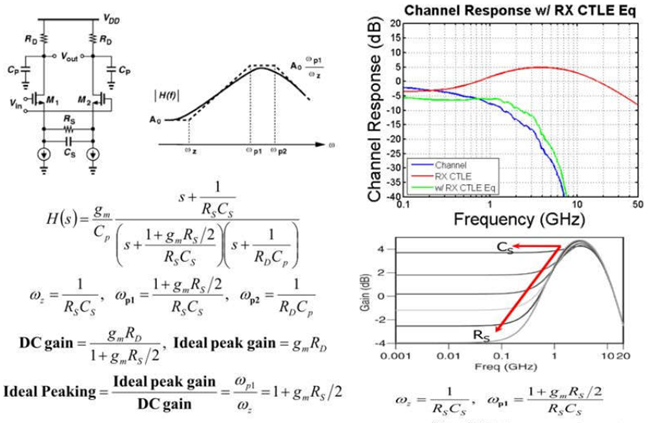

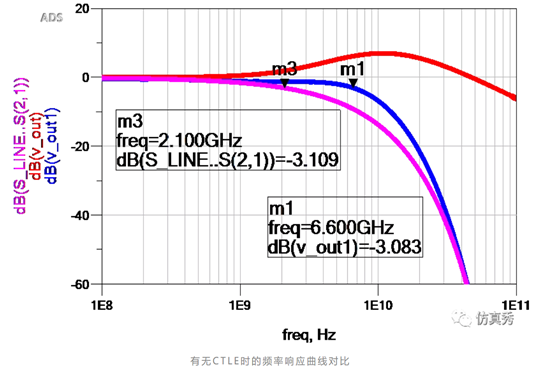

(1)CTLE

连续时间线性均衡(Continuous Time Linear Equalization, CTLE)是高速串行链路中常用的均衡技术。CTLE 的本质为高通滤波器(HFP),其技术实现方式分为无源架构与有源架构两类。无源 CTLE 即无源高通滤波器,其直流增益由电阻参数决定,交流增益由电容参数决定。有源 CTLE 由线性差分放大器构成,RC 电路参数决定滤波器的零极点频率,增益水平由电阻参数与放大器放大倍数共同决定,极点频率受放大器自身带宽的限制。CTLE 均衡器的增益补偿范围通常在 10 dB 左右。

无源 CTLE 架构如下图所示。

有源 CTLE 架构如下图所示。

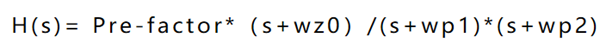

CTLE 的传递函数可进行归一化处理,表达式如下图所示。

式中 Pre-factor = Ideal Peacking \text{Pre-factor} = \text{Ideal Peacking} Pre-factor=Ideal Peacking 为前置系数,其计算公式为 Pre-factor = A dc ⋅ w p 1 ⋅ w p 2 / w z 0 \text{Pre-factor}= A_{\text{dc}}\cdot w_{p1}\cdot w_{p2}/w_{z0} Pre-factor=Adc⋅wp1⋅wp2/wz0。其中 w z 0 w_{z0} wz0 代表零点频率, w p 1 w_{p1} wp1、 w p 2 w_{p2} wp2 代表极点频率, A dc A_{\text{dc}} Adc 为直流增益,其取值范围为 [ 0 , 1 ] [0,1] [0,1],由分压电路参数决定,表征频率为 0 时的信号增益水平。

上述四个参数的取值直接影响 CTLE 频响曲线的形态。CTLE 通过提升传输通道的带宽,实现接收端眼图质量的改善。如下图所示,紫色曲线为未启用 CTLE 时的通道频率响应曲线,红色曲线为 CTLE 自身的频率响应曲线,蓝色曲线为启用 CTLE 后的通道频率响应曲线。

从图中可观察到,蓝色曲线在低频段(2 GHz 以内)与紫色曲线基本重合;在 2 GHz 至 30 GHz 的频段范围内,蓝色曲线位于紫色曲线上方,表明该频段内蓝色曲线对应的信号衰减程度更低。

在 CTLE 的作用下(红色曲线),通道频率响应曲线由紫色曲线调整为蓝色曲线,其增益平坦度相较于原始状态显著提升。

从带宽角度分析,以 3 dB 带宽为评估基准,未启用 CTLE 时,通道带宽仅为 2.1 GHz;启用 CTLE 后,通道带宽可提升至 6.6 GHz,带宽提升至原来的 3 倍。简言之,CTLE 通过提升传输通道的带宽,实现接收端眼图的张开。

(2)DFE

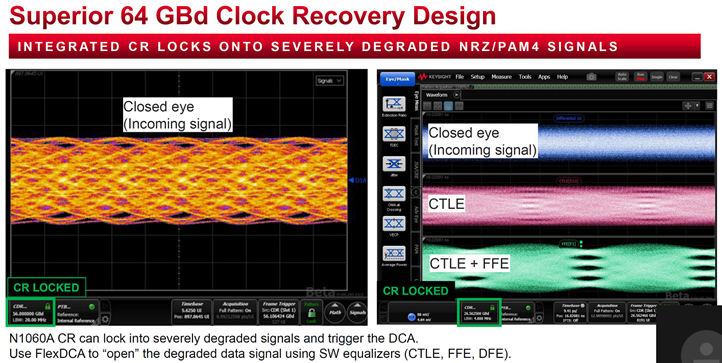

判决反馈均衡(Decision Feedback Equalizer, DFE)属于非线性均衡技术,其技术优势为不会随信号损耗同步放大噪声与串扰(线性均衡器存在此类问题),可有效改善系统信噪比(SNR),因此特别适用于高噪声的应用场景。DFE 的架构组成包括前向 FIR 滤波器、判决器与反馈 FIR 滤波器,该架构对反馈时序与 CDR 鉴相器的性能要求较高,因此实际应用中通常与 CTLE 配合使用。当前主流的 CTLE+DFE 联合均衡方案,其最大增益水平可达 20 dB 左右。

(采样示波器采用 CTLE+FFE 组合方案测试 PAM-4 信号,可获得显著的信号改善效果)

(3)自适应均衡技术

该技术主要应用于接收端(RX),其核心原理为通过分析接收端输入信号,检测信号需要补偿的频谱范围,进而自动调整均衡器的抽头系数与增益参数。可搭载自适应算法的均衡器类型包括 FFE、DFE、CTLE 等。

(4)EQ 技术选择依据

以下为均衡技术的选择建议,实际应用中需结合具体产品的应用场景与协议一致性(Protocol compliance)要求进行调整,同时需考量连接器、过孔、耦合电容、串扰及回流焊工艺等因素带来的信号损耗。

以 Nyquist 频点处的插入损耗(Insertion Loss, 定义为输出端口接收功率 P I P_I PI 与输入源功率的比值)为评估基准:

- 当信道插入损耗小于 6 dB 时,无需采用预均衡或均衡技术;

- 当信道插入损耗处于 6-12 dB 区间时,建议采用预均衡技术;

- 当信道插入损耗处于 12-20 dB 区间时,建议采用预均衡+CTLE 或预均衡+FFE 组合技术方案;

- 当信道插入损耗处于 20-30 dB 区间时,建议采用预均衡+CTLE+DFE 组合技术方案。

4.2 CDR

4.2 时钟数据恢复

为实现对带有频率偏移与抖动的发送端(TX)数据的正确恢复,接收端(PX)通常集成时钟数据恢复(Clock and Data Recovery, CDR)模块。CDR 的功能为通过调整本地时钟信号的相位(phase),对经过信道损耗与各级模块噪声干扰的发送端(TX)串行数据进行重定时处理,确定最佳采样时刻,使接收端(RX)本地时钟信号的边沿与发送端(TX)数据信号的中心位置对齐,实现最佳采样效果,同时降低信号抖动(Jitter)。

4.2.1 CDR Classes

4.2.1 时钟数据恢复的分类

CDR 技术分为模拟架构与数字架构两大类。

- 模拟 CDR 大多采用锁相环(APLL-Based)架构,按照鉴相器的类型,可分为线性鉴相器架构与 Bang-Bang 鉴相器架构,两种架构的传递函数存在差异。

- 数字 CDR 包含过采样(Oversampling)架构与数字锁相环(DPLL-Based)架构。过采样架构对每个 UI 周期内的信号进行多次采样,可提升环路带宽与锁定速度,但因采样次数过多,不适用于高速 Serdes 系统。DPLL-Based 架构由传统 APLL 架构演变而来,其技术特点为将环路中的部分模拟电路(例如模拟滤波器、Bang-Bang 鉴相器)替换为数字电路,可有效降低系统功耗、节省芯片面积,并减小工艺(P)、电压(V)、温度(T)变化对系统性能的影响。

4.2.2 CDR digital

4.2.2 数字式时钟数据恢复

数字 CDR 的技术特点为采用数字累加器,替代模拟 CDR 中的电容积分模块。

根据不同应用场景的技术需求,CDR 存在多种实现架构。FPGA 设备的 SerDes 模块通常采用基于 DPLL 的 CDR 架构与基于相位插值的 CDR 架构,这两种架构的环路中均搭载数字滤波器(Digital Filter)。

CDR 环路具有以下特性:

环路带宽(Loop Bandwidth)决定环路对抖动的处理能力,频率低于环路带宽的抖动分量会被 CDR 捕捉,并转移至恢复时钟信号中,不会导致系统误码;频率高于环路带宽的抖动分量,其对系统的影响取决于抖动幅度的大小,可能引发系统误码。

环路带宽越大,系统在上电捕捉阶段可覆盖的噪声范围越广,锁定时间越短,但恢复时钟信号的抖动幅度也越大;反之,环路带宽越小,系统锁定时间越长,恢复时钟信号的抖动幅度也越小。

环路参数的计算可参考以下文献资料:

1\] DPLL-Based Clock and Data Recovery-PPT.

\[2\] DPLL-Based Clock and Data Recovery-ISSCC.

\[3\] Sonntag J L, Stonick J. A Digital Clock and Data Recovery Architecture for Multi-Gigabit/s Binary Links\[J\]. IEEE Journal of Solid-State Circuits, 2006, 41(8):1867-1875

#### 4.3 PLL

##### 4.3 锁相环

SerDes 系统内部所需的时钟信号,其频率对应数据波特率(SDR 工作模式),或为数据波特率的 1/2(DDR 双边沿采样工作模式)。然而,外部输入至 SerDes 系统的参考时钟频率,往往远低于系统内部所需的时钟频率,因此需通过锁相环(PLL)实现时钟信号的倍频,生成满足系统要求的高频时钟信号。举例说明:FPGA 设备的 SerDes PLL 通常支持 8x、20x、40x 等倍频模式,当 PCIe 协议工作在 5 Gbps 速率时,采用 20x 倍频模式的 FPGA SerDes 仅需外部输入 250 MHz 的参考时钟信号;采用 40x 倍频模式时,仅需外部输入 125 MHz 的参考时钟信号。

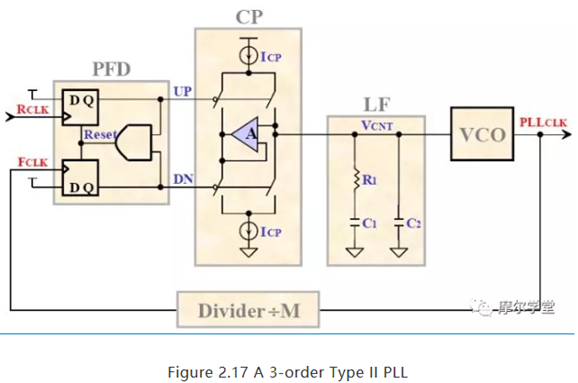

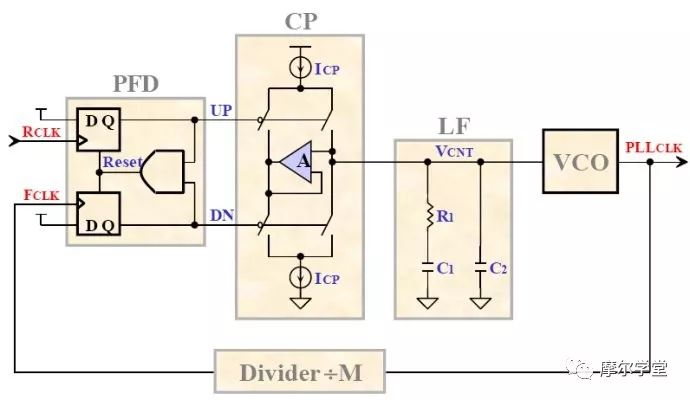

三阶 PLL 电路的典型架构如下图所示。输入信号 RCLK 的相位(phase)与反馈信号 FCLK 的相位(phase)输入至鉴相器进行相位比较,相位误差信号经电荷泵(CP charge pump)转换为电压或电流信号;该信号经环路滤波器(Loop Filter)滤波后,生成控制电压信号;控制电压信号调节压控振荡器(VCO)的输出频率,即调整 FCLK 的相位,最终使环路的相位误差趋近于 0。

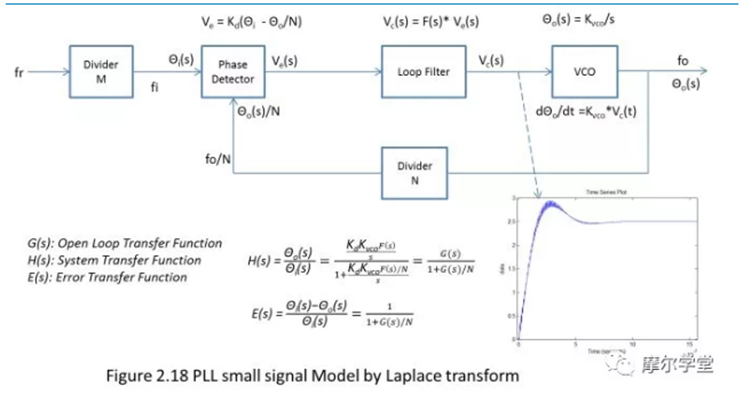

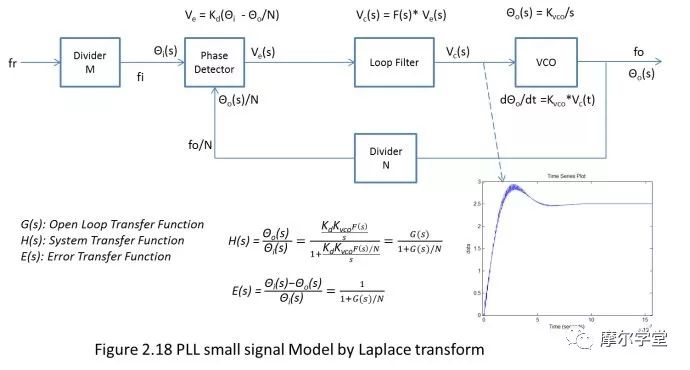

PLL 的工作过程分为捕获与跟踪两个阶段。在捕获阶段,环路的数学模型可采用非线性微分方程描述,通过该模型可评估环路的捕获时间、捕获带宽等性能指标。在跟踪阶段,小信号范围内,PLL 的数学模型可简化为常系数线性方程,可在拉普拉斯域(Laplace 域)分析环路的带宽(Bandwidth)、增益(Gain)与系统稳定性(Stability)等特性。PLL 小信号模型如下图所示。

PLL 的环路阶数由环路极点的数量决定。压控振荡器(VCO)对相位具有积分作用(其传递函数为 K vco / s K_{\\text{vco}}/s Kvco/s),因此未搭载环路滤波器的 PLL 被称为一阶环,搭载环路滤波器的 PLL 被称为二阶环。一阶环与二阶环均属于无条件稳定系统。高阶环路拥有更多可独立调整的零点与极点,可实现对环路带宽、增益、系统稳定性、捕获带宽、捕获时间等性能指标的灵活优化。

当 PLL 环路实现锁定后,输入信号 RCLK 与反馈信号 FCLK 之间仅存在固定相位差,两者的频率保持一致。

对于输入端引入的噪声,PLL 环路呈现低通滤波器的特性,可抑制频率高于环路截止频率(-3 dB 频点)的噪声或干扰信号。应用于 SerDes 系统的 PLL,通常设计为较小的环路带宽,以实现对参考时钟干扰与噪声的有效抑制。

#### 4.4 Channel SI

##### 4.4 信道信号完整性

信道的频率响应分析范围为 0 Hz 至 Nyquist 频率,Nyquist 频率的数值为信号基频的 2 倍。举例说明:当信号传输速率为 5 Gbps(采用 NRZ 调制方式),假设信号以最大基频传输(传输码型为 01010101),则 1 秒内传输 2.5 Gbit 的逻辑 1 与 2.5 Gbit 的逻辑 0,信号基频为 2.5 GHz,对应的 Nyquist 采样频率为 5 GHz。

信道对信号造成的损伤包括插入损耗(Insertion Loss)、反射(reflection)、串扰(crosstalk),这些参数均可通过 S 参数(S-parameter)对信道特性进行表征。S 参数可通过矢量网络分析仪(Vector Network Analyzer)测量获得。信道并非纯阻性网络,其等效模型包含感性与容性元件,不同频率成分的信号在信道中传输时产生的时延存在差异,由此引发与频率相关的抖动。

*** ** * ** ***

## 深入理解 SerDes

摩尔学堂 2023-10-13 09:31

FPGA 发展至今,SerDes(Serializer-Deserializer)已成为器件的标准配置。从 PCI 到 PCI-E、从 ATA 到 SATA、从并行 ADC 接口到 JESD204、从 RIO 到 Serial RIO 等技术演进,均借助 SerDes 实现数据传输性能的提升。SerDes 属于复杂的数模混合设计,用户手册仅对相关概念与使用方法进行概述,无法完整阐释其工作原理。设计者在使用 SerDes 的过程中会面临诸多疑问:数据传输过程中为何不包含时钟信号?加重与均衡的定义是什么?抖动与误码存在何种关联?各类抖动之间的相互关系是什么?时钟恢复的实现方式是什么?若设计者能够厘清上述问题,SerDes 的开发工作将得以顺利开展。本文从 SerDes 用户的视角出发,对其设计原理展开分析。

### SerDes 的价值

### 并行总线接口

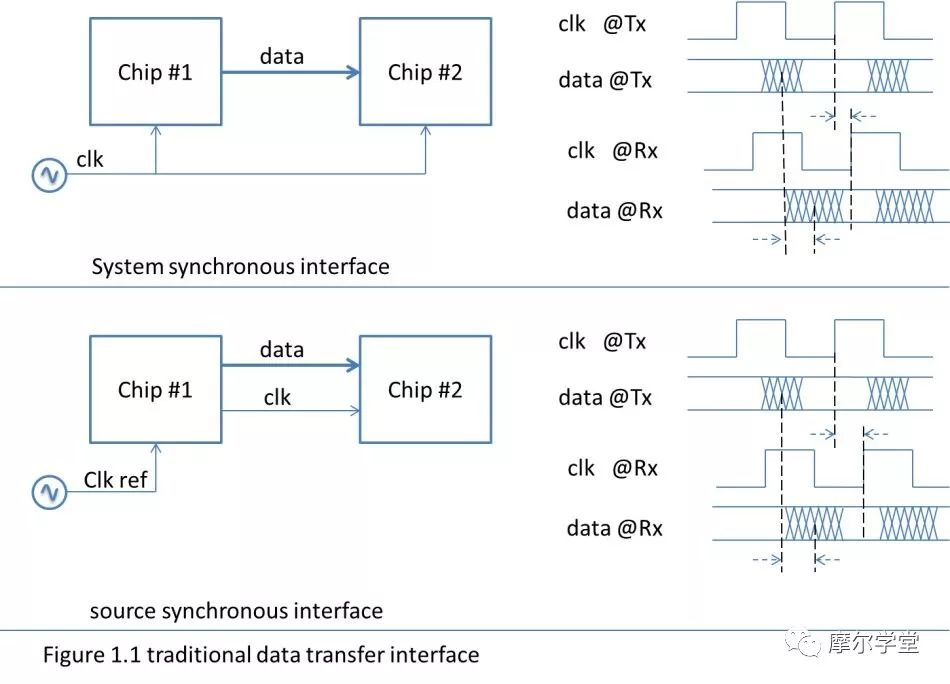

芯片间的数据传输最初采用串行传输方式,随着数据量的持续增长,串行数据传输速率较低的缺点逐渐凸显。为此,芯片设计者通过增加数据传输位宽,采用并行传输方式以实现高于串行传输的速率。芯片间的互连通常通过系统同步或源同步的并行接口完成数据传输。图 1.1 展示了系统同步与源同步并行接口的结构。

随着接口频率的升高,系统同步接口的有效数据位宽增长受到以下因素的限制:

* 时钟信号到达两个芯片的传播延时存在差异(clock skew)

* 并行数据各 bit 的传播延时存在差异(data skew)

* 时钟信号与数据信号的传播延时存在差异(skew between data and clock)

虽然可以在目的芯片(chip #2)内部利用 PLL 补偿时钟延时差(clock skew),但在 PVT(Process Voltage Temperature)条件发生变化时,时钟沿的变化量与数据延时的变化量并不一致。这一现象会进一步压缩数据窗口,即无法通过单纯增加数据总线位数的方式提升数据传输速率。

在源同步接口方式中,发送端 Tx 将时钟信号与数据信号一同发送,以此降低 clock skew 对有效数据窗口的影响。通常在发送端芯片内部,源同步接口会将时钟信号与数据信号视为同类信号进行处理,即让两类信号经过相同的传输路径,以保证两者的延时一致。在此情况下,当 PVT 条件发生变化时,时钟信号与数据信号的延时会向同一方向呈现相同幅度的增减,有利于减小 skew 带来的负面影响。

基于以下典型假设条件,对 32 bit 并行总线的性能进行分析:

1. 发送端的数据 skew = 50 ps(较高设计要求)

2. PCB 总线引入的 skew = 50 ps(较高设计要求)

3. 时钟的周期抖动 jitter = ± 50 ps(较高设计要求)

4. 接收端触发器采样窗口 = 250 ps(Xilinx V7 高端器件的 IO 触发器参数)

通过计算可得并行接口的最高时钟频率为:

f max = 1 50 ps + 50 ps + 100 ps + 250 ps = 2.2 GHz (DDR) f_{\\text{max}}=\\frac{1}{50\\ \\text{ps}+50\\ \\text{ps}+100\\ \\text{ps}+250\\ \\text{ps}}=2.2\\ \\text{GHz (DDR)} fmax=50 ps+50 ps+100 ps+250 ps1=2.2 GHz (DDR)

或对应 **1.1 GHz (SDR)**。

采用源同步接口可显著提升数据的有效窗口,其工作频率通常低于 1 GHz。在实际应用中,SPI4.2 接口的时钟频率可达到 DDR 700 MHz × 16 bits 位宽;DDR Memory 接口同样属于源同步接口,例如 DDR3 在 FPGA 中的时钟频率可达到约 800 MHz(DDR)。

提升接口传输带宽的方式包括两种:提高时钟频率与增大数据位宽。那么数据位宽是否可以无限制增大?这一问题需考虑同步切换噪声(SSN)的影响。

SSN 的计算公式为:

SSN = L × N × d i d t \\text{SSN}=L\\times N\\times\\frac{di}{dt} SSN=L×N×dtdi

式中, L L L 为芯片封装电感, N N N 为数据位宽, d i d t \\frac{di}{dt} dtdi 为电流变化斜率。随着频率升高与数据位宽增大,SSN 逐渐成为限制传输带宽提升的主要因素。图 1.2 为 DDR3 串扰的实例,低电平的理论值为 0 V,受 SSN 影响,低电平呈现震荡状态,震荡噪声的最大值达到 610 mV,由此计算可得噪声余量为:

1.5 V 2 − 610 mV = 140 mV \\frac{1.5\\ \\text{V}}{2}-610\\ \\text{mV}=140\\ \\text{mV} 21.5 V−610 mV=140 mV

由此可见,无法通过无限制增大数据位宽的方式提升带宽。解决 SSN 问题的一种方法是采用差分信号替代单端信号,该方法可有效抑制 SSN,但代价是需要占用更多的芯片引脚。此外,差分信号的使用无法解决数据 skew 问题,大位宽差分信号结合严格的时序约束,给并行接口的设计带来了极大挑战。

### SerDes 接口

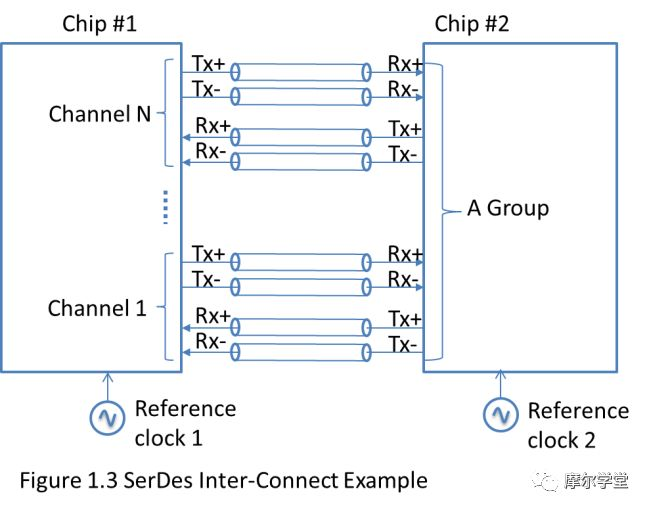

源同步接口的时钟频率已达到瓶颈,由于信道(channel)的非理想特性,若继续提升频率,信号会受到严重损伤,此时需要采用均衡与数据时钟相位检测等技术,这正是 SerDes 所采用的核心技术路径。SerDes 是串行器(Serializer)与解串器(Deserializer)的简称,其中串行器也称为 SerDes 发送端(Tx),解串器也称为接收端(Rx)。图 1.3 展示了 N 对 SerDes 收发通道的互连结构,通常 N N N 小于 4。

可以看到,SerDes 不单独传输时钟信号,这是其显著特征。SerDes 在接收端集成了时钟数据恢复(CDR,Clock Data Recovery)电路,CDR 可从数据的边沿信息中提取时钟信号,并确定最优采样位置。

SerDes 采用差分方式传输数据,通常多个通道会被划分为一个组(group),以共享 PLL 资源,且每个通道仍保持独立工作状态。

SerDes 需要参考时钟(Reference Clock),该时钟一般采用差分形式以降低噪声。接收端 Rx 与发送端 Tx 的参考时钟允许存在数百 ppm 的频率偏差(准同步系统,plesio-synchronous system),也可采用同频时钟,且对相位差无特定要求。

通过简单对比可以看出 SerDes 的优势:单个 SerDes 通道(Channel)仅需 4 个引脚(Tx+/-, Rx+/-),目前 FPGA 的 SerDes 通道速率可达到 28 Gbps;而 16 bit 的 DDR3-1600 接口的线速率为 1.6 Gbps × 16 = 25 Gbps 1.6\\ \\text{Gbps} \\times 16=25\\ \\text{Gbps} 1.6 Gbps×16=25 Gbps,却需要占用 50 余个引脚。

与源同步接口相比,SerDes 具有以下特点:

* 时钟信号内嵌于数据线中,无需单独传输时钟信号

* 通过加重/均衡技术可实现高速长距离传输,例如背板传输场景

* 占用的芯片引脚数量较少

### 中间类型

存在一类介于 SerDes 与并行接口之间的接口类型,这类接口与源同步接口相比,同样采用串行器与解串器,同时会传输用于同步的时钟信号。视频显示接口 7:1 LVDS 即属于此类接口。

### SerDes 结构

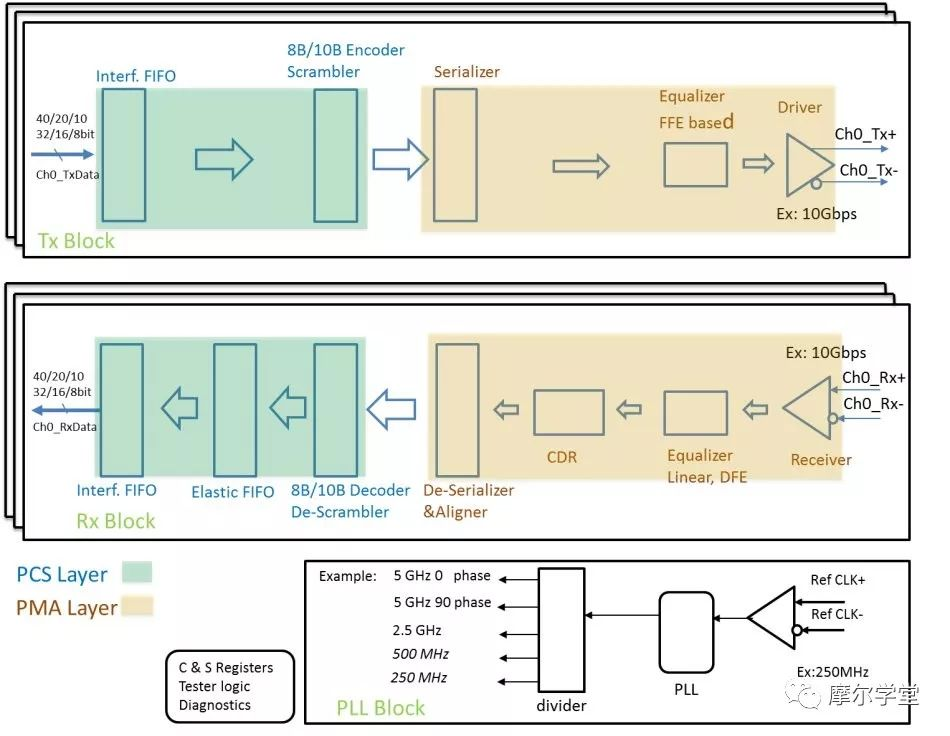

SerDes 的主要组成部分包括三部分:PLL 模块、发送模块 Tx、接收模块 Rx。为便于维护与测试,SerDes 还集成了控制和状态寄存器、环路测试、伪随机二进制序列(PRBS)测试等功能,结构如图 2.1 所示。

图中蓝色背景的子模块为物理编码子层(PCS,Physical Coding Sublayer),该层采用标准的可综合 CMOS 数字逻辑实现,既可使用硬件逻辑,也可通过 FPGA 软逻辑实现,原理相对易于理解。褐色背景的子模块为物理介质连接层(PMA,Physical Medium Attachment),该层采用数模混合 CML/CMOS 电路设计,是理解 SerDes 区别于并行接口的关键,也是本文的重点讨论内容。

发送端(Tx)的信号流向为:FPGA 逻辑(Fabric)输出的并行信号通过接口 FIFO(Interface FIFO)传输至 8B/10B 编码器(8B/10B encoder)或扰码器(scrambler),以此避免数据中出现连续的 0 或连续的 1。处理后的信号送入串行器(Serializer)完成并串转换,串行数据经过均衡器(equalizer)调理后,由驱动器(driver)发送至信道。

接收端(Rx)的信号流向为:外部串行信号经过线性均衡器(Linear Equalizer)或判决反馈均衡器(DFE,Decision Feedback Equalizer)调理,以消除部分确定性抖动(Deterministic Jitter)。CDR 从数据中恢复采样时钟,解串器将串行信号转换为对齐的并行信号。8B/10B 解码器(8B/10B decoder)或解扰器(de-scrambler)完成解码或解扰操作。若系统为异步时钟系统(Plesio-synchronous system),则在用户 FIFO 前需设置弹性 FIFO,用于补偿频率偏差。

PLL 的作用是生成 SerDes 各模块所需的时钟信号,并管理各时钟之间的相位关系。以线速率 10 Gbps 为例,参考时钟频率为 250 MHz,此时 Serializer/Deserializer 至少需要 5 GHz 0 相位时钟、5 GHz 90 度相位时钟,以及 1 GHz(对应 10 bit 并行数据)或 1.25 GHz(对应 8 bit 并行数据)的时钟信号。

SerDes 通常具备调试功能,例如伪随机码流的生成与比对、各类环回测试、控制状态寄存器及访问接口、信号丢失(LOS)检测、在线测试等。

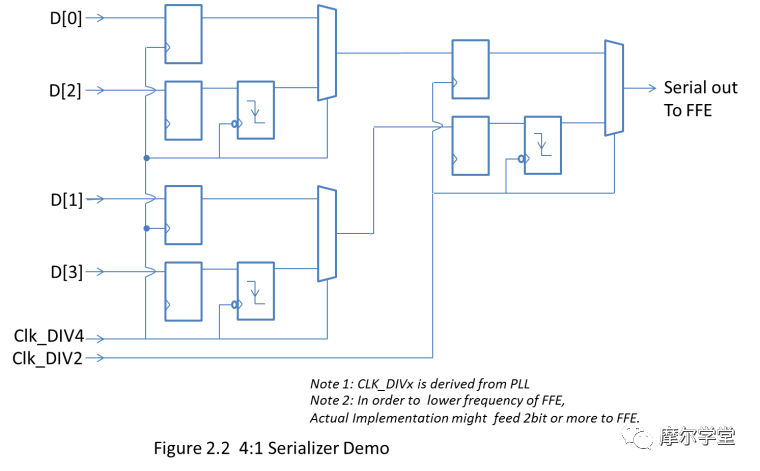

### 串行器与解串器

串行器(Serializer)的功能是将并行信号转换为串行信号,解串器(Deserializer)的功能是将串行信号转换为并行信号。通常并行信号的位宽为 8/10 bit 或 16/20 bit,串行信号的位宽为 1 bit(也可采用分阶段串行化方式,例如 8 bit→4 bit→2 bit→1 bit,以降低均衡器的工作频率)。采用扰码(scrambled)协议的 SDH/SONET、SMPTE SDI 接口通常使用 8/16 bit 的并行位宽;采用 8B/10B 编码协议的 PCI-Express 接口、采用 10 bit/20 bit 位宽的千兆以太网(GbE)接口也属于此类应用场景。

图 2.2 展示了 4:1 串行器的结构,8:1 或 16:1 串行器可采用类似原理实现。在实际设计中,为降低均衡器的工作频率,串行器会先将并行数据转换为 2 bit 宽度,再送入均衡器进行滤波,最后通过 2:1 串行化完成最终转换。

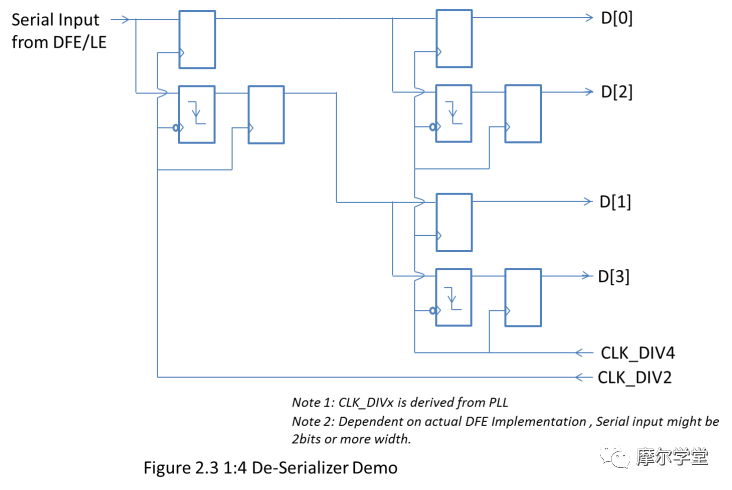

图 2.3 展示了 1:4 解串器的结构,8:1 或 16:1 解串器可采用类似原理实现。在实际设计中,为降低均衡器的工作频率,均衡器工作在双倍数据率(DDR)模式下,解串器的输入信号位宽为 2 bit 或更宽。

串行器与解串器采用双沿 DDR 工作方式,通过面积换速度的设计策略,降低电路中高频模块的占比,从而减小电路的噪声水平。

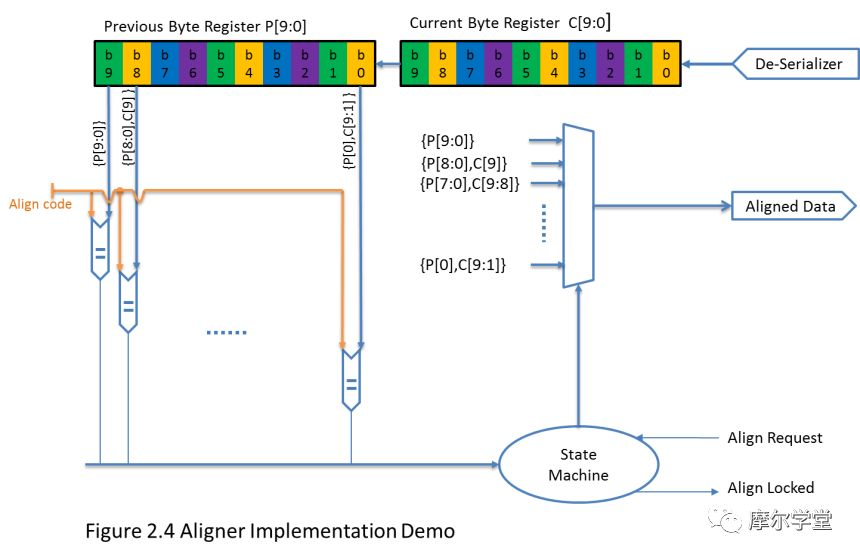

接收端除解串器外,通常还配置对齐功能逻辑(Aligner)。由于 SerDes 接收端的启动时刻具有随机性,接收器接收到的第一个 bit 可能对应发送端并行数据的任意位置。因此需要通过对齐逻辑确定串并转换的起始位置,以恢复正确的并行数据。对齐逻辑的工作原理是在串行数据流中搜索特征码字(Alignment Code),例如采用 8B/10B 编码协议的接口通常以 K28.5(正码为 10 ′ b 1110000011 10'\\text{b}1110000011 10′b1110000011,负码为 10 ′ b 0001111100 10'\\text{b}0001111100 10′b0001111100)作为对齐字。图 2.4 展示了对齐逻辑的工作流程,通过滑动窗口逐 bit 比对,确定对齐码的位置,当多次在同一位置检测到对齐码后,状态机锁定该位置,并输出对齐后的并行数据。

### 发送均衡器(Tx Equalizer)

SerDes 信号从发送芯片传输至接收芯片所经过的路径称为信道(Channel),信道包括芯片封装、PCB 总线、过孔、电缆、连接器等部件。从频域角度分析,信道可简化为低通滤波器(LPF)模型,若 SerDes 的信号速率超过信道的截止频率,信号会受到明显损伤。均衡器的作用是补偿信道对信号的损伤。

发送端均衡器采用前馈均衡器(FFE,Feed Forward Equalizer)结构,发送端均衡器也被称为加重器(emphasis)。加重技术分为去加重(de-emphasis)与预加重(pre-emphasis)两种类型:去加重通过降低差分信号的摆幅(swing)实现;预加重通过增大差分信号的摆幅实现。FPGA 中的 SerDes 大多采用去加重方式,加重程度越高,信号的平均幅度越小。

发送端均衡器被设计为高通滤波器(HPF),其频率响应近似为信道频率响应 H ( f ) H(f) H(f) 的逆函数。FFE 的设计目标是使接收端接收到的信号保持完整性,FFE 具有多种实现方式,典型结构如图 2.5 所示。

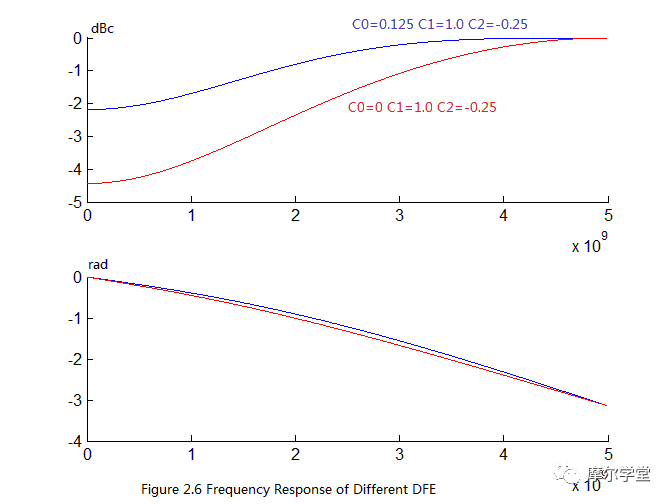

通过调节滤波器系数可改变其频率响应,以适配不同的信道特性,且系数通常支持动态配置。以 10 Gbps 线速率为例,图 2.6 展示了 FFE 的频率响应特性,当配置系数为 C 0 = 0 C_0=0 C0=0、 C 1 = 1 C_1=1 C1=1、 C 2 = − 0.25 C_2=-0.25 C2=−0.25 时,5 GHz 频段的高频增益比低频段高出 4 dB,从而补偿信道对高频信号的衰减。

采样时钟频率限制了 FFE 的最高补偿频率,其上限为 F s / 2 F_s/2 Fs/2(上述例子中 F s / 2 = 5 GHz F_s/2=5\\ \\text{GHz} Fs/2=5 GHz)。根据采样定理,串行数据的全部信息均包含在 5 GHz 以内的频段,因此该补偿范围已能满足需求。若需补偿 F s / 2 F_s/2 Fs/2 以上的频率,则需提高 FFE 的工作频率,或采用连续时间域滤波器(Continuous Time FFE)。

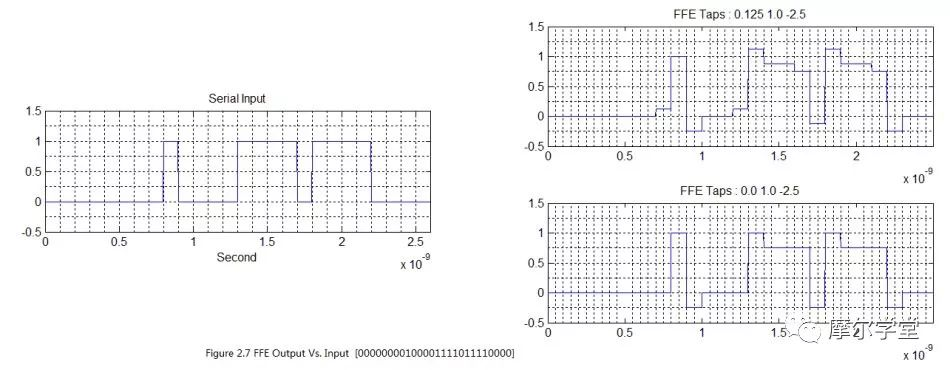

图 2.7 展示了 FFE 的时序滤波效果,以 10 Gbps 线速率为例,此时单位间隔(UI,Unit Interval)为 0.1 ns = 100 ps 0.1\\ \\text{ns}=100\\ \\text{ps} 0.1 ns=100 ps,演示所用的串行数据码流为二进制序列 \[ 00000000100001111011110000 \] \[00000000100001111011110000\] \[00000000100001111011110000\]。

### 2.3 接收端均衡器 (Rx Equalizer)

#### 2.3.1 线性均衡器 (Linear Equalizer)

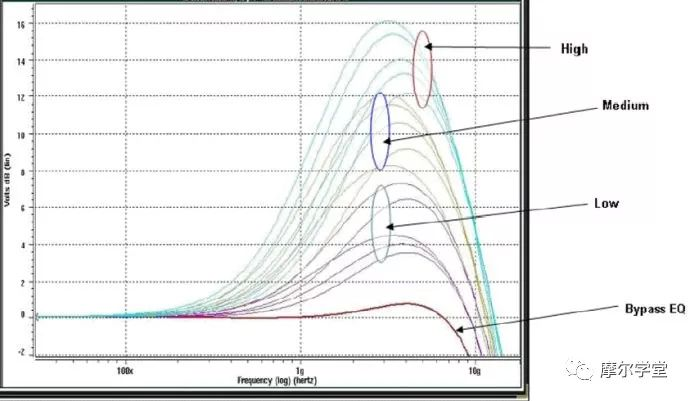

接收端均衡器的设计目标与发送端均衡器一致。对于低速(\< 5 Gbps)SerDes,通常采用连续时间域线性均衡器,例如峰值放大器(peaking amplifier),该类均衡器对高频分量的增益高于对低频分量的增益。图 2.8 展示了基于峰值放大器的 Rx 均衡器的频率响应特性。厂商通常会将均衡特性封装为多种等级,例如高/中/低(High/Med/Low)等,支持动态配置以适配不同的信道特性。

*Figure 2.8 Frequency Response of A peaking Amplifier based Rx Equalizer*

#### 2.3.2 DFE 均衡器 (Decision Feedback Equalizer)

对于高速(\> 5 Gbps)SerDes,信号抖动(例如与码间干扰 ISI 相关的确定性抖动)的幅度可能超过或接近一个单位间隔(UI),此时单纯使用线性均衡器已无法满足需求。线性均衡器会同时放大信号与噪声,无法改善信噪比(SNR)或误码率(BER)。因此,高速 SerDes 通常采用非线性均衡器------判决反馈均衡器(DFE,Decision Feedback Equalizer)。DFE 通过跟踪前若干个 UI 的数据(历史比特,history bits)预测当前比特的采样门限,仅对信号进行放大,不会放大噪声,可有效提升 SNR。

图 2.9 展示了典型的 5 阶 DFE 结构。接收的串行数据经比较器(slicer)判决为 0 或 1,判决后的数据流送入滤波器以预测码间干扰(ISI),随后从原始输入信号中减去该干扰分量,从而得到恢复后的完整信号。为使 DFE 均衡器工作在线性区间,串行信号需先经过可变增益放大器(VGA),以自动控制进入 DFE 的信号幅度。

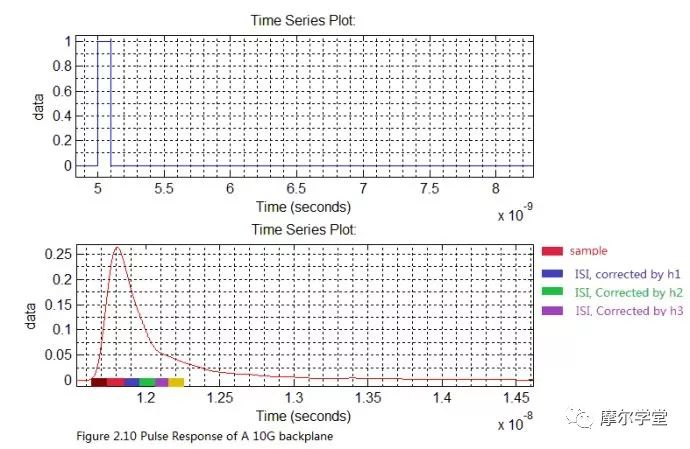

为阐释 DFE 的工作原理,以 10 Gbps 背板的脉冲响应为例进行分析,该背板模型由 Matlab 基于实测数据构建,具有典型的信道特性。

图 2.10 中,每个横向格子代表一个 UI 的时间。可以观察到,一个 UI( 0.1 ns = 1 / 10 GHz 0.1\\ \\text{ns}=1/10\\ \\text{GHz} 0.1 ns=1/10 GHz)的脉冲信号经过背板传输后,能量会泄漏到前后多个相邻的 UI 中,从而对其他 UI 的数据产生干扰。采样点之后的干扰称为后光标干扰(post-cursor 干扰),采样点之前的干扰称为前光标干扰(pre-cursor 干扰)。DFE 的第一个系数 h 1 h_1 h1(本例中为 0.175)用于补偿第一个 post-cursor 干扰,第二个系数 h 2 h_2 h2(本例中为 0.075)用于补偿第二个 post-cursor 干扰。DFE 的阶数越高,可补偿的 post-cursor 干扰数量越多。

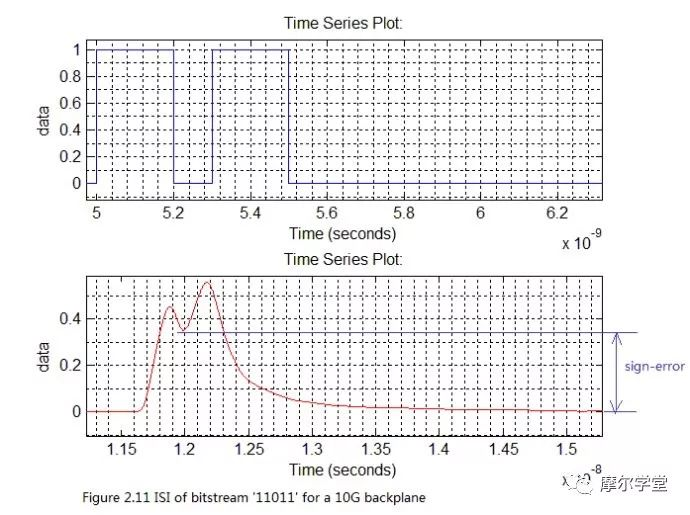

以码流 11011 经过背板传输的过程为例,若无均衡处理,受 post-cursor 与 pre-cursor 干扰的影响,码流中的"0"比特将无法被正确识别,如图 2.11 所示。假设采用 2 阶 DFE,则"0"比特处的信号幅度需减去前两个"1"比特对应的干扰分量,计算过程如下:

0.35 − 0.075 − 0.175 = 0.1 0.35-0.075-0.175=0.1 0.35−0.075−0.175=0.1

该幅度足以支持"0"比特的正确识别。

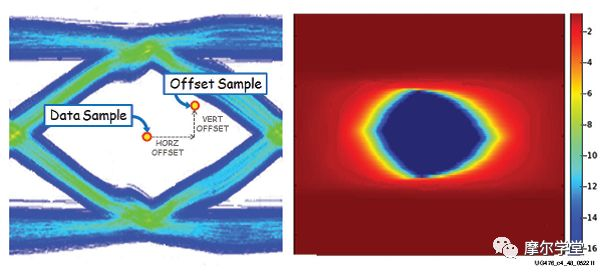

由此可见,DFE 通过计算历史比特的 post-cursor 干扰,并从当前比特的信号中扣除该干扰,实现信号的恢复。由于 DFE 仅能补偿 post-cursor ISI,因此通常在 DFE 前级配置线性均衡器(LE)。当 DFE 的系数与信道的脉冲响应特性匹配时,可获得理想的均衡效果。但信道特性会随时间变化,例如温度、电压、工艺等条件的缓慢变化都会改变信道特性,因此 DFE 的系数需要通过自适应算法实时捕获并跟踪信道变化。DFE 系数的自适应算法属于学术研究与厂商技术保密范畴,未对外公开。对于不归零码(NRZ),典型算法准则基于符号误差驱动(sign-error driven),该算法以符号误差的均方差最小为优化目标,逐次迭代优化系数 h 1 / h 2 / h 3 ... h_1/h_2/h_3\\dots h1/h2/h3...。由于符号误差与采样位置存在耦合关系,因此也可同时以符号误差与眼图宽度作为优化目标进行 DFE 系数预测。基于此,采用 DFE 结构的 SerDes 通常集成内嵌眼图测试电路,如图 2.9 所示。眼图测试电路通过在垂直方向调整信号幅度、在水平方向调整采样位置,计算每个调整位置对应的误码率(BER),从而得到偏移位置与误码率的关系曲线,即"眼图",如图 2.12 所示。

*Figure 2.12 SerDes Embedded Eye-Diagram Test Function*

### 2.4 时钟数据恢复 (CDR)

CDR 的设计目标是确定信号的最佳采样时刻,这要求数据信号具备丰富的跳变沿。CDR 存在一项关键指标------最长连 0/连 1 长度容忍能力(Max Run Length 或 Consecutive Identical Digits)。若数据信号长时间无跳变,CDR 将无法进行精确的时钟训练,采样时刻会发生漂移,可能导致采样结果中出现过多的 1 或 0。当数据信号恢复跳变时,甚至可能出现采样错误。例如,部分基于 PLL 实现的 CDR,若数据长时间无跳变,PLL 的输出频率会发生漂移。实际上,SerDes 传输的数据通常通过扰码或编码方式,将最长连 0/连 1 长度限制在特定范围内:

* 8B/10B 编码可保证最长连 0/连 1 长度不超过 5 个 UI

* 64B/66B 编码可保证最长连 0/连 1 长度不超过 66 个 UI

* SONET/SDH 扰码方式可保证在误码率 B E R \< 10 − 12 BER\<10\^{-12} BER\<10−12 条件下,最长连 0/连 1 长度不超过 80 个 UI

在点到点连接场景中,多数 SerDes 协议采用连续模式(continuous-mode),即线路上的数据流持续传输且无中断。在点到多点连接场景中,通常采用突发模式(burst-mode),例如无源光网络(PON)。显然,突发模式对 SerDes 的锁定时间提出了严苛要求。

连续模式协议(如 SONET/SDH)要求 CDR 能够容忍较长的连 0 序列,同时对 CDR 的抖动传输性能具有严格要求(源于环路定时,loop timing 机制)。

若接收端(Rx)与发送端(Tx)采用异步模式(asynchronous mode),或应用于频谱扩展(SSC)场景,则要求 CDR 具备较宽的相位跟踪范围,以补偿 Rx 与 Tx 之间的频率偏差。

根据应用场景的不同需求,CDR 存在多种实现架构。FPGA 中的 SerDes 常采用两种 CDR 架构:基于数字锁相环(DPLL)的 CDR 与基于相位插值器的 CDR。这两种架构在环路中采用数字滤波器,相比基于模拟电荷泵与模拟滤波器的结构,具有更高的面积利用率。

图 2.13 展示了基于相位插值器的 CDR 结构。鉴相器阵列对输入的串行数据与 M M M 个等相位间隔的本地时钟进行多 UI 跨度的相位比较,生成多 UI 跨度的相位误差信号。该相位误差信号频率高、带宽宽,经抽取器降速和平滑处理后,送入数字滤波器。数字滤波器的性能直接影响环路的带宽、稳定性与响应速度。经数字滤波器平滑后的误差信号驱动相位插值器(phase rotators)调整时钟相位。当环路达到锁定状态时,理论上相位误差为零,此时采用相位偏移 90 度的时钟作为恢复时钟对串行输入信号进行采样。

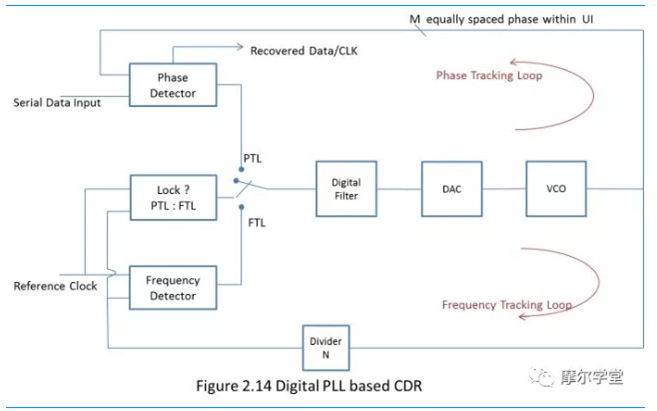

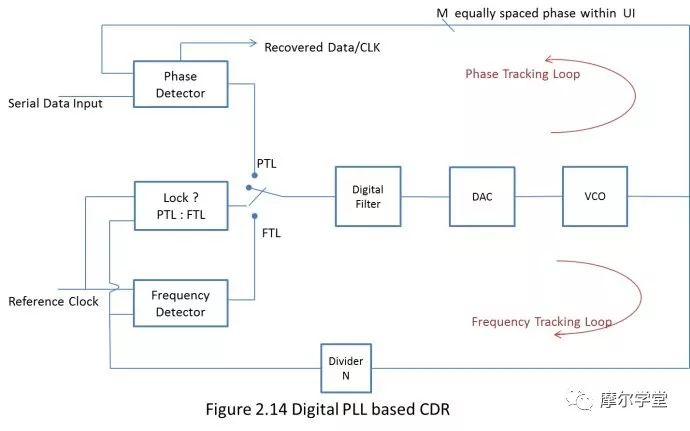

图 2.14 展示了基于 DPLL 的 CDR 结构,该结构包含两个环路:数据锁相环路(phase tracking loop)与频率跟踪环路(Frequency Tracking Loop)。其中数据锁相环路的工作原理与图 2.13 所示 CDR 类似,鉴相器阵列对输入的串行数据与 M M M 个等相位间隔的本地时钟进行相位比较(也可在多 UI 跨度上进行),生成相位误差信号并送入数字滤波器。数字滤波器的性能影响环路的带宽、稳定性与响应速度,经滤波后的误差信号驱动压控振荡器(VCO)调整时钟相位。当环路锁定时,理论上相位误差为零,采用相位偏移 90 度的时钟作为恢复时钟采样串行输入信号。

基于 DPLL 的 CDR 额外配置了频率跟踪环路,该环路的作用是缩短 CDR 的锁定时间,降低对环路滤波器的设计约束。系统工作时,首先由频率跟踪环路完成锁定,随后切换至数据相位跟踪环路;当相位跟踪环路失锁时,系统会自动切换回频率跟踪环路。参考时钟(Reference Clock)频率的 N N N 倍与线路速率接近相等,因此两个环路中 VCO 的稳态控制电压基本一致。借助频率跟踪环路,相位跟踪环路的捕获时间得以有效缩短。

当相位跟踪环路处于锁定状态时,频率跟踪环路不会对其产生影响。因此 SerDes 接收端对参考时钟的抖动无严格要求。

基于相位插值器的 CDR,其参考时钟可采用收发端共享的 PLL,也可采用每个通道独立的 PLL。该结构的缺点在于,参考时钟的抖动会直接影响恢复时钟的抖动,进而影响接收端的误码率。

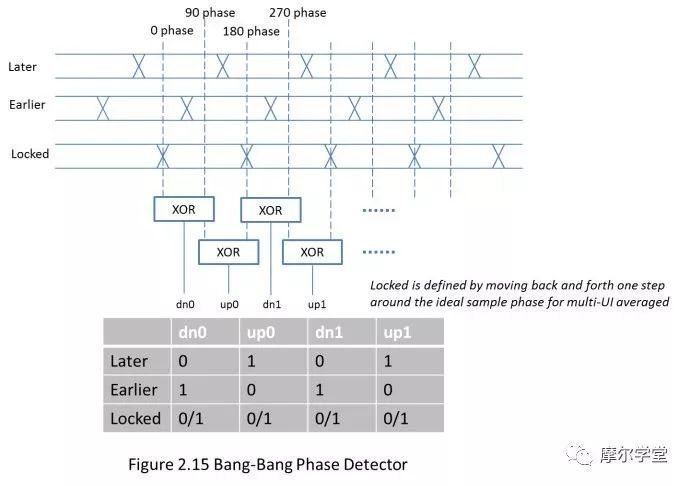

#### 鉴相器 (PD)

鉴相器的功能是比较输入信号与本地时钟的相位误差,相位误差通常以上升(UP)或下降(DN)信号的形式输出,UP/DN 信号的持续时间与相位误差的大小成正比。图 2.15 展示了一个 bang-bang 结构鉴相器的实例,该实例中采用了四个不同相位的恢复时钟进行演示。

#### 抽取器和滤波器

抽取器的作用是降低滤波器的工作频率,抽取步长与平滑方式均会影响环路性能。数字滤波器由比例分支(Proportion)与积分分支(Integral)构成,分别用于跟踪相位误差与频率误差。此外,数字滤波器的处理延时不宜过大,若延时过长,环路将无法跟踪相位与频率的快速变化,从而导致误码。

CDR 的实现架构不限于上述两种,还存在多种变体结构,其本质均为锁相环路。环路的跟随性能、稳定性(STABILITY)、带宽(bandwidth)/增益(gain)性能分析属于学术研究范畴,可通过小信号线性模型进行量化分析,相关理论在大量专业书籍与文献中均有详细阐述。CDR 环路的特性总结如下:

#### 环路带宽

1. 频率低于环路带宽的相位抖动会通过 CDR 传递至恢复时钟。换言之,该频段的抖动可被 CDR 跟踪,不会引发误码;而频率高于环路带宽的抖动分量,其是否引发误码取决于抖动幅度的大小。

2. 环路带宽越大,锁定时间越短,但恢复时钟的抖动也越大;反之,环路带宽越小,锁定时间越长,恢复时钟的抖动也越小。对于 CDR 而言,通常希望环路带宽尽可能大,以提升抖动容忍能力;但对于 SONET/SDH 等采用环路定时(loop timing)的应用场景,恢复时钟的抖动存在严格限制,因此环路带宽不能过大。

3. 开关电源的开关频率通常低于环路带宽,其产生的抖动可被 CDR 跟踪。但需注意两点:一是开关电源耦合至 VCO(数模多相转换器,Digital to Multi-Phase Convertor)的噪声无法被环路跟踪,尤其是低成本环形 VCO(Ring VCO)对电源噪声尤为敏感;二是开关电源的谐波频率可能超出环路带宽范围。

部分协议(如 SDH/SONET)制定了 CDR 增益模板,要实现对这些协议的兼容,需对输入与输出抖动预算进行精确计算。

### 2.5 公用锁相环 (PLL)

SerDes 需要工作在数据波特率或 1/2 数据波特率下的内部时钟,该时钟通常工作在 DDR 模式。由于片外提供的参考时钟频率远低于数据波特率,因此需要通过 PLL 倍频生成内部高频时钟。FPGA 中的 SerDes PLL 通常支持 8x、16x、10x、20x、40x 等倍频模式,以适配常见的 SerDes 接口协议。例如,PCI Express 接口工作在 5 Gbps 速率时,若采用 40x 倍频模式,则需要片外提供 125 MHz 的参考时钟;若采用 20x 倍频模式,则需要片外提供 250 MHz 的参考时钟。

图 2.17 展示了三阶 PLL 的电路结构,鉴相器对输入信号相位与 VCO 反馈信号相位进行比较,相位误差经电荷泵转换为电压或电流信号,该信号经过环路滤波器(Loop Filter)平滑处理后生成控制电压,用于调整 VCO 的输出相位,最终使环路相位误差趋于零。

*Figure 2.17 A 3-order Type II PLL*

PLL 的工作过程分为捕获过程与跟踪过程。在捕获过程中,环路模型可通过非线性微分方程描述,据此可评估捕获时间、捕获带宽等指标。当环路进入锁定状态后,在小信号范围内,PLL 模型可简化为常系数线性方程,此时可在拉普拉斯变换域分析 PLL 的带宽、增益、稳定性等性能,图 2.18 展示了其小信号数学模型。

PLL 的阶数由其传输函数极点(分母的根)的个数决定。由于 VCO 对相位具有积分作用(传输函数为 K vco / s K_{\\text{vco}}/s Kvco/s),因此未配置滤波器的环路称为一阶环,配置一阶滤波器的环路称为二阶环。一阶环与二阶环均属于无条件稳定系统。高阶环路则可通过调整更多的极点与零点,实现对带宽、增益、稳定性、捕获带宽、捕获时间等性能的独立调控。

PLL 的频域传输特性主要由环路滤波器 F ( s ) ∣ s = j ω F(s)\|_{s=j\\omega} F(s)∣s=jω 决定,图 2.19 展示了通用 PLL 的频域传输曲线。该曲线存在两个关键特征:环路带宽与抖动峰值(jitter peaking)。抖动峰值过大会导致抖动放大,增大阻尼系数(damping factor)可抑制抖动峰值,但会延长环路的捕获时间,同时影响滚降速度与固有频率(natural frequency)。

#### PLL 锁定后的特性

1. 环路锁定后,输入信号与反馈信号之间存在固定相位差:

K dc K_{\\text{dc}} Kdc 为环路的直流开环增益, Δ ω \\Delta\\omega Δω 为 VCO 中心频率与受控频率的差值。对于电荷泵 + 无源滤波器结构的 PLL,其相位误差为零。

2. 环路锁定后,输入信号与反馈信号的频率相等,满足以下关系:

f r M = f o N \\frac{f_r}{M}=\\frac{f_o}{N} Mfr=Nfo

3. 对于输入端的噪声,环路表现为低通滤波器特性,可抑制频率高于环路截止频率的噪声或干扰。对于 SerDes 专用 PLL,通常希望其带宽尽可能小,以有效抑制参考时钟引入的干扰与噪声。

4. 对于 VCO 产生的噪声,环路表现为高通滤波器特性,仅能抑制频率低于环路截止频率的 VCO 噪声。VCO 的高频噪声过大会恶化输出时钟的抖动性能。低速 SerDes(\< 5 Gbps)为降低成本,通常采用环形 VCO(Ring VCO),该类型 VCO 噪声较大且对电源噪声敏感;高速 SerDes 则多采用噪声较低的 LC 结构 VCO。

### 3 抖动和信号完整性 (Jitter, SI)

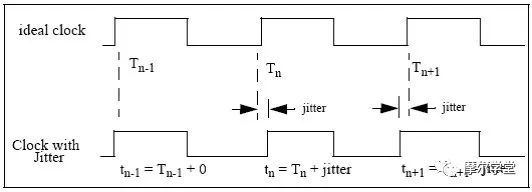

抖动是指信号跳变沿的实际时刻偏离理想(ideal)或预期(expected)时刻的现象。噪声、非理想信道与非理想电路均是产生抖动的原因。

#### 3.1 时钟的抖动 (clock jitter)

*Figure 3.1 Clock Jitter*

针对时钟信号,不同应用场景对抖动的定义存在差异。例如,数字逻辑设计中计算时序余量时,主要关注周期抖动;而时钟设计人员更倾向于使用相位抖动,因为相位抖动可通过频谱分析进行评估,且能量化特定干扰源对总相位抖动的贡献。

结合图 3.1,对几种常见的抖动定义进行说明:

##### 相位抖动 (phase jitter)

J phase ( n ) = t n − n × T J_{\\text{phase}}(n)=t_n-n\\times T Jphase(n)=tn−n×T

理想时钟的周期 T T T 恒定且无抖动,实际时钟跳变沿相对于理想时钟的偏移量即为相位抖动。

##### 周期抖动 (period jitter)

J period ( n ) = ( t n − t n − 1 ) − T J_{\\text{period}}(n)=(t_n-t_{n-1})-T Jperiod(n)=(tn−tn−1)−T

周期抖动是指实际时钟周期相对于理想周期的偏移量(deviation)。由定义可知,周期抖动与相位抖动的关系为:

J period ( n ) = J phase ( n ) − J phase ( n − 1 ) J_{\\text{period}}(n)=J_{\\text{phase}}(n)-J_{\\text{phase}}(n-1) Jperiod(n)=Jphase(n)−Jphase(n−1)

##### 周期间抖动 (Cycle-to-Cycle jitter)

J cycle ( n ) = ( t n − t n − 1 ) − ( t n − 1 − t n − 2 ) J_{\\text{cycle}}(n)=(t_n-t_{n-1})-(t_{n-1}-t_{n-2}) Jcycle(n)=(tn−tn−1)−(tn−1−tn−2)

周期间抖动是指相邻两个时钟周期的差值。由定义可知,周期间抖动与周期抖动的关系为:

J cycle ( n ) = J period ( n ) − J period ( n − 1 ) J_{\\text{cycle}}(n)=J_{\\text{period}}(n)-J_{\\text{period}}(n-1) Jcycle(n)=Jperiod(n)−Jperiod(n−1)

假设相位抖动的最大值为 ± J p \\pm J_p ±Jp,且抖动频率 f jitter = 0.5 f clock = 0.5 / T f_{\\text{jitter}}=0.5f_{\\text{clock}}=0.5/T fjitter=0.5fclock=0.5/T,即满足以下条件:

* t n − 2 t_{n-2} tn−2 时刻的相位抖动为最大值 + J p +J_p +Jp

* t n − 1 t_{n-1} tn−1 时刻的相位抖动为最小值 − J p -J_p −Jp

* t n t_n tn 时刻的相位抖动为最大值 + J p +J_p +Jp

* t n + 1 t_{n+1} tn+1 时刻的相位抖动为最小值 − J p -J_p −Jp

根据上述条件可计算得出:

* 周期抖动的最大值为 J period = ± 2 J p J_{\\text{period}}=\\pm 2J_p Jperiod=±2Jp

* 周期间抖动的最大值为 J cycle = ± 4 J p J_{\\text{cycle}}=\\pm 4J_p Jcycle=±4Jp

#### 3.2 数据的抖动 (data jitter)

在高速 SerDes 领域,抖动是核心研究内容之一,因为抖动与误码率(BER)直接相关。

SerDes 发送端的一项关键指标为抖动生成(jitter generation)------在特定码型(pattern)、速率与负载条件下,发送端产生的抖动幅度。

信号经过信道(channel)传输至接收端后,抖动会进一步被放大。不同码型包含的频率成分存在差异,而信道对不同频率成分的传输延时不同(非线性相位特性),由此产生与数据码型相关的确定性抖动。此外,阻抗不连续导致的信号反射、相邻信号的串扰以及噪声等因素,均会引发数据抖动。

SerDes 接收端的一项关键指标为抖动容忍能力(Jitter Tolerance)------在特定码型与误码率要求( B E R \< 10 − 12 BER\<10\^{-12} BER\<10−12)下,接收端能够容忍的最大抖动幅度。对抖动进行评估时,常用的分析手段包括眼图(eye-diagram)、浴缸曲线(bath curve)、抖动分布直方图(PDF)、抖动频谱(jitter spectrum)等。

需要说明的是,在讨论高速 SerDes 的数据抖动(如 T j T_j Tj、 R j R_j Rj、 D j D_j Dj 等参数)时,通常不包含低频抖动。这是因为低频抖动被视为漂移(wander),可被 CDR 跟踪,不会导致误码。使用示波器(SDA)测量数据抖动时,可通过设置示波器内嵌 CDR 的环路带宽,滤除低频抖动分量。

根据抖动的产生原因与概率密度函数,可将抖动划分为不同类型。对抖动进行分类的意义在于,部分类型的抖动可通过技术手段校正,而其他类型则无法校正。经典分类方法将总抖动 T j T_j Tj(Total Jitter)划分为确定性抖动 D j D_j Dj(deterministic jitter)与随机抖动 R j R_j Rj(random jitter)。抖动的计量单位为 UI 或 ps,其数值可表示为均方根值或峰峰值。

##### 3.2.1 确定性抖动 D j D_j Dj

确定性抖动 D j D_j Dj 可进一步细分为以下类型:

1. **占空比失真抖动(DCD,Duty Cycle Distortion)**

该类抖动由差分信号正负端的偏置电压不一致,或信号上升沿与下降沿的时间不一致导致。由于 DCD 与数据码型相关,因此可通过技术手段校正。

2. **数据相关抖动(DDJ,Data Dependent Jitter)**

该类抖动也称为码间干扰(ISI,Intersymbol Interference),由信道的非理想特性导致。DDJ 可通过均衡器进行校正。

3. **周期性抖动(Pj,Periodic Jitter)**

该类抖动由电路中的周期性干扰源产生,例如开关电源的开关频率、时钟信号的串扰等。尽管开关电源的开关频率通常处于 CDR 的跟踪范围内,但其低次谐波可能超出环路带宽或落入抖动峰值区域;更重要的是,电源谐波对 CDR 内部 VCO 的干扰无法被环路抑制和跟踪。因此,对于采用环形 VCO 的 CDR,应尽量使用低压差稳压器(LDO)供电。Pj 无法通过均衡器校正。

4. **有界非相关抖动(BUJ,Bounded Uncorrelated Jitter)**

该类抖动由非时钟干扰源引发。若干扰源(aggressor)与被干扰源(victim)为异步关系,则抖动的概率分布为有界高斯分布,此时也称为相关有界高斯抖动(CBGJ,Correlated Bounded Gaussian Jitter)。BUJ/CBGJ 无法通过技术手段校正。

##### 3.2.2 随机抖动 R j R_j Rj

随机抖动 R j R_j Rj 由半导体器件本身的噪声引起,其显著特征是概率密度函数呈高斯分布,无固定边界,且与数据码型无关。仅在特定误码率约束条件下,才可将其视为有界抖动。

##### 3.2.3 总抖动 T j T_j Tj

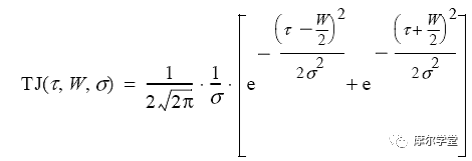

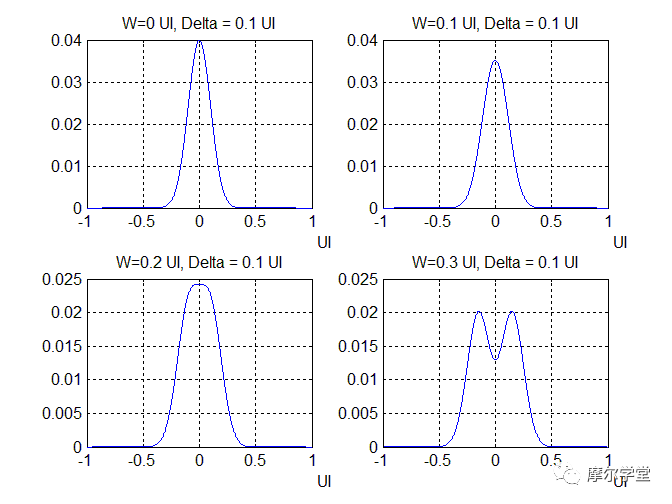

从数学角度分析,抖动的概率分布函数可近似为高斯分布与双狄拉克分布的卷积。

对高斯分布产生贡献的抖动类型包括:

* 随机抖动 R j R_j Rj 本身呈高斯分布

* 多个周期性抖动 P j Pj Pj 叠加后的效果近似高斯分布

* 部分有界非相关抖动 B U J BUJ BUJ 呈高斯分布

对双狄拉克分布产生贡献的抖动类型包括:

* 占空比失真抖动 D C D DCD DCD 的概率分布近似双狄拉克分布

高斯分布与双狄拉克分布的卷积公式如下:

式中, W W W 为确定性抖动的峰峰值, δ \\delta δ 为高斯分布的均方差。如图 3.2 所示,随着确定性抖动 W W W 的增大,概率密度分布曲线的顶部呈现双峰特征。通常,曲线的顶部形状反映了确定性抖动的幅度大小。

*Figure 3.2 PDF of Tj with different Dj and Rj*

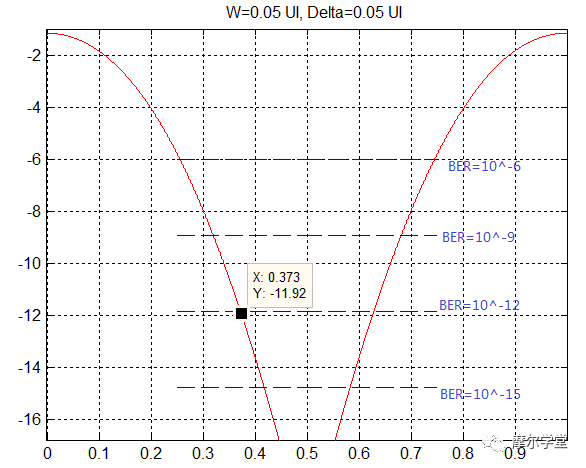

将一个 UI 内两个跳变沿处(0 UI 与 1 UI 位置)的概率分布函数绘制在同一张图中,即可得到抖动的浴缸曲线(bathtub curve)。由于对数坐标具有宽动态范围特性,浴缸曲线的 Y 轴通常采用对数刻度。图 3.3 展示了确定性抖动峰峰值 W = 0.05 UI W=0.05\\ \\text{UI} W=0.05 UI、高斯抖动均方差 δ = 0.05 UI \\delta=0.05\\ \\text{UI} δ=0.05 UI 时对应的浴缸曲线。

*Figure 3.3 Bathtub Curve of Tj with 0.05 Dj peak and 0.05 Rj RMS*

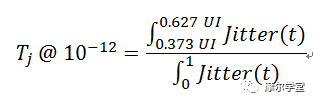

浴缸曲线通常会标注对应的误码率(BER)坐标,例如图中 B E R = 10 − 12 BER=10\^{-12} BER=10−12 对应的总抖动峰峰值为 T j ( p-p ) = 0.373 × 2 = 0.746 UI T_j(\\text{p-p})=0.373\\times2=0.746\\ \\text{UI} Tj(p-p)=0.373×2=0.746 UI。曲线下方的面积占总面积的比例即为误码率,其计算公式如下:

浴缸曲线的顶部主要由确定性抖动 D j D_j Dj 贡献,越靠近曲线底部,高斯抖动的贡献越大,且以高斯曲线的斜率衰减。基于此特性,可利用高斯分布的统计特征对抖动进行估算。下表列出了高斯分布中概率与均方差的对应关系:

在指定误码率条件下,可通过该表快速估算均方差与峰峰值的关系。例如,当高斯抖动的均方根值为 0.05 UI 0.05\\ \\text{UI} 0.05 UI、误码率要求为 10 − 12 10\^{-12} 10−12 时,查表可得 Q = 7 Q=7 Q=7,因此高斯抖动的峰峰值为:

0.05 UI × 7 × 2 = 0.7 UI 0.05\\ \\text{UI}\\times7\\times2=0.7\\ \\text{UI} 0.05 UI×7×2=0.7 UI

前文所述的例子中, W = 0.05 UI W=0.05\\ \\text{UI} W=0.05 UI、 R j = 0.05 UI R_j=0.05\\ \\text{UI} Rj=0.05 UI 时,计算得到的总抖动 T j = 0.746 UI T_j=0.746\\ \\text{UI} Tj=0.746 UI;利用高斯分布特性估算的高斯抖动峰峰值为 0.7 UI 0.7\\ \\text{UI} 0.7 UI。若按 T j = R j ( 0.7 UI ) + D j ( 0.05 UI ) T_j=R_j(0.7\\ \\text{UI})+D_j(0.05\\ \\text{UI}) Tj=Rj(0.7 UI)+Dj(0.05 UI) 计算,可得 T j = 0.75 UI T_j=0.75\\ \\text{UI} Tj=0.75 UI,与理论计算值基本一致,差异源于绘图程序的量化误差。

### 4 信号完整性 (SI)

信号完整性(SI)的定义为:信号在传输过程中保持其原有特性的能力。信号的奈奎斯特频率为其线速率的一半,即信号的奈奎斯特频率等于线速率。信道对信号的损伤主要包括插入损耗(insertion loss)、反射(reflection)、串扰(crosstalk)等,这些损伤可通过 S 参数信道模型进行描述。S 参数可通过矢量网络分析仪(Vector Network Analyzer)测量获得。信道并非纯阻性网络,而是包含容性与感性元件,这导致信道对不同频率成分的传输延时存在差异,从而产生与数据码型相关的抖动。

信道中任何阻抗不连续的位置都会产生信号反射,根据反射点位置的不同,反射信号会以不同相位叠加在原始信号上,导致信号幅度增大或减小。

SerDes 采用差分信号传输,对共模干扰具有较强的抑制能力。若差分信号正负端受到的干扰存在差异,则会引入串扰。在 PCB 设计中,通常可保证 SerDes 数据线与干扰源之间的距离,但在芯片内部,出于成本考虑,难以实现 SerDes 信号与干扰源的充分隔离,尤其是同一通道的发送信号对接收信号的干扰问题。

#### 4.2 芯片封装 (Package)

芯片封装(Package)是信道的重要组成部分。芯片外部信道的 S 参数可通过矢量网络分析仪(VNA)测量获得,而封装的 S 参数通常由芯片制造商提供。在进行仿真分析时,可将封装与外部信道的 S 参数级联使用。由于封装的物理尺寸较小,其插入损耗通常不是主要问题,设计的重点在于实现阻抗匹配。

#### 4.3 SI 仿真

信号完整性(SI)仿真可通过以下方式搭建仿真平台:将 SerDes 发送端的 SPICE 模型、封装与信道的 S 参数模型、接收端的 SPICE 模型进行级联,利用仿真工具对不同激励信号在不同测试条件下进行电路仿真。通过分析 SerDes 接收端的眼图,可评估系统是否满足设计需求;也可通过实测接收端眼图,验证其是否符合接收端眼图模板或协议规定的眼图模板要求。图 4.1 展示了 3.125 Gbps 信号的实测眼图与模板,同时包含浴缸曲线与统计直方图。

*Figure 4.1 Rx-end Eye-diagram of A 3.125Gbps SerDes*(此处原文缺图)

对于高速 SerDes(\> 5 Gbps),传统的电路仿真方法已无法满足设计需求。原因主要有两点:第一,严重的码间干扰(ISI)会导致接收端眼图完全闭合,但经过芯片内部 DFE 均衡处理后,眼图可恢复至清晰状态;第二,电路仿真(SPICE)的速度较慢,即使将 DFE 均衡算法纳入仿真流程,由于 DFE 训练需要大量的比特数据,仿真时间会变得难以接受。

针对高速 SerDes 的仿真需求,可采用统计分析(statistical analysis)方法。该方法将发送端-信道-接收端的链路近似为线性系统,计算系统的脉冲响应 h ( t ) h(t) h(t),并加入噪声源模拟抖动,随后通过激励信号与脉冲响应的卷积运算,得到接收端的信号。该方法可将厂商的私有 FFE、DFE 自适应算法纳入仿真流程。

需要注意的是,统计分析方法无法仿真电路的非线性与时变特性,因此高速 SerDes 的 SI 仿真通常需要结合电路仿真与统计分析两种方法。关于统计分析方法的更多细节,可参考相关专业文献。

*** ** * ** ***

## via:

* 一文读懂SerDes技术-CSDN博客